今天看了《用于构建多核处理器的crossbar的研究与设计》的论文,主要讲的是crossbar,归纳一下。

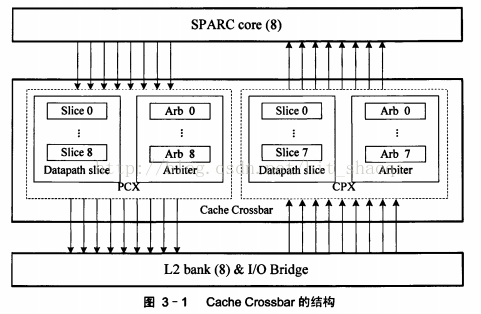

opensparc t2中有8核,每个对应一个L2 cache,核与cache之间有一个仲裁器与数据通路片。

仲裁器与数据通路片一共有8对,仲裁器负责选择哪个cpu可以访问L2cache。数据通路片负责根据仲裁器输出的信号从数据总线上将数据选出来,传递给L2 cache.

需要注意的是,仲裁器分为pcx和cpx。pcx负责处理器到缓存,而cpx负责缓存到处理器。 pcx与cpx除了接口不同外,功能类似。

另外,仲裁器需要支持原子操作,即连续的两个命令访问,不允许被仲裁器从中间断开。

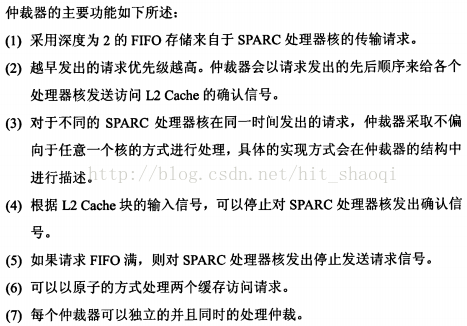

仲裁器:

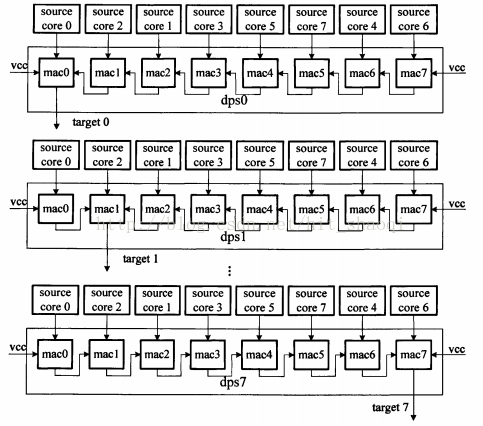

数据通路选择片的结构:

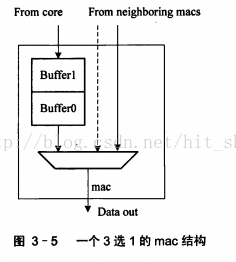

注意其中的每一个mac的结构如下图所示

是一个三输入的mac,接受左边和右边以及自身数据流输入的mac。这样看起来,像一个移位寄存器...具体为什么这么做,暂时还不清楚。

另外,这篇文章没有说如何保证cache的一致性。