目录

简介:

PCIe有很多寄存器,也有很多控制,包括链路状态信息,上一节我们讲到了PCie的链路训练,这节文章将继续学习PCIe相关知识。

目的:

从设计开发流程来说,本文属于上一篇文章的继续,一般来说在开发过程,是否正确识别到PCIe设备,代表上一篇文章已经通过。链路训练包括枚举过程已经完成。

详情:

文章从实际案例出发,逐渐学习更深的知识。

这里面包含了很多信息,

我们来解释以下:

Bus:第一个端口40,第二个端口时41.下游端口时41.

Interrupt:这个表示终端的向量位置。

区域0:IO空间;

区域2:内存空间;

区域4:内存空间;

第一个capabilities:POWER management capability

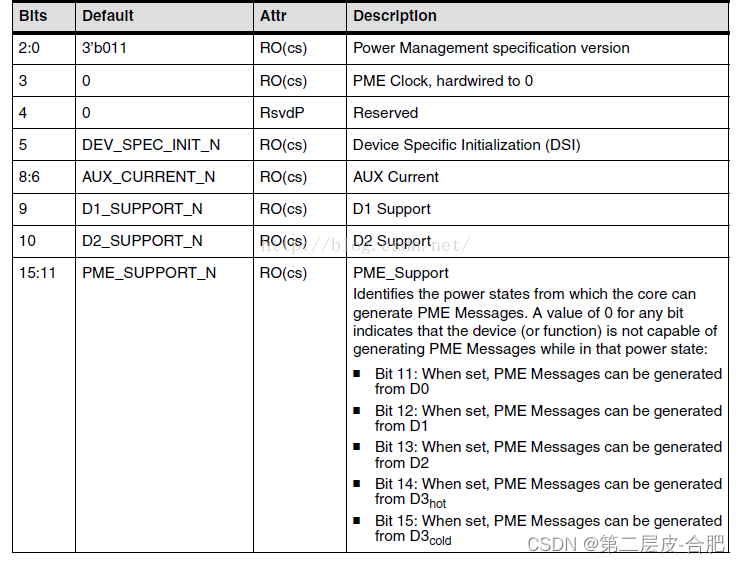

包括PMCR和PMCSR,其结构如下:

:PMCR寄存器由16位组成,都是只读的,该设备的作用时记录下当前设备的属性。

:PMCR寄存器由16位组成,都是只读的,该设备的作用时记录下当前设备的属性。

在本文:可以看到PMECLK,DSI都不使能,D1和D2使能,电流375mA;

MSI capabiliyies :MSI中断使能,中断数一个,maskable不使能,64bit;

地址: 数据:

下面时链路的具体capabilities:

显示当前端口属于EP,PCIE2.0 ,msi01(中断机制需要的消息字段)

Devcap:该字段2:0主要存放 max_payload_size support.该字段主要放置设备支持的max_payload_size support参数的大小。只读。该字段决定一个TLP包最大有效负载,协议位4096B。该字段仅表示设备支持的最大有效负载。在devctl中,还有个max_payload_size, 这个由软件设置,表示实际值。值得注意的是。在PCIe设备中,max_payload_size_support 和max_payload_size不一定相同,前一个是设备所能支持的最大值,后一个是两者协商的结果。