明天继续搞一下cache,还有后面的,

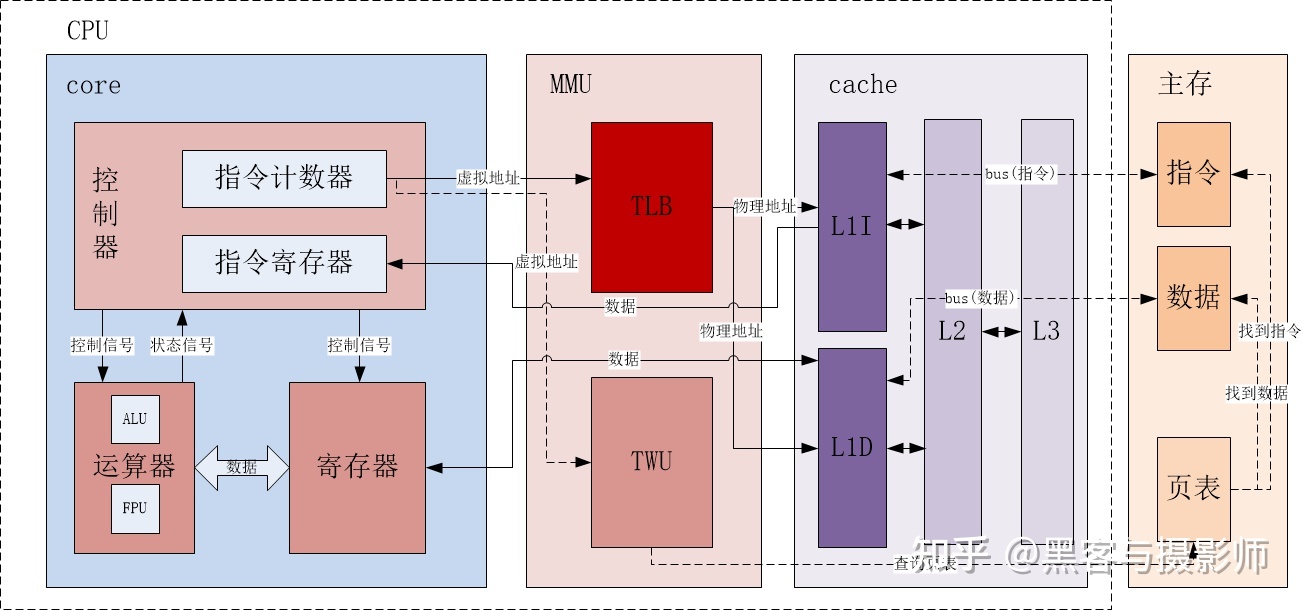

下面是cpu框架图

开始解释cpu

1.控制器

控制器又称为控制单元(Control Unit,简称CU),下面是控制器的组成

1.指令寄存器IR:是用来存放当前正在执行的的一条指令。当一条指令需要被执行时,先按照程序计数器PC所指出的指令地址,从cache中取出一条指令到指令寄存器IR。

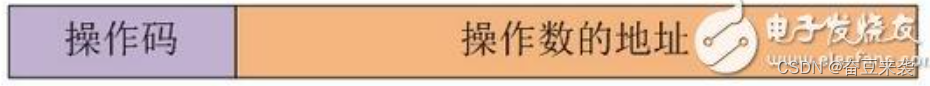

操作码就是汇编语言里的mov,add,jmp等符号码;操作数地址说明该指令需要的操作数在数据缓存cache中的地址。

2.指令译码器ID:指令寄存器中的指令经过译码,决定该指令应进行何种操作(就是指令里的操作码)、操作数在哪里(操作数的地址)。

3.时序产生器TG: 类似于“时间作息表”,给计算机各部分提供工作所需的时间标志,一般是利用定时脉冲的顺序和不同的脉冲间隔来实现。

4.操作控制器CU: 根据指令所需完成的操作和信号,发出各种微操作命令序列,用以控制所有被控对象,完成指令的执行。

5.程序计数器PC: 用来存放下一条要执行指令的地址,它与存储器(内存)之间有一条直接通路。执行指令时,首先需要根据程序计数器PC中存放的指令地址,将指令由内存取到指令寄存器IR,完成“取指令”的操作。程序计数器PC本身具有自动加1的功能,可以自动给出下一条指令的地址,如此循环,执行每一条指令。

2.运算器

运算器,一般最少包括3个寄存器和1个算术逻辑单元(ALU),现代计算机内部往往设有通用寄存器组。

寄存器,一种有限存储容量的高速存储部件,可用来暂存指令、数据和位址。寄存器有很多种类,一般涉及到四则运算的有3类,ACC(Accumulator)为累加器,MQ(Multiplier-Quotient Register)为乘商寄存器,X为操作数寄存器,3类寄存器在完成不同运算时,所存放的操作数类别也各不相同。

关于乘积高位和乘积低位的概念,以十进制为例,百位就是十位的高位,十位是百位的低位。两个16位数相乘,结果可能会有32位,那左半部分的16位就是乘积高位,存储到ACC中,右半部分的16位就是乘积低位,存储到MQ中。

算术逻辑单元(ALU,Arithmetic and Logic Unit),是算术运算和逻辑运算的部件。算术运算包括加、减、乘的整数运算,逻辑运算是与、或、非和异或等逻辑操作,还有移位、比较和传送等操作。

移位运算,将一个字符向左或向右移动位,或是浮动特定位,包含带符号延伸和无符号延伸,在程序中应用很广泛。

3.寄存器

在CPU中至少要有六类寄存器:指令寄存器(IR)、程序计数器(PC)、地址寄存器(AR)、数据寄存器(DR)、累加寄存器(AC)、程序状态字寄存器(PSW)。

这些寄存器用来储存少量数据,以供cpu能快速使用.

-

数据寄存器

数据寄存器(Data Register,DR)又称数据缓冲寄存器,其主要功能是作为CPU和主存、外设之间信息传输的中转站,用以弥补CPU和主存、外设之间操作速度上的差异。

数据寄存器用来暂时存放由主存储器读出的一条指令或一个数据字;反之,当向主存存入一条指令或一个数据字时,也将它们暂时存放在数据寄存器中。

数据寄存器的作用是 :

(1)作为CPU和主存、外围设备之间信息传送的中转站;

(2)弥补CPU和主存、外围设备之间在操作速度上的差异;

(3)在单累加器结构的运算器中,数据寄存器还可兼作操作数寄存器。 -

指令寄存器

指令寄存器(Instruction Register,IR)用来保存当前正在执行的一条指令。

当执行一条指令时,首先把该指令从主存读取到数据寄存器中,然后再传送至指令寄存器。

指令包括操作码和地址码两个字段,为了执行指令,必须对操作码进行测试,识别出所要求的操作,指令译码器(Instruction Decoder,ID)就是完成这项工作的。指令译码器对指令寄存器的操作码部分进行译码,以产生指令所要求操作的控制电位,并将其送到微操作控制线路上,在时序部件定时信号的作用下,产生具体的操作控制信号。

指令寄存器中操作码字段的输出就是指令译码器的输入。操作码一经译码,即可向操作控制器发出具体操作的特定信号。 -

程序计数器

程序计数器(Program Counter,PC)用来指出下一条指令在主存储器中的地址。

在程序执行之前,首先必须将程序的首地址,即程序第一条指令所在主存单元的地址送入PC,因此PC的内容即是从主存提取的第一条指令的地址。

当执行指令时,CPU能自动递增PC的内容,使其始终保存将要执行的下一条指令的主存地址,为取下一条指令做好准备。若为单字长指令,则(PC)+1àPC,若为双字长指令,则(PC)+2àPC,以此类推。

但是,当遇到转移指令时,下一条指令的地址将由转移指令的地址码字段来指定,而不是像通常的那样通过顺序递增PC的内容来取得。

因此,程序计数器的结构应当是具有寄存信息和计数两种功能的结构。 -

地址寄存器

地址寄存器(Address Register,AR)用来保存CPU当前所访问的主存单元的地址。

由于在主存和CPU之间存在操作速度上的差异,所以必须使用地址寄存器来暂时保存主存的地址信息,直到主存的存取操作完成为止。

当CPU和主存进行信息交换,即CPU向主存存入数据/指令或者从主存读出数据/指令时,都要使用地址寄存器和数据寄存器。

如果我们把外围设备与主存单元进行统一编址,那么,当CPU和外围设备交换信息时,我们同样要使用地址寄存器和数据寄存器。 -

累加寄存器

累加寄存器通常简称累加器(Accumulator,AC),是一个通用寄存器。

累加器的功能是:当运算器的算术逻辑单元ALU执行算术或逻辑运算时,为ALU提供一个工作区,可以为ALU暂时保存一个操作数或运算结果。

显然,运算器中至少要有一个累加寄存器。 -

程序状态字寄存器

程序状态字(Program Status Word,PSW)用来表征当前运算的状态及程序的工作方式。

程序状态字寄存器用来保存由算术/逻辑指令运行或测试的结果所建立起来的各种条件码内容,如运算结果进/借位标志(C)、运算结果溢出标志(O)、运算结果为零标志(Z)、运算结果为负标志(N)、运算结果符号标志(S)等,这些标志位通常用1位触发器来保存。

除此之外,程序状态字寄存器还用来保存中断和系统工作状态等信息,以便CPU和系统及时了解机器运行状态和程序运行状态。

因此,程序状态字寄存器是一个保存各种状态条件标志的寄存器。

下面是cpu和主存框架图

4.MMU

属于cpu

mmu的作用是进行虚拟地址和物理地址的相互转换.

虚拟地址和物理地址的关系记录在页表里,页表存在内存中.

TLB是一个高速缓存,用于缓存页表转换的结果,从而减少页表查询的时间.

如果TLB中没有命中,那么就用TWU去内存中遍历查询页表,得到物理地址或虚拟地址,并记录在TLB中.

5.cache

属于cpu

首先说明,cache被称为高速缓存,为什么有cache,是因为虽然内存存取数据速度很快,但是和cpu相比还是太慢了,cache比内存快上百倍,存取速度和cpu相当, 所以先把内存的数据提前加载到cache里,做个缓存,以供cpu使用.

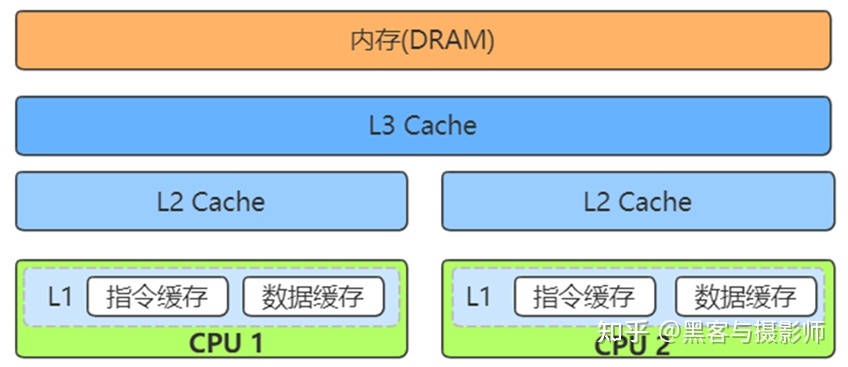

cache分为L3 cache /L2 cache / L1 cache, L1 cache又分为指令缓存cache和数据缓存cache

L1和L2 cache在同一个cpu上,L3 cache一般是多个cpu间共享

下图为计算机的所有储存数据的类型

1.寄存 2.缓存 3.内存 4.硬盘

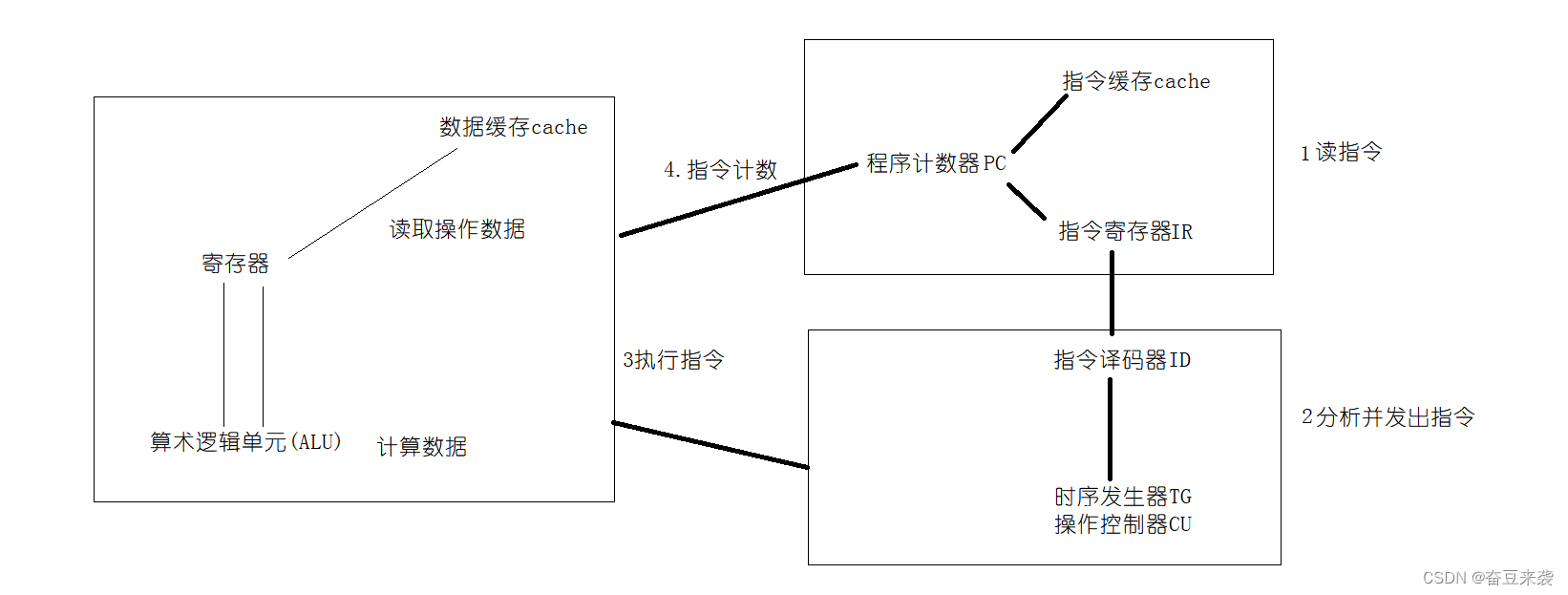

二.CPU的运行过程

cpu的运行过程

1.取指令

cpu读取 程序计数器 所指的在 指令cache 中的一条指令,将指令读取到到指令寄存器IR.

2.分析并发出指令

指令译码器ID对指令进行分析

操作控制器CU和时序产生器TG根据指令的功能向有关部件发出控制命令,执行控制指令的操作

3.执行指令

执行指令分为两步:取操作数和进行运算。

取操作数:CPU通过寻址操作从 数据缓存cache 中读取操作数到寄存器中,暂时保存起来

进行运算:运算单元通过指令中的操作码,对寄存器中的数进行操作

4.指令计数

修改程序计数器PC,使其指向下一条指令地址. 继续循环以上步骤,直至没有指令.

cpu的三级缓存的大小

一级缓存,容量最小,单位都是KB,不同CPU之间一级缓存没有差距,

二级缓存,基本都是个位数MB,除了一些服务器CPU会有10几MB之外,

三级缓存,常见的CPU的三级缓存只有10MB左右(现在AMD EPYC 的X系列已经达到768MB的三级缓存)。

cpu和io的关系

计算机硬件上使用DMA来访问磁盘等IO,也就是请求发出后,CPU就不再管了,直到DMA处理器完成任务,再通过中断告诉CPU完成了。所以,单独的一个IO时间,对CPU的占用是很少的,阻塞了就更不会占用CPU了,因为程序都不继续运行了,CPU时间交给其它线程和进程了。虽然IO不会占用大量的CPU时间,但是非常频繁的IO还是会非常浪费CPU时间的,所以面对大量IO的任务,有时候是需要算法来合并IO,或者通过cache来缓解IO压力的。