目录

浮点单元

介绍FPU (Floating Point Unit)。

它包含以下部分:

- 关于FPU的信息见8-2。

- FPU功能描述见8-3。

- FPU程序员模型在第8-5页。

8.1关于FPU

Cortex-M7处理器是ARMv7-M架构的单精度和双精度变体,具有浮点扩展(FPv5)。

FPv5扩展功能如下:

- 中现有数据处理指令增加双精度操作数支持FPv4-SP-D16-M.双精度和单精度操作数的一些新指令。

- 16个双精度寄存器。这与FPv4相同,并且没有额外的寄存器。

- 软件使能控制单精度和双精度支持使用CPACR。

- 双精度和单精度支持,当两者都实现时,不能彼此独立地启用。

- 与已经支持64位数据类型的FPv4扩展相同的加载/存储指令支持。

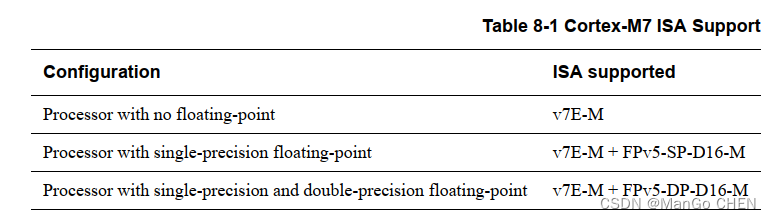

不同配置的Cortex-M7处理器支持的ISA如表8-1所示。

它提供了符合ANSI/IEEE Std 754-2008 (IEEE二进制浮点运算标准,简称IEEE 754标准)的浮点计算功能。

8.2FPU功能描述

介绍FPU支持的操作和产生的异常。

FPU完全支持单精度和双精度加、减、乘、除、乘、累加和平方根运算。

它还提供定点和浮点数据格式之间的转换,以及浮点常量指令。

FPU提供一个包含32个单精度寄存器的扩展寄存器文件。

这些可以看作是:

十六位双字寄存器,D0-D15。

32个32位单字寄存器,S0-S31。

来自这些视图的寄存器的组合。有关FPU的更多信息,请参见《Armv7-M架构参考手册》。

本节内容如下:

操作方式。符合第8-4页的IEEE 754标准。例外情况见第8-4页。操作模式由浮点状态和控制寄存器(FPSCR)控制。有关FPSCR的更多信息,请参阅ARMv7-M架构参考手册。

8.2.1操作方式

FPU提供三种操作模式,以适应各种应用:

- 完全符合模式。

- Flush-to-zero模式。

- 默认NaN模式。

完全符合模式

在full compliance模式下,FPU在硬件上的所有操作都是按照IEEE 754标准进行的。

Flush-to-zero模式

设置FPSCR。FZ位启用刷新到零模式。在这种模式下,FPU将算术运算的所有次正常输入操作数视为运算中的零。由零操作数引起的异常会适当地发出信号。VABS、VNEG和VMOV不被认为是算术运算,也不受刷新到零模式的影响。如果结果很小,如IEEE 754标准中所描述的,即目标精度小于舍入前的最小正常值,则用零替换。FPSCR。IDC位表示输入刷新发生的时间。FPSCR。UFC位表示结果刷新发生的时间。

默认NaN模式

设置FPSCR。DN位开启默认的NaN模式。在这种模式下,任何涉及输入NaN或生成NaN结果的算术数据处理操作的结果都会返回默认NaN。分数比特的传播仅由VABS、VNEG和VMoV操作维持。所有其他算术运算都忽略输入NaN的分数位中的任何信息。

8.2.2符合IEEE 754标准

当默认NaN (DN)和Flush-to-Zero (FZ)模式被禁用时,FPv5功能在硬件上符合IEEE 754标准。不需要任何支持代码来实现这种遵从性。请参阅Armv7-M架构参考手册,了解有关FP架构符合IEEE 754标准的信息。

8.2.3异常

根据FPv5架构,FPU根据每条指令的需要在FPSCR寄存器中设置累积异常状态标志。FPU单板不支持异常trap。处理器还有六个输出引脚:FPIXC、FPUFC、FPOFC、FPDZC、FPIDC和FPIOC,每个引脚反映一个累积异常标志的状态。处理器可以通过使用延迟堆叠来减少异常延迟。这意味着处理器在堆栈上为FP状态保留空间,但直到需要时才将该状态信息保存到堆栈中。有关更多信息,请参阅Armv7-M架构参考手册。

8.3FPU编程器模型

表8-2显示了在Cortex-M7处理器中使用FPU实现的浮点系统寄存器。这些寄存器在Arm*v7-M架构参考手册中有描述。