目录

一、前言

以Makefile启动VCS为例来讲解如何使用命令参数,VCS编译文件会引入过多参数,试想如果我们每次都需要终端中敲击过多参数才能运行一次VCS,那么效率显然是很低的,于是通过脚本语言存储参数从而简化操作指令是必要的,于是Makefile派上了用场。

我们通常会将参数写入到Makefile中,然后通过脚本简化命令成make run_vcs来一步完成VCS的编译连接运行,这称为一步法(首参数是vcs)。

二、VCS的常用命令参数

| 命令参数 | 含义 | 补充 |

| vlogan | 分析verilog文件(如果是分析VHDL文件,类似的指令是vhdlan),编译常用 | 三步法中使用(见下文) |

| vcs | 使用vcs编译文件 | 一步法或两步法中使用(见下文) |

| -sverilog | 编译的文件中含sv语法,编译sv文件必加这一条 | vcs -sverilog tb.sv 编译tb.sv文件 |

| -full64 | 以64位模式编译且创建64位可执行文件可供模拟 | 如果是64位操作系统,则必须添加 |

| -l compile.log | 将编译内容写入到compile.log文件中 | |

| +v2k(-v2k) | 使用Verilog 1364-2001标准 | 广泛使用的标准 |

| -f | 编译覆盖.v文件和包含路径的文件 | vcs -f ram.lst 编译ram的lst文件,在lst文件中可能包含路径比如/home/host/rtl/ram.v |

| -timescale=1ns/1ps | 定义仿真的时间单位为1ns,精度为1ps | 为不包含timescale编译器指令的文件指定时间表,并在包含时间表的文件前先指定时间表 |

| +plusarg_save | 使能传参功能,仿真时可将具体数值传入 | |

| -ntb_opts | 编译的时候加上一些选项 | -ntb_opts uvm1.2表示加载uvm1.2库文件 |

| +incdir+<directory> | 指定包含使用`include 编译器指令指定的文件的目录,可以指定多个目录,用+字符分隔每个路径名称; | |

| -debug_all | 启动所有调试功能,-debug部分调试,-debug_access+<option>(VCS2014版本后新增的debug可选功能) | |

| -nc | 不打印synopsys的版权信息 | 加或不加都不影响仿真 |

| -R | 编译后立即启动仿真 | 一步法中使用 |

| -sim_res | 启用时间分辨率 |

注意:incdir文件的时候,只能包含文件夹下的文件,而不包括下级文件夹的内容(如果要包含下级文件夹的内容,需要写+incdir+uvm/{test,test/basic_test},这样就包括了uvm下test文件中的文件,同时包含了uvm下test下basic_test中的文件)

2.1. 一步法

对设计/验证文件用VCS做编译检查时,可以只用一些简单的VCS指令来实现。以下操作适合不涉及仿真,仅仅检查当前写的文件是否有错时使用。

| 命令 | 结果 |

| vcs +v2k -full64 file1.v file2.v | 编译Verilog文件 |

| vcs +v2k -full64 -sverilog file1.v file2.v file3.sv file4.sv | 编译可包含SV语法的文件 |

| vcs +v2k -full64 -f file1.lst | 编译lst文件,文件中包含路径的文件信息 |

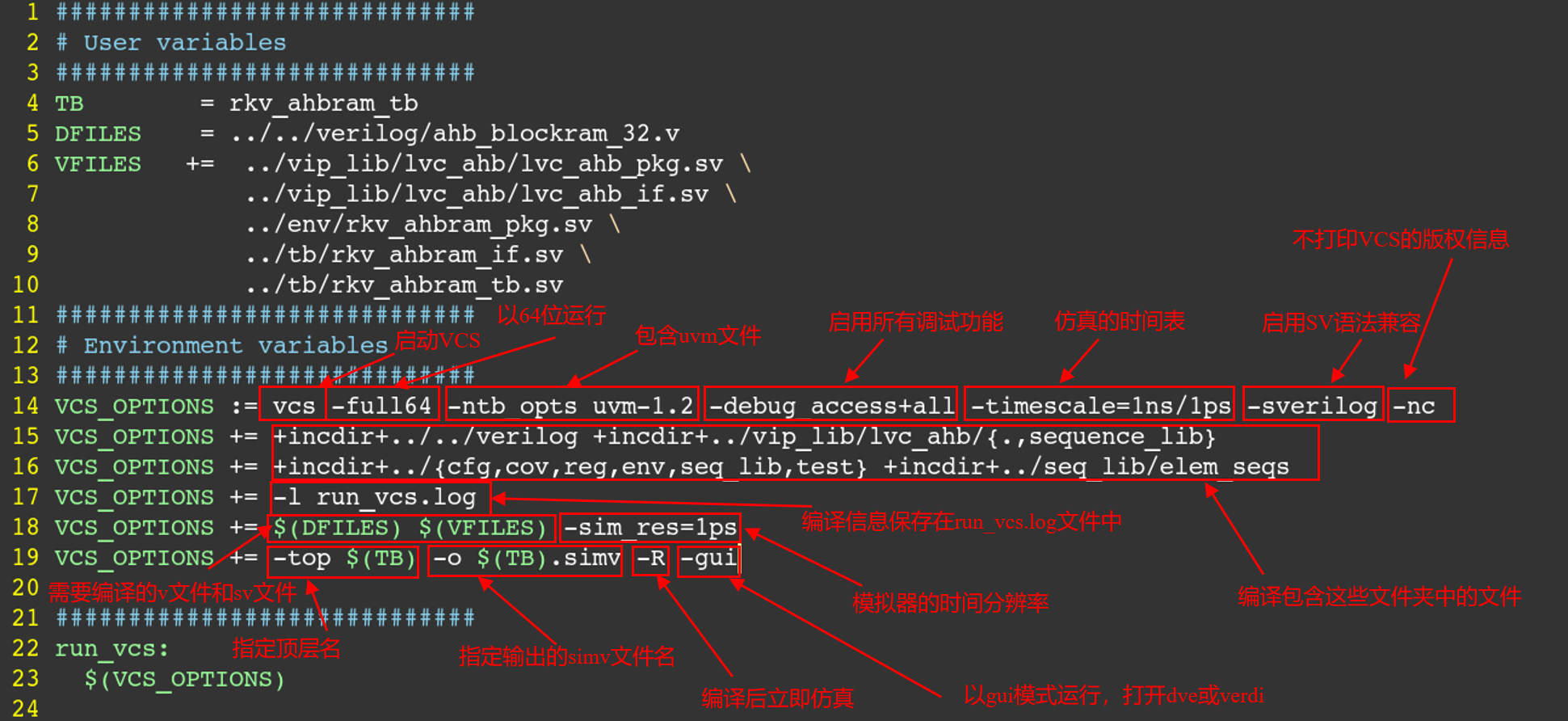

如果在编译后还需要启动仿真(前提:具备验证环境),且文件繁多,且需要添加更多的控制参数,那么需要使用Makefile,以下是一步法的Makefile编写示例

一步法Makefile编写示例:

通过-R选项将编译与仿真操作合并,从而实现一步法

2.2. 两步法

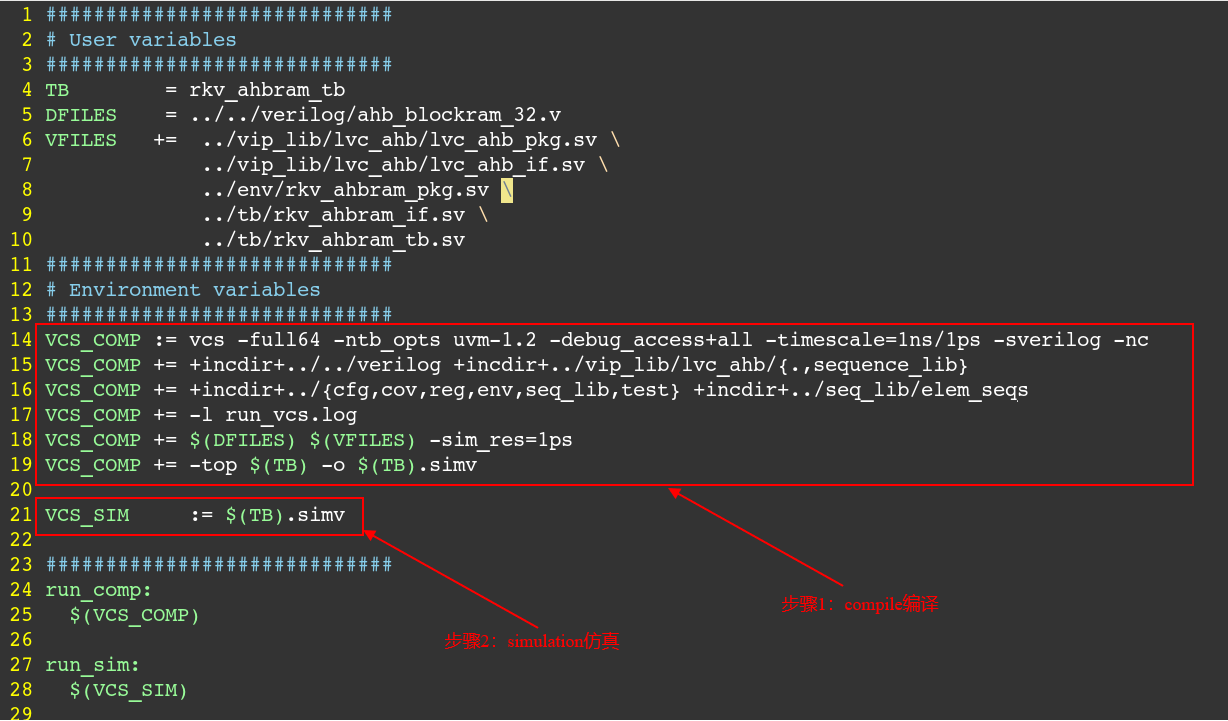

我们有时会将编译与仿真拆分,在编译完成生成simv文件后,再运行仿真执行simv文件,称为两步法。

两步法Makefile编写示例:

与一步法相比,将其拆分成两个步骤,同时不使用-R参数

补充:-gui参数是可选的,控制打开图形化界面,可以打开verdi或dve,dve是vcs原生的,而verdi用的比较广泛

2.3. 三步法

三步法相比于两步法将编译(compile)拆分成了分析(analysis)和细化(elaborate),一般是在面对多文件类型编译时(比如有verilog也有VHDL)用到。实际上这是按照VCS实际运行过程来划分步骤的,VCS运行的过程是将编译通过的文件临时存储,然后通过细化成为可执行的文件.simv,最后通过执行.simv文件即可完成文件的编译与仿真。

在Makefile中先实现分析命令(首参数是vlogan或vhdlan,分别编译verilog和VHDL文件,这里的an是analysis的缩写),再实现细化命令(首参数是vcs),最后实现仿真命令。

三步法Makefile编译示例

三、常见错误

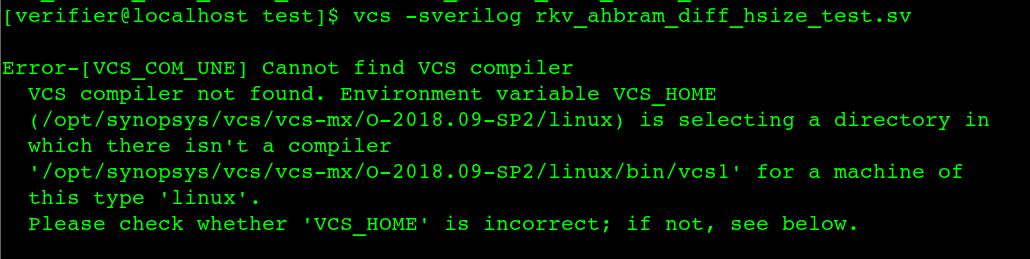

cannot find vcs compiler

不用Makefile编译,时常会少打一些编译参数,比如缺少-full64,则会报cannot find vcs compiler。另外如果编译sv文件,不加-sverilog则会报syntax error(语法错误)

四、参考资料

关于VCS仿真的详细流程:

VCS仿真流程_甲六乙的博客-CSDN博客_vcs vlogan

Makefile详细编写实例:

【数字IC快速入门】Makefile脚本了解_Thomas-w的博客-CSDN博客_makefile脚本

Makefile中的=,:=,+=的用法

Makefile中:=, =, ?=和+=的含义_keep_forward的博客-CSDN博客_makefile中:=

debug选项