1、系统时钟的来源

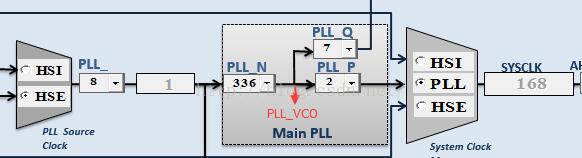

STM32F407具有两个PLL,用于产生不同的时钟信号。这里主要来讨论主PLL时钟。主PLL时钟的时钟源有两个信号,分别是上边提到的HIS信号和HSE信号。PLL通过把这两个信号倍频,分频等达到更高频率的时钟信号。一般来说,由于HIS和HSE的时钟频率较低,SYSCLK一般都不会选择HIS时钟和HSE时钟作为系统时钟,而主PLL产生的时钟一般会用作系统时钟。下面我们来看下主PLL的内部结构框图。

由图可以看出PLL的时钟源主要有两个:HSE时钟信号和HIS时钟信号。其中PLL_M,PLL_N,PLL_P,PLL_Q是一个分频器,而PLL_M是一个倍频器。假设上图中经过PLL_N之后的时钟信号为PLL_VCO,PLL使用外部时钟信号HSE作为时钟源。那么有如下关系。

PLL_VCO = (HSE / PLL_M)* PLL_N

SYSCLK = PLL_VCO/ PLL_P

2、系统时钟的配置

- plln: PLL1 倍频系数(PLL 倍频),取值范围:4~512.

- pllm: PLL1 预分频系数(进 PLL 之前的分频),取值范围:2~56.

- pllp: PLL1 的 p 分频系数(PLL 之后的分频),分频后作为系统时钟,取值范围:2~128

- pllq: PLL1 的 q 分频系数(PLL 之后的分频),取值范围:1~128.

所以,如果外部晶振的频率已经确定了,那么确定PLL_M,PLL_N,PLL_P的系数就可以得到对应频率的系统时钟SYSCLK,其中PLL_M,PLL_N,PLL_P可以有多种组合,只要满足相应的条件即可。例如,假设外部晶振为8M,对STM32F407来说,系统时钟的最大频率为168M,那么久可以分别设置PLL_M = 8,PLL_N = 336,PLL_P = 2。来产生168M的时钟。即SYSCLK = ( 8 /8 ) * 336 / 2 = 168M。

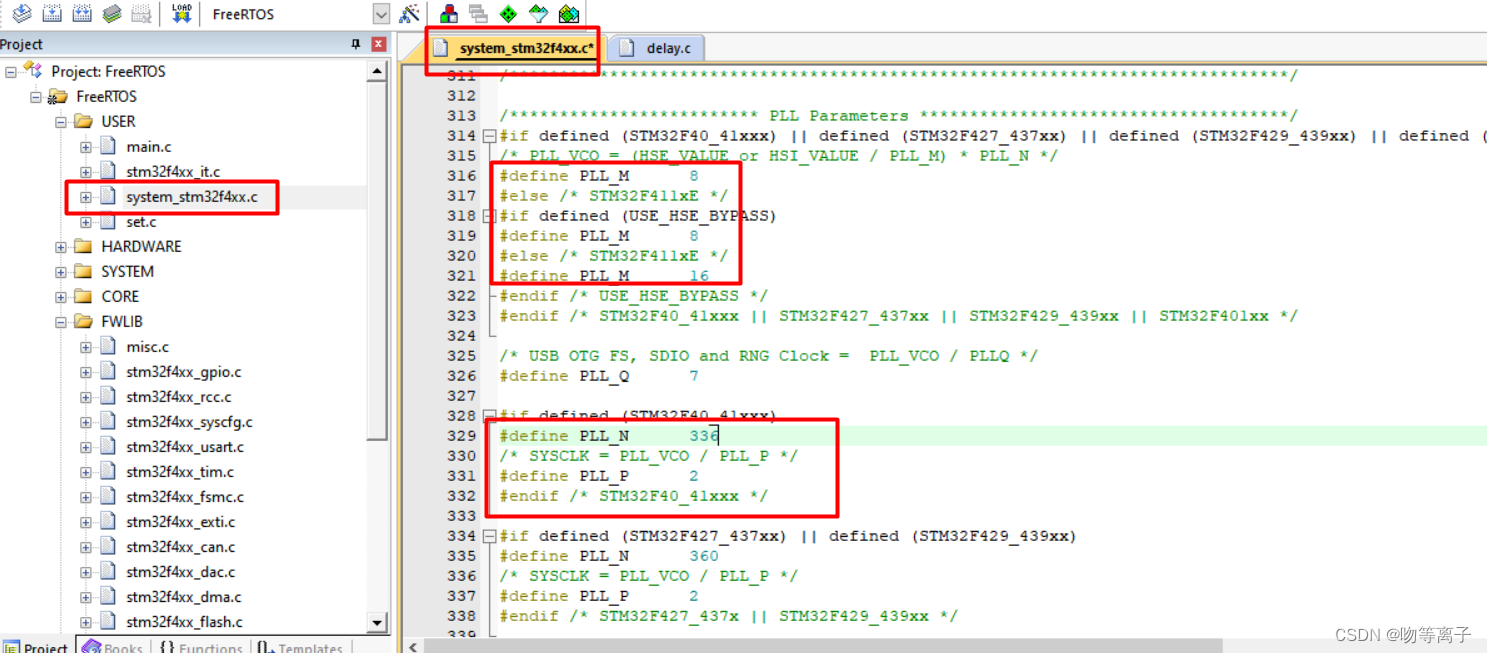

在下列文件中配置PLL参数

通过配置主PLL,我们就得到了系统的主时钟SYSCLK,下一步我们就可以通过这个时钟来分频得到各个外设的时钟。

3、查看stm32系统时钟

第一步在main函数开头添加如下代码:

RCC_ClocksTypeDef RCC_Clocks;

RCC_GetClocksFreq(&RCC_Clocks);

RCC_ClocksTypeDef结构体原型在stm32f4xx_rcc.h中:

typedef struct

{

uint32_t SYSCLK_Frequency; /*!< SYSCLK clock frequency expressed in Hz */

uint32_t HCLK_Frequency; /*!< HCLK clock frequency expressed in Hz */

uint32_t PCLK1_Frequency; /*!< PCLK1 clock frequency expressed in Hz */

uint32_t PCLK2_Frequency; /*!< PCLK2 clock frequency expressed in Hz */

}RCC_ClocksTypeDef;

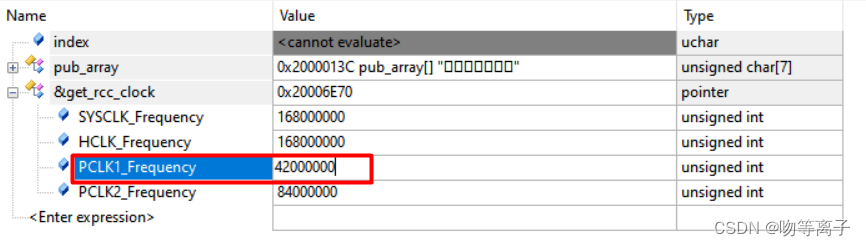

然后仿真就可以看到系统各个时钟值了:

注意:这里默认是显示十六进制数的,需要对这些数据点击右键会出现"Hexadcimal Display"打勾,点击一下就可以切换到十进制数了。