Intel系列微处理器概述

8086/8088微处理器

8086/8088微处理器是英特尔公司于1978年推出的16位处理器,在80年代是个非常流行的芯片,被广泛用于个人电脑和工作站。它是x86家族处理器的一员,被视为现代PC体系结构的基础。

8086/8088微处理器的主要特点如下:

-

16位架构:支持16位数据总线和地址总线,同时可以处理16位指令。

-

分段式内存管理:通过分段机制,可以寻址最大1MB的物理地址空间。

-

x86指令集:8086/8088使用x86指令集,其指令集最初基于Intel 8008和8080处理器指令集,后来逐步演变为现代x86指令集。

-

工作频率:8086处理器是5MHz,而8088是4.77MHz。后来,一些版本的处理器能够在更高的频率下工作。

-

外部设备支持:支持外部设备的接口协议,例如串口、并口、键盘和鼠标。

-

可编程中断控制器:可编程中断控制器(PIC)是一个集成电路,用于协调计算机的中断请求。8086/8088处理器系统使用由Intel推出的8259 PIC。

今天,8086/8088处理器系统已经被现代x86处理器和其他处理器体系结构所取代,但它作为计算机历史上的一个重要里程碑,仍被视为计算机行业的经典之一。

80286微处理器

80286微处理器是英特尔公司于1982年推出的16位处理器。与8086/8088相比,80286处理器具有更高的工作频率,更优秀的性能,以及更好的内存管理能力。

80286微处理器的主要特点如下:

-

16位处理器:与8086/8088一样,80286也是16位微处理器。

-

更快的工作频率:80286处理器的工作频率是6或8 MHz,比8086/8088处理器快了1.2倍至1.6倍,因此处理能力更强。

-

更多的内存:80286处理器的物理寻址能力提高到了16MB,因此可以通过扩展内存,使得拥有更大的内存地址空间成为可能。

-

保护模式:80286处理器引入了保护模式,使得可以在不同的任务之间切换,从而实现多任务处理和更好的内存管理。

-

具备虚拟内存:80286处理器支持基于虚拟内存的内存管理机制,这大大提高了计算机系统的灵活性和稳定性。

-

支持指令集扩展:80286处理器支持指令集扩展,例如浮点运算指令扩展。

80286处理器由于其性能和扩展能力的提高,成为了当时IBM PC和Apple Macintosh等计算机系统的主流处理器,奠定了后来x86体系处理器的基础。

80386/80486微处理器

80386和80486微处理器是英特尔公司基于x86架构推出的高性能处理器。它们是8086/8088和80286微处理器的后继产品,以其更高的性能和更好的扩展性能提高了计算机系统的处理能力。

80386微处理器的主要特点如下:

-

32位处理器:80386是首款32位微处理器,它可以处理32位数据、地址和指令。

-

更快的工作频率:80386处理器的工作频率达到了16或33MHz左右,比80286处理器快了2倍左右,因此处理能力更强。

-

保护模式:与80286处理器类似,80386引入了保护模式,使得可以在不同的任务之间切换,从而实现多任务处理和更好的内存管理。

-

虚拟内存:80386处理器实现了页式内存管理机制,可以支持更大的内存容量。

-

指令集扩展:80386处理器增加了大量的新指令,并支持新的内存寻址模式。

而80486微处理器则在80386基础上进一步提高了性能和扩展能力。具体而言,其主要特点如下:

-

更高的工作频率:80486处理器的工作频率可达50、66、75甚至100MHz,比80386处理器快了好几倍,从而实现更强的计算处理能力。

-

高速缓存:80486处理器引入了高速缓存技术,并且运行在其内部的时钟速度上,使得程序执行速度更快。

-

更好的数字信号处理能力:80486处理器集成了数学协处理器,提升了数字信号处理的运算速度。

-

支持分段式虚拟内存:80486引入了一些新的特性,如支持分段式虚拟内存,从而大大提高了系统的灵活性和性能。

80386/80486微处理器的上市为计算机系统的性能提升带来了质的飞跃,成为80年代末和90年代初计算机领域的经典之一,对于计算机技术的发展产生了巨大的影响。

Pentium微处理器

Pentium是英特尔公司于1993年推出的微处理器,作为8086/8088、80286、80386和80486的继任者,是x86架构的第五代微处理器。Pentium微处理器的推出,引领了计算机芯片焕发新的生机和能力,而且在当时的市场上非常成功。

Pentium微处理器的主要特点如下:

-

首个支持超标量处理的微处理器:这意味着一个时钟周期内,可以同时执行多个指令,提高了处理能力。

-

内置浮点数处理器:Pentium处理器集成了浮点数处理器,从而可以更快、更精准地处理浮点数运算。

-

更快的运行速度:Pentium处理器的运行速度可以达到60-200MHz,比其前任80286、80386、80486处理器大大提升。

-

支持大内存:Pentium处理器支持最高达4GB的内存。

-

更多的指令并行:Pentium处理器配了两个独立的指令流水线,可以同时处理两个指令。

-

新增64位数据总线:这使得Pentium处理器在访问内存时更快,从而提高了计算机的运行速度。

总的来说,Pentium处理器的推出,是中央处理器速度倍增及多媒体计算机的奠定基础,其高性能、高速度、高精度等特点,也将计算机领域的应用向着一个更高层次引领。之后,Pentium系列的处理器被广泛应用并发展壮大,成为了当今个人电脑市场上处理器尤其是x86架构的无可争议的领导者。

80486微处理器的体系结构

80486微处理器的体系结构特点

-

32位处理器:与80286一样,80486也是一款32位处理器,可以处理32位数据、指令和地址。

-

高速缓存:80486处理器中包含了8K的一级缓存,可以降低访问内存的频率,从而提高了性能。

-

浮点运算单元集成:由于过去的80286和80386没有集成浮点运算功能,所以这是80486的一个重要变化。80486的硬件集成了浮点运算器,可以更快速和准确地执行浮点运算。

-

支持虚拟内存:在80386处理器中已经引入了分页式的内存管理机制,但是在80486处理器中,对于虚拟内存的支持做出了更为完善和优化。

-

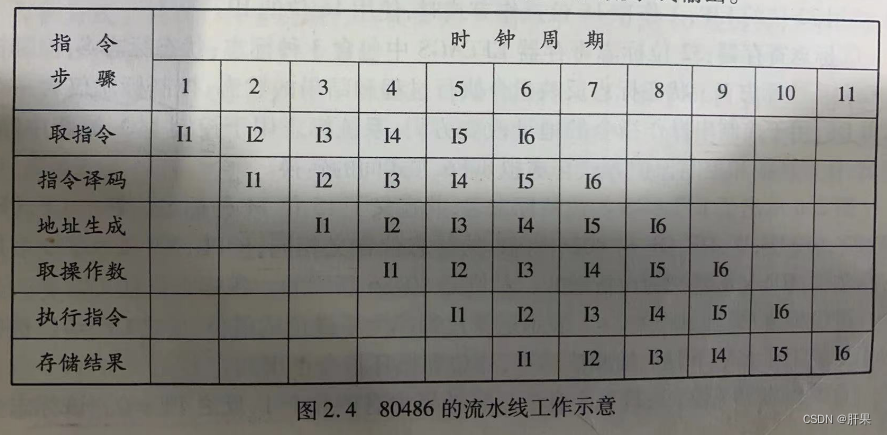

指令流水线:80486处理器的指令流水线有五级,这意味着处理器内部可以同时处理五条指令,提高了处理器的性能和效率。

-

高速时钟:80486处理器内部集成了时钟倍频器,在基准时钟的基础上提升到了50MHz或更高的速率,从而增加了运算能力和速度。

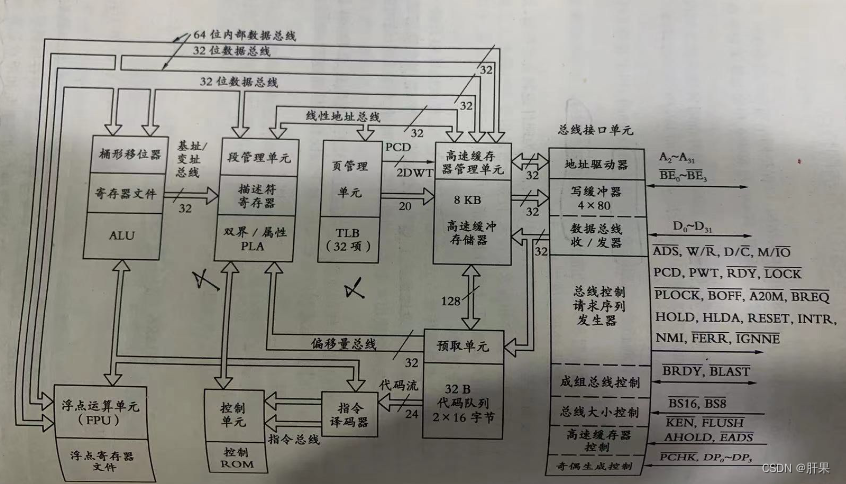

80486微处理器的内部结构

80486微处理器主要由总线接口单元、指令预取单元、指令译码单元、指令执行单元、段管理单元、页管理单元、高速缓冲存储器单元和浮点运算单元等8个逻辑单元组成。

1、总线接口单元主要用于外部地址、数据和控制总线管理,完成预取指令、读/写数据等总线操作。

2、指令预取单元内含1个32个字节的指令预取队列。

内部寄存器

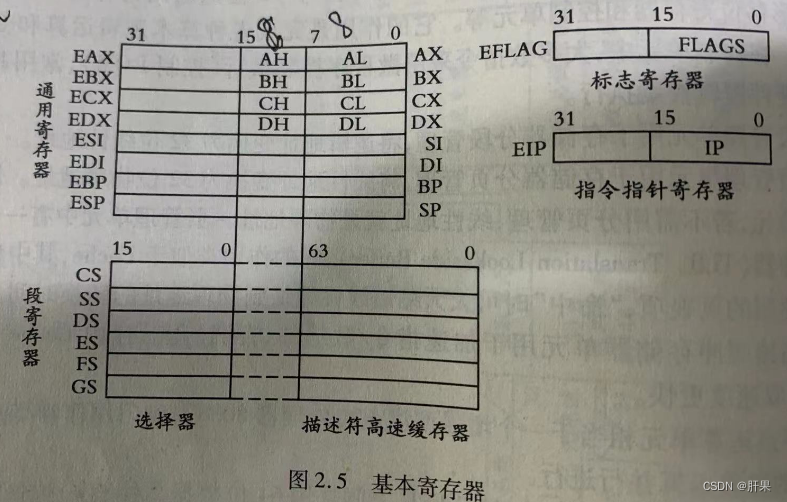

1、基本寄存器

基本寄存器包括通用寄存器、指令指针寄存器(EIP)、标志寄存器(EFLAGS)和段寄存器。

(1)通用寄存器

80486是一种x86微处理器,具有多个通用寄存器。它有8个32位的通用寄存器,每个寄存器可以存储32位的数据。这些寄存器被命名为EAX、EBX、ECX、EDX、ESI、EDI、EBP和ESP。

EAX寄存器通常用于存储函数返回值或算术运算的结果。

EBX寄存器通常用于存储内存地址或其他数据指针。

ECX寄存器通常用于计数,例如循环计数。

EDX寄存器通常用于存储除法或乘法的结果。

ESI和EDI寄存器通常用于存储源和目标指针,特别是在字符串或存储数据的数组中。

EBP寄存器通常用于指向堆栈中的帧指针,这对于函数调用和局部变量的管理非常有用。

ESP寄存器通常用于指向堆栈指针,这对于跟踪函数调用和返回非常有用。

这些通用寄存器在编程中发挥着非常重要的作用,使得程序员可以方便地进行数据存储和操纵,从而实现复杂的计算和操作。

(2)指令指针寄存器

80486微处理器的指令指针寄存器是EIP(Extended Instruction Pointer)。EIP寄存器存储着下一个执行的指令的地址。当处理器执行指令时,它会从内存中读取指令的二进制代码,并将EIP寄存器设置为下一条指令的地址,以便在执行完成当前指令后转到下一条指令。在分支指令(如跳转和调用指令)执行时,EIP寄存器会被修改以跳转到另一个地址执行指令。

EIP寄存器的大小是32位,因此可以存储4字节的地址。在实模式下,这意味着它可以寻址1MB的内存空间;在保护模式下,它可以寻址4GB的内存空间。EIP寄存器是x86架构中非常重要的寄存器之一,因为它控制着程序的执行流程,并允许程序员实现复杂的控制结构和程序逻辑。

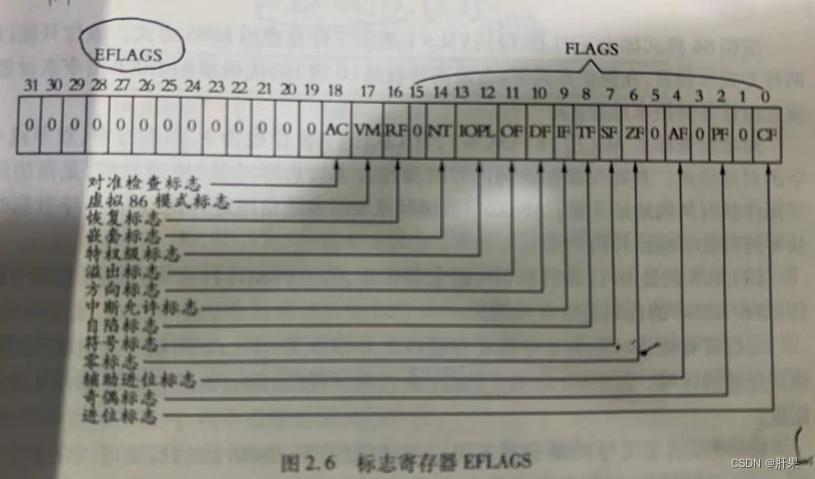

(3)标志寄存器

80486微处理器的标志寄存器是EFLAGS(Extended Flags Register)。EFLAGS寄存器存储着处理器的状态信息,其中包括算术运算和逻辑运算的结果、控制流程和中断处理等。EFLAGS寄存器的每一个比特都代表着一个不同的标志位(或者称为标志位标志),用于提供不同的状态信息。

下面是EFLAGS寄存器中各个标志位的含义:

- CF (Carry Flag) 标志位:用于指示算数操作中是否出现了进位或借位情况。

- PF (Parity Flag) 标志位:用于指示结果中二进制位中“1”的个数是否为偶数。如果“1”的个数是偶数,则PF标志位被设置为1,否则为0。

- AF (Auxiliary Carry Flag) 标志位:用于指示算数操作中是否出现了半进位或半借位情况。

- ZF (Zero Flag) 标志位:用于指示运算结果是否为0。如果结果为0,则ZF标志位被设置为1,否则为0。

- SF (Sign Flag) 标志位:用于指示运算结果的符号。如果结果为正,则SF标志位为0,否则为1。

- TF (Trap Flag) 标志位:用于指示调试器是否需要跟踪每一条指令。

- IF (Interrupt Flag) 标志位:用于控制是否允许中断。

- DF (Direction Flag) 标志位:用于指示字符串操作的方向。如果DF标志位被设置为1,则字符串操作从高地址到低地址执行;如果DF标志位为0,则字符串操作从低地址到高地址执行。

- OF (Overflow Flag) 标志位:用于指示算数操作是否发生了溢出。

EFLAGS寄存器在编程中非常重要,因为它与处理器的状态信息相关,能够用于控制程序的执行流程和中断处理等。

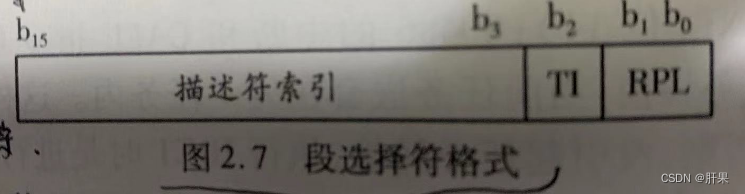

(4)段寄存器

80486微处理器有6个段寄存器,它们是CS、DS、ES、FS、GS和SS。这些段寄存器用于管理内存中的段。在x86架构中,任何内存地址都由一个段地址和一个偏移地址组成。段寄存器存储着段地址,而通用寄存器(例如EAX、EBX等)存储着偏移地址,当组合后就可以得到特定的内存地址。

下面是每个段寄存器的简要说明:

- CS (Code Segment) 寄存器:用于存储代码段的地址,通常用于存储正在执行的指令。

- DS (Data Segment) 寄存器:用于存储数据段的地址,通常用于存储程序中的变量和数据。

- ES (Extra Segment) 寄存器:用于存储其他数据段的地址,它可以与DS寄存器一起用于处理一些特殊的数据访问情况。

- FS (F Segment) 寄存器:用于存储附加数据段的地址,通常用于存储线程局部存储的变量。

- GS (G Segment) 寄存器:用于存储另一个附加数据段的地址,通常用于存储进程局部存储的变量。

- SS (Stack Segment) 寄存器:用于存储堆栈段的地址,通常用于存储函数调用的返回地址和局部变量等数据。

这些段寄存器在内存管理和程序执行过程中都有非常重要的作用,能够帮助CPU管理不同的数据和代码段,并确保程序在正确的地址空间中执行。

2、系统级寄存器

包括4个控制寄存器和4个系统地址寄存器。

(1)控制寄存器

80486微处理器有多个控制寄存器,用于控制和管理处理器的各种行为和操作。下面是常用的一些控制寄存器:

-

CR0 (Control Register 0):CR0寄存器包含了多个控制标志位,包括保护模式开关、分页机制开关、缓存控制等。程序员可以通过写入特定的值到CR0寄存器中来控制这些标志位。

-

CR2 (Control Register 2):CR2寄存器用于记录最近的缺页异常地址,这个地址用于交给操作系统来进行异常处理。

-

CR3 (Control Register 3):CR3寄存器包含了分页机制相关的信息,例如页目录表的地址等。程序员可以通过修改CR3寄存器来切换不同的地址空间。

-

CR4 (Control Register 4):CR4寄存器包含了一些处理器扩展功能的控制标志位,例如在x86架构中支持物理地址扩展 (PAE) 机制、支持全局页面管理 (PGE) 等。

这些控制寄存器对于操作系统和底层软件的开发非常重要,它们提供了对处理器各种行为和功能的控制,使得程序员可以更好地管理和优化系统的性能、稳定性和安全性。

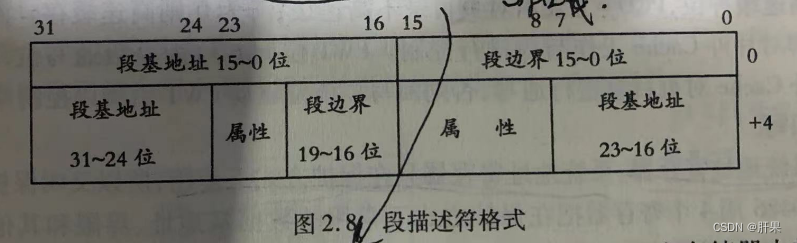

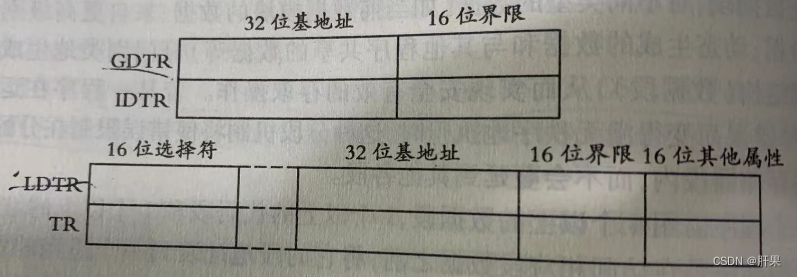

(2)系统地址寄存器:系统地址寄存器只在保护方式下使用。

80486微处理器有两个系统地址寄存器,分别是GDTR和IDTR。

-

GDTR (Global Descriptor Table Register):GDTR寄存器存储了全局描述符表(GDT)的基地址和限长。GDT是分段机制中的一个数据结构,它定义了每个段的基地址、大小、访问权限等信息。GDTR寄存器的值被读入到处理器的硬件段寄存器中,用于查找和访问GDT中的描述符。

-

IDTR (Interrupt Descriptor Table Register):IDTR寄存器存储了中断描述符表(IDT)的基地址和限长。IDT是中断处理机制中的一个数据结构,它定义了每个中断或异常向量的处理函数地址和特权级等信息。IDTR寄存器的值被读入到处理器的硬件中断向量表中,用于查找和执行特定中断或异常的处理程序。

这些系统地址寄存器在x86架构的系统开发中都扮演着非常重要的角色,它们用于管理和组织系统中的各种数据结构和信息,并确保处理器能够正确地访问和执行它们。

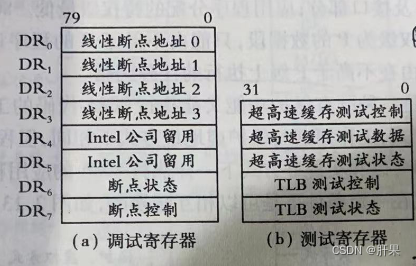

3、调试和测试寄存器

80486微处理器有两个调试和测试寄存器,分别是DR0和DR7。

-

DR0 (Debug Register 0):DR0寄存器用于设置调试或断点条件,例如在某个内存地址或I/O端口上设置断点。当程序执行到指定的断点处时,处理器会发出异常中断信号,加载中断处理程序或调试器来进行后续的处理。

-

DR7 (Debug Register 7):DR7寄存器用于控制DR0~DR3寄存器中断点的状态,包括断点长度、是否触发INT1、是否执行单步调试等。

这些调试和测试寄存器的主要作用是帮助程序员进行调试和性能优化。在程序执行过程中,可以通过设置断点或者执行单步调试等方法,查看程序的执行过程和结果,并进行问题排查和代码优化。同时,这些寄存器也被用于系统和软件的安全性测试,以便发现和修复存在的安全漏洞和问题。

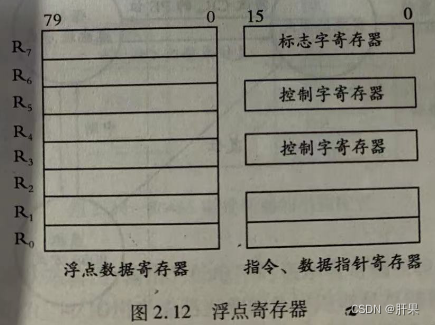

4、浮点寄存器

80486微处理器同时支持两种浮点数数据类型:单精度 (32位) 和双精度 (64位)。为了支持这些浮点数数据类型,它有8个浮点寄存器,分别是ST0~ST7。

这些浮点寄存器是80位宽度的,可以存储不同类型的浮点数数据以及控制数据。这些寄存器还用于执行各种浮点运算,例如加、减、乘、除、取模等操作。处理器还提供指令来加载和存储浮点数据到和从内存中,同时还有指令来支持浮点比较和转换等操作。

在x86架构的系统开发中,浮点处理的性能经常是一个关键问题,因此该架构采用了浮点寄存器来高效处理这些浮点数数据。浮点寄存器能够处理高精度的数据,同时也能提高处理器的运算速度,帮助程序员编写更快和更准确的计算代码。

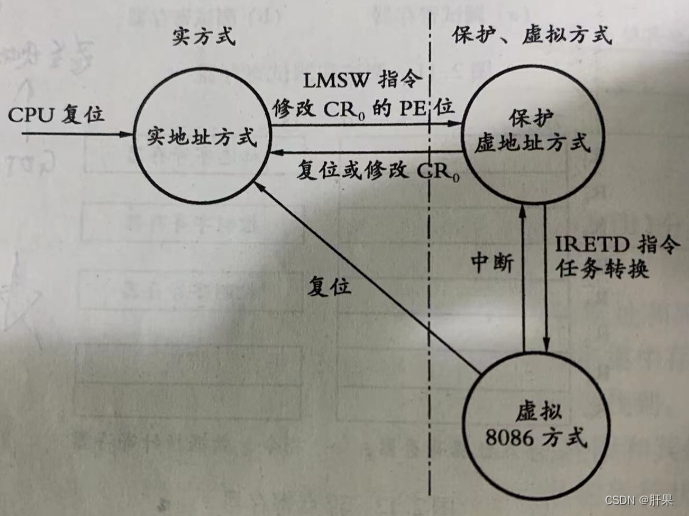

80486的工作方式及转换

80486有3种工作方式:实地址方式,保护虚地址方式和虚拟8086方式。

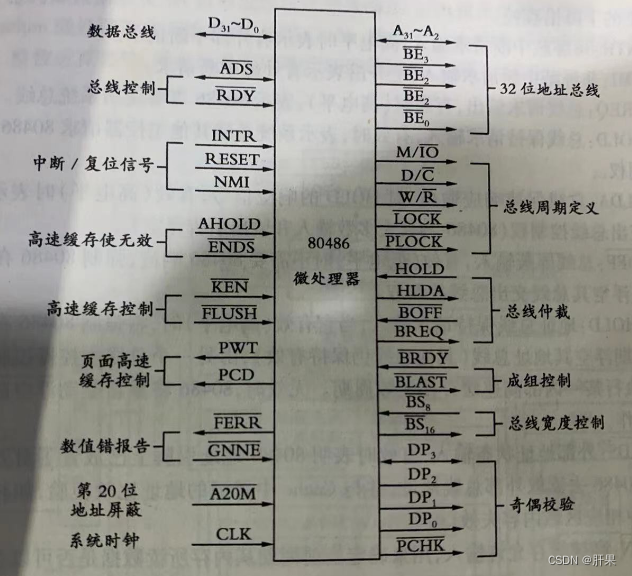

80486的引脚功能

80486 微处理器是英特尔推出的一款经典的 x86 微处理器,它有168个引脚。以下是其中一些常用引脚及其功能:

地址和数据总线引脚:包括 A0 到 A31 引脚,用于传输地址和数据信息。

控制信号引脚:例如,RD(读取)、WR(写入)信号引脚用于控制内存读写操作;M/IO(内存/IO)信号引脚用于区分访问内存还是外部设备;BE0 到 BE3(字节使能)信号引脚用于指示数据总线上的有效字节。

时钟引脚:CLK(时钟)引脚提供微处理器的时钟信号,驱动其工作频率。

电源引脚:VCC 引脚为电源引脚,提供微处理器所需的电压供应。

标志引脚:包括标志引脚 PF0 到 PF3(中断前缀)和标志引脚 FLUSH(刷新),用于中断处理和相关操作。

外部总线接口引脚:如HOLD(挂起)和HLDA(挂起确认)引脚,用于与其他设备进行总线互连时的控制信号传输。

习题:

1、80486CPU由哪几个部件组成?各部件的功能是什么?

算术逻辑单元 (ALU):负责执行算术和逻辑运算,例如加法、减法、乘法和逻辑与、或、非等操作。

控制单元 (Control Unit):管理和协调CPU内部的各个部件,并决定程序的执行顺序。它从内存中读取指令,并发送控制信号给其他部件以执行相应的操作。

寄存器 (Registers):用于临时存储数据和指令。不同类型的寄存器包括指令寄存器、数据寄存器、地址寄存器等。

缓存 (Cache):作为高速缓存存储器,用于存储最常访问的数据和指令,提高CPU的访问速度。

总线接口单元 (Bus Interface Unit):与外部设备和系统总线进行通信,负责数据传输和地址管理。

浮点运算单元 (Floating-Point Unit):专门负责执行浮点运算操作,例如浮点加法、减法、乘法和除法。

内部时钟发生器 (Internal Clock Generator):产生CPU内部的时钟信号,控制指令和操作的执行速度。

这些部件共同协作,完成CPU的各种计算和控制任务。

2、8086中,存储器的物理地址是如何生成的?若已知逻辑地址为B100:A300,试求物理地址。

在8086处理器中,物理地址是通过逻辑地址经过段地址转换和偏移地址的组合来生成的。

具体步骤如下:

段地址转换:将段地址与16相乘,得到20位的段基址,即将逻辑地址中的B100左移4位,得到B1000。

偏移地址:将A300直接拼接到B1000后面,得到B10000A300。

物理地址:将B10000A300作为物理地址。

所以,根据已知的逻辑地址B100:A300,对应的物理地址为B10000A300。

3、假设用户程序装入内存后SS=095BH,SP=0040H,试问该用户程序的栈底物理地址是多少?

栈底物理地址的计算公式如下:

栈底物理地址 = SS x 16 + SP

将给定的数值代入公式中进行计算:

栈底物理地址 = 095Bh x 16 + 0040h

首先将十六进制转换为十进制:

SS = 095Bh(十六进制)= 2395(十进制)

SP = 0040h(十六进制)= 64(十进制)

然后进行计算:

栈底物理地址 = 2395 * 16 + 64

栈底物理地址 = 38240 + 64

栈底物理地址 = 38304

因此,该用户程序的栈底物理地址是38304。

4、8086系统中,设CS=0914H,代码段长度为244个字节,该代码段末地址的逻辑地址(段地址,偏移地址)和物理地址各是多少?

根据提供的信息,假设在8086系统中,CS寄存器值为0914H。代码段长度为244个字节。

对于逻辑地址(段地址,偏移地址)和物理地址的计算,我们需要考虑到8086实模式下的内存分段机制。

首先,将CS寄存器值左移4位并且加上偏移地址,从而得到逻辑地址的偏移部分。然后,逻辑地址的段部分为CS寄存器的值。

逻辑地址(段地址,偏移地址)的计算如下:

段地址 = CS

偏移地址 = 0

将给定的数值代入公式中进行计算:

段地址 = 0914H(十六进制)= 2324(十进制)

偏移地址 = 0

因此,逻辑地址(段地址,偏移地址)为(2324, 0)。

接下来,将逻辑地址转换为物理地址。

物理地址的计算公式如下:

物理地址 = 段地址 * 16 + 偏移地址

将逻辑地址的段地址和偏移地址代入公式中进行计算:

物理地址 = 2324 x 16 + 0

物理地址 = 37184

因此,该代码段末地址的逻辑地址为(2324, 0),物理地址为37184。