最近在使用xilinx的zynq-7010开发、调试一个Lora模块,与模块进行spi通信时候出现linux应用层接收不到模块发回的数据问题。先排除硬件问题,通过逻辑分析仪可以抓到总线上有正常的收发数据波形,那问题只能是在CPU侧的软件上了。然后在linux的spi标准驱动的spi->rxbuf上增加debug打印信息,也没有收到数据打印出来,最终定位xilinx写的SPI主机驱动处理接收数据过程可能存在问题,没有将硬件上的数据及时传输到spi驱动核心层的buf中;找到spi主机驱动的中断处理函数,数据最终是通过中断发送到硬件和接收数据到fifo。

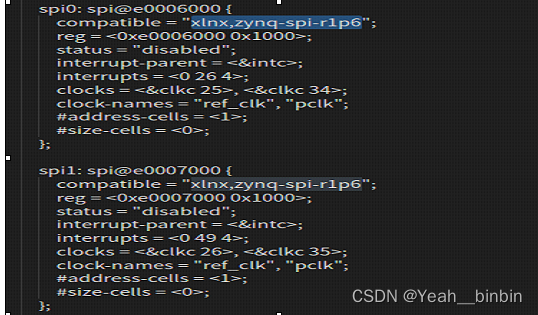

在dts通过compatible找到xilinx的spi主机驱动linux/drivers/spi/spi-cadence.c

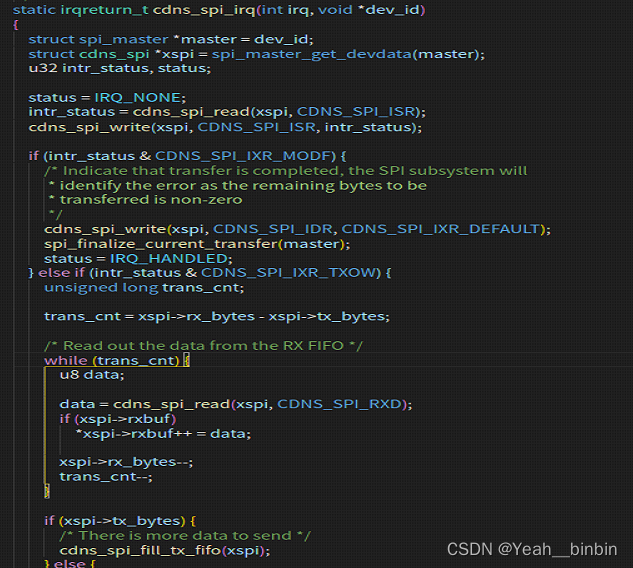

找到收发数据的中断处理函数。

原驱动的中断处理发送、接收数据逻辑(因为SPI的IP内部本质是个移位寄存器,因此发送和接收是同时进行的,即要接收数据一定要发数据出去):触发spi中断->tx为空的中断(数据都发出去了)->判断已经发了多少个字节数据出去->从RXFIFO接收相同个数字节数据->数据传递给上层的rxbuf->若还有数据没发完(还有数据要接收)则继续将数据写入txfifo->重复上述过程。

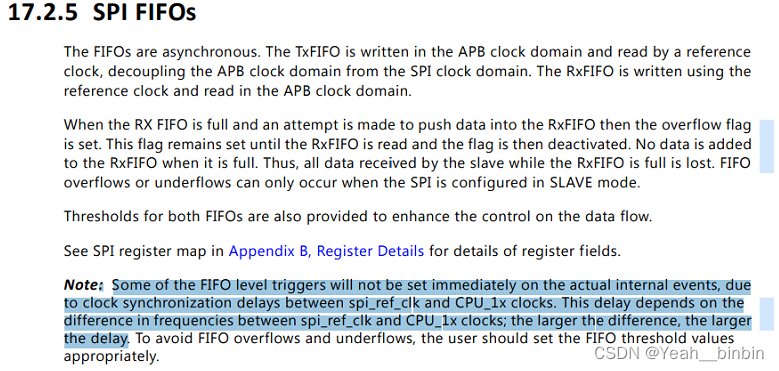

一开始感觉这个数据处理的逻辑没问题,在总线上确实也能抓取到发送和接收数据,但在应用层read到的数据一直为0。在这个中断处理函数里面加上printk(“data=%02X\n”,data),发现打印出来的也是0,因此问题就出现在从读取数据的时候,RXFIFO里面的数据还是0,推测原因:CPU处理速度较快,主频远大于SPI的工作时钟(模块的最大SPI时钟为2M),数据可能还未被采样存入RXFIFO而CPU就从FIFO里面读取数据了,因此读取的数据都是默认为0。从官方的datasheet也找到这点提示。

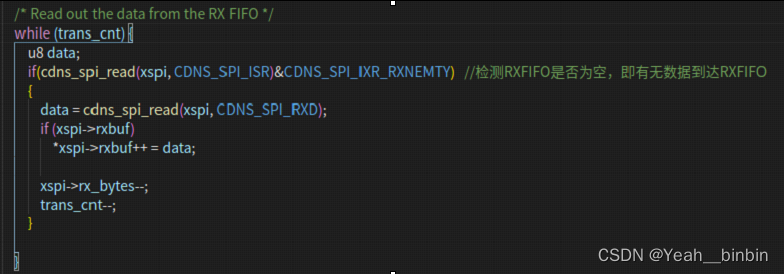

修改后:在中断处理读取rxfifo时候加上检测RXFIFO是否为空(即有无数据被存入RXFIFO),确保有RXFIFO数据后才开始读取,最终打印的数据正常,也能正确传给应用层。