SPYGLASS初步使用教程

文字目录

SPYGLASS是很高效的RTL分析和CDC检查工具,可以有效的帮助规避设计中的难以察觉的问题,帮助设计人员提高设计质量。本文的目的在于给刚刚接触的人提供一个基础实践指导,根据既有的流程来认识这个软件。

本文由4个基础实验构成,详细介绍了SPYGLASS在不同阶段的运行说明,学会这几个基础实验的操作是使用别的SPYGLASS分析的基础。同时几个实验也需要按顺序操作,每个实验是下一个实验的基础。实验源码在文字隐含链接中,直接点击即可下载。

(本实验是基于snopsys教程的翻译,是为了各位可以快速对spyglass有了解,文中的相关操作自己已经动手完成验证。本来有5个,但最后一个个人认为没啥用,就不在这里加入。)

1.整体实验文件预览

1.1 RTL框图

下图为实验中使用的rtl源码的设计框图。该设计包括一个终端为一个USB控制器和音频解码器核心(IMA_ADPCM),两者通过Wishbone总线连接到叉骨连接矩阵(WB_Conmax),该矩阵又使用一个WB2AHB桥连接到AHB总线。该设计为混合型RTL设计,包括verilog和vhdl两种编程语言。![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-3PADEsyx-1605094790058)(F:\VM_SHARE\synglass\RTL框架.jpg)]](https://img-blog.csdnimg.cn/20201111194040775.jpg?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMwODQzOTUz,size_16,color_FFFFFF,t_70#pic_center)

1.2 实验目录结构

实验目录包括:rtl(用于存放代码),spyglass(用于存放中间文件和工程文件),doc(用于存放自己添加的说明文件)。图示如下:

2.实验一

本实验目的在于知道如何使用gui来进行读取文件和进行结果分析。

2.1 读取设计文件

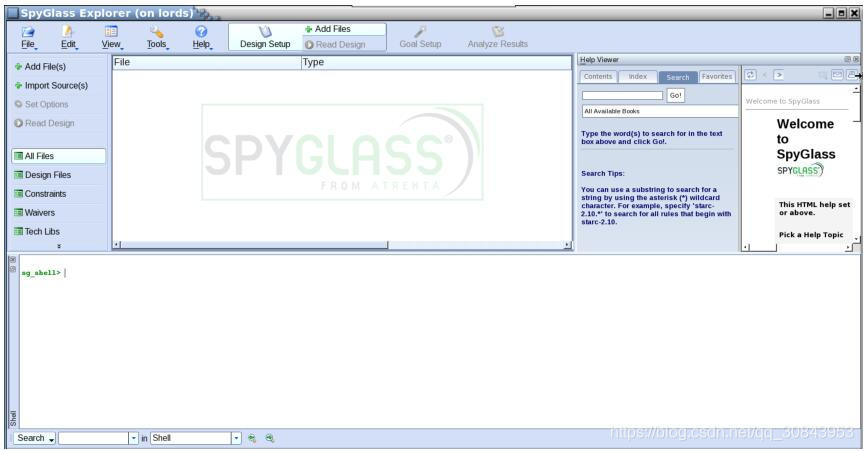

本实验中,创建完整目录结构后,首先切换到工作目录下,然后打开软件:

% cd spyglass

% spyglass &

此时可以看到如下界面:

然后点击Add File(s), 此时会打开添加文件窗口。左侧窗口用来切换目录和选择文件,右侧显示已经选择的文件。左侧选择文件后点击中间的Add即可完成文件的添加,点击OK退出当前窗口。

本实验中需要读取的文件为:

../rtl/ahb2wb.v

../rtl/wb_subsystem.v

2.2 设置顶层模块

添加完文件后点击Set Options,然后选择列表中选择Top Level Design Unit,Value值为顶层模块名(此处顶层模块为wb_subsystem),如下图所示:

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-ZUibMxUV-1605094790061)(F:\VM_SHARE\synglass\3.jpg)]](https://img-blog.csdnimg.cn/20201111194209401.jpg?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMwODQzOTUz,size_16,color_FFFFFF,t_70#pic_center)

2.3 编译设计,得到结果

点击Read Design,再在左侧点击Run Design Read开始进行设计文件编译和分析,在读取完成后会在下方窗口列出问题。如下图所示:

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-2VRfHIrh-1605094790063)(F:\VM_SHARE\synglass\4.jpg)]](https://img-blog.csdnimg.cn/20201111194303875.jpg?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMwODQzOTUz,size_16,color_FFFFFF,t_70#pic_center)

其中三个问题类型都为ErrorAnalyzeB Box,这是因为有的模块文件没有添加,SPYGLASS找不到,后面SPYGLASS会将其作为黑盒子处理。

左侧instance下文件不同颜色标识意义为:绿色表示该模块可进行分析,但不可进行综合;黑色表示该模块作为黑盒子存在;白色表示该模块可综合。需要注意,只是读取设计并不会完成综合,因此也不会创建相关的原理图。因此,为了使用spyglass,首先应该解决黑盒子问题,为此需要选择复选框Synthesize Netlist然后重新运行Design Read。

2.4 静态分析

下面列出使用spyglass来进行linting分析的步骤。注意使用spyglass进行分析不要求完整的工程文件。

首先选择Linting RTL分析。在窗口上方中间点击Goal Setup ,然后在主窗口区勾选Lint_rtl(在lint中点击+即可见),如下图。虽然可以一次选择多个目标设置,但分析过程是顺序执行的,只要前面的检查通过了才会进行后面的检查。

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-p1h1UWjF-1605094790065)(F:\VM_SHARE\synglass\5.jpg)]](https://img-blog.csdnimg.cn/20201111194324201.jpg?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMwODQzOTUz,size_16,color_FFFFFF,t_70#pic_center)

然后点击Run Goal(s) ,当运行完成,会自动弹出Analyze Result窗口。

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-OTd8jhQ0-1605094790067)(F:\VM_SHARE\synglass\6.jpg)]](https://img-blog.csdnimg.cn/20201111194338688.jpg?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMwODQzOTUz,size_16,color_FFFFFF,t_70#pic_center)

得到分析结果后,首先查看Lint分析结果。首先展开lint/lint_rtl文件夹消息。错误信息以红色显示,警告以橙色显示,信息以绿色显示。选择并展开inferLatch Error文件夹。双击第一条违规消息。此时与错误相关的代码会在RTL代码窗口中显示出来,如下所示。

![ [外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-TksxEPBP-1605094790068)(F:\VM_SHARE\synglass\7.jpg)]](https://img-blog.csdnimg.cn/2020111119435369.jpg?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMwODQzOTUz,size_16,color_FFFFFF,t_70#pic_center)

此时来对该问题进行分析。有消息可知,由于设计问题生成了非期待的锁存器。可以看到违规消息左侧有一个 ,这个意思是该违规消息包含一些原理图方面信息。通过点击

,这个意思是该违规消息包含一些原理图方面信息。通过点击![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-tTUMuad6-1605094790070)(C:\Users\admin\AppData\Roaming\Typora\typora-user-images\image-20201110201514066.png)]](https://img-blog.csdnimg.cn/20201111194646183.jpg#pic_center) 可以打开相关的逻辑示意图:

可以打开相关的逻辑示意图:

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-IECiTuUS-1605094790071)(F:\VM_SHARE\synglass\8.jpg)]](https://img-blog.csdnimg.cn/20201111194728951.jpg?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMwODQzOTUz,size_16,color_FFFFFF,t_70#pic_center)

在本次例子中,是因为hready信号在没有else的if语句中被赋值。如果这些Latch是故意的,那通过屏蔽对该处的规则检查即可。如果需要修改代码,可以在代码窗口中点击有问题的代码行,使得光标落于该行,然后点击e即可将打开默认的编辑器进行代码编辑。编辑完后要重新运行Goal。

2.5 实验一总结

关闭窗口之前应该先保存。可以用编辑器打开工程文件wb_subsystem.prj,因为顶层文件为wb_subsystem.v,所以工程文件名为wb_subsystem。打开的文件如下:

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-ydiOWfC8-1605094790071)(F:\VM_SHARE\synglass\9.jpg)]](https://img-blog.csdnimg.cn/20201111194745351.jpg?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMwODQzOTUz,size_16,color_FFFFFF,t_70#pic_center)

-

read_file命令定义了在SpyGlass运行期间要读取的各种类型的文件;

-

language_mode选项用于指定当前SpyGlass运行的操作语言。默认值为mixed(将处理Verilog、VHDL和混合语言设计);

-

projectwdir选项用于指定项目工作目录;

-

GuideWare/latest是默认的规则设置,它在项目文件中被定义为active _ methodology。

从文件结构可以看出,这是基于TCL的文件操作。通过添加语句和选项,再运行该TCL脚本即可进行相关分析。第二个实验的目的就在于此。

3.实验二

本练习将涵盖将设计读入SpyGlass的各个方面,并将建立在前一个实验的基础上。在本实验中,我们将使用–batch选项在批处理模式下运行SpyGlass。同样的操作也可以在GUI模式下完成。

1.通过下面的指令来运行SpyGlass工程:

%spyglass -project wb_subsystem.prj -designread -batch

在本实验的工程中,终端显示如下:

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-n1Wro2V5-1605094790072)(F:\VM_SHARE\synglass\10.jpg)]](https://img-blog.csdnimg.cn/20201111194831988.jpg?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMwODQzOTUz,size_16,color_FFFFFF,t_70#pic_center)

提示有三个黑盒错误。

SpyGlass会生成比较多的报告,其中常用的报告为:

./wb_subsystem/wb_subsystem/Design_Read/spyglass_reports/moresimple.rpt

其内容如下:

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-IhmArmJN-1605094790073)(F:\VM_SHARE\synglass\11.jpg)]](https://img-blog.csdnimg.cn/20201111194847490.jpg#pic_center)

moresimple.rpt中的消息按严重性、规则名、文件名和行号的顺序排序。此报告提供了足够的信息来识别源文件中的违规。

2.在.prj中可以通过源文件列表的形式来读取源文件。本实验中在##Data Import Section下添加如下语句:

read_file -type sourcelist …/rtl/usb/file.list

read_fiel -type sourcelist …/rtl/wb_conmax/file.list

将下面命令的选项改为yes:(在**##Common Options Section**下)

set_option designread_enable_synthesis yes

将文件保存后重新运行Design Read。

通过上面的文件添加和设置消除了之前的黑盒问题,但因为新的文件加载也引入新的黑盒问题,如下所示:![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-Q0RKrD3B-1605094790073)(F:\VM_SHARE\synglass\12.jpg)]](https://img-blog.csdnimg.cn/20201111194911483.jpg#pic_center)

它们看起来是被实例化的标准单元,但不知何故,它们的定义没有被提供。这些单元格很可能是使用-y/-v选项传递的,所以让我们浏览一下“usb”中的目录,看看是否有任何丢失的库文件。可以看到usb_lib目录存在于“usb”目录中,但是没有-y被指定为file.list的一部分。

3.通过下列的语句来读取缺失的部分:

> set_option y { ../rtl/usb/usb_lib }

> set_option libext { .v }

将文件保存后重新运行Design Read来检查是否解决了USB黑盒问题。结果如下:

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-uWUVFQTq-1605094790074)(F:\VM_SHARE\synglass\13.jpg)]](https://img-blog.csdnimg.cn/20201111194935295.jpg?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMwODQzOTUz,size_16,color_FFFFFF,t_70#pic_center)

moresimple.rpt报告内容如下:![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-dFZ2snbZ-1605094790075)(F:\VM_SHARE\synglass\14.jpg)]](https://img-blog.csdnimg.cn/20201111194952758.jpg#pic_center)

可以看到剩下的一个黑盒错误来自块“IMA_ADPCM_top”。这部分采用VHDL设计,出现黑盒问题原因是其设计文件尚未包含在.prj文件。

4.预编译库来解决IMA_ADPCM_top黑盒问题。

要预编译一个HDL库,您必须指定要在逻辑库中预编译的文件列表,以及逻辑库名称和物理目录之间的映射。这是使用lib_hdlfiles(定义要编译到命名库的文件)和lib(将命名库映射到物理目录)选项完成的(添加到**.prj文件的##Data Import Section**部分):

set_option libhdlf ima_adpcm_lib "vhd_file.list"

set_option lib ima_adpcm_lib ./ima_adpcm_lib

其中vhd_file.list内容为需要编译的VHDL文件的路径列表。接下来删除包含上次运行保存的网表的结果目录,然后重新运行设计验证是否解决了黑盒问题:

%rm -rf wb_subsystem

%spyglass -project wb_subsystem.prj -designread -batch

运行结果如下:

![ [外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-xyzbWItA-1605094790076)(F:\VM_SHARE\synglass\15.jpg)]](https://img-blog.csdnimg.cn/20201111195010724.jpg?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMwODQzOTUz,size_16,color_FFFFFF,t_70#pic_center)

通过第二次的实验我们解决了全部黑盒问题。

4.实验三

本实验在实验二的基础上进行目标设置和结果检查。

可以通过下面命令来获取可用的Goal列表:

% spyglass –project wb_subsystem.prj -showgoals

获取结果如下:

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-zlghYGeb-1605094790076)(F:\VM_SHARE\synglass\16.jpg)]](https://img-blog.csdnimg.cn/20201111195031990.jpg?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMwODQzOTUz,size_16,color_FFFFFF,t_70#pic_center)

其中Run Status显示目标是否运行,如果运行会有生成了多少错误、警告和信息消息。注意有的Goal的运行要求使用额外的SpyGlass组件。如果使用SpyGlass v2016.06或更高版本,需要为lint/lint_rtl目标启用checkfullbus参数(以使lint结果与本实验最初为v5.6.0创建的结果相匹配)。为此,请在wb_subsystem.prj文件的末尾添加以下内容:

current_goal lint/lint_rtl

set_parameter checkfullbus no

设置完成后使用如下命令来运行**“lint/lint_rtl”**分析:

% spyglass -project wb_subsystem.prj -goals lint/lint_rtl -batch

运行完成后在终端中查看结果如下:

在文件./wb_subsystem/wb_subsystem/lint/lint_rtl/spyglass_reports/moresimple.rpt中查看更为详细的报告:![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-axEYF7yy-1605094790078)(F:\VM_SHARE\synglass\18.jpg)]](https://img-blog.csdnimg.cn/20201111195232700.jpg?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMwODQzOTUz,size_16,color_FFFFFF,t_70#pic_center)

至此,通过该实验知道了如何运行Goal及如何查看报告信息。

5.实验四

在本练习中,我们将分析lint目标运行期间产生的违规。我们可以在SpyGlass GUI中使用各种调试工具来理解违规,在RTL代码中调试其根本原因,并查看如何在SpyGlass环境本身中修复这些违规。对于本实验,每次更改RTL或者.prj文件都需要重新运行目标以验证结果。实验流程按照Analyze Result选项卡中Run Goal框中显示的顺序进行。

通过下面命令进入GUI界面:

% spyglass –project wb_subsystem.prj &

在没有**-batch时候,SpyGlass默认打开GUI界面。之前设置的current_goal会自动加载执行。同时在运行Goal**同时会生成多个报告,不同报告提供不同信息,可在Report》More Report下查看。

在GUI底部的Violations可查看违规信息。在显示出违规信息后,点击违规信息窗口顶部的Group By,然后选择Goal by Rule。此字段确定批处理运行中的违规在消息树中的排序方式。本实验中违规信息显示如下:![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-Cv88JC1V-1605094790079)(F:\VM_SHARE\synglass\19.jpg)]](https://img-blog.csdnimg.cn/20201111195257707.jpg?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMwODQzOTUz,size_16,color_FFFFFF,t_70#pic_center)

5.1 W415错误

从消息窗口中可以看到违反规则W415的情况。该规则确定了在设计中可以由两个或更多非三态驱动器同时驱动的网络。展开后可以看到违规细节为:WB_master_data_o[31:0]在设计wb_subsystem的顶层中有多个同时非稳态驱动程序。接下来对该问题进行调试分析。

双击违规细节信息,违规信息将变成粗体,同时代码窗口将会跳转到有问题的代码行且高亮显示。如下图所示: ![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-wodDnOpu-1605094790079)(F:\VM_SHARE\synglass\20.jpg)]](https://img-blog.csdnimg.cn/2020111119532353.jpg?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMwODQzOTUz,size_16,color_FFFFFF,t_70#pic_center)

可以通过原理图获取更多违规细节。违规消息前面的![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-yJtRYcyO-1605094790080)(C:\Users\admin\AppData\Roaming\Typora\typora-user-images\image-20201111112831144.png)]](https://img-blog.csdnimg.cn/20201111195402677.jpg#pic_center)

指示该违规消息包含一些逻辑示意图数据方面的信息,单击![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-ePEvgQeA-1605094790081)(C:\Users\admin\AppData\Roaming\Typora\typora-user-images\image-20201111112956417.png)]](https://img-blog.csdnimg.cn/20201111195419749.jpg#pic_center)

打开原理图窗口,增量示意图窗口显示违规的结构:![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-U8Cy9tgn-1605094790081)(F:\VM_SHARE\synglass\21.jpg)]](https://img-blog.csdnimg.cn/20201111195436733.jpg?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMwODQzOTUz,size_16,color_FFFFFF,t_70#pic_center)

主窗口显示结构的细节,问题网用红色显示。模块边界以虚线显示,模块名称在底部,实例名称在每个模块边界的顶部。左侧底部窗口提供了带有红色缩放区域的逻辑示意图的整体视图–可以通过拖动红色区域的边缘/角落以及使用逻辑示意图边缘的滑动条来更改缩放比例。

可以看到两个驱动程序正在驱动报告的信号(WB_master_data_o[0]) 端口“m0_data_i”由端口“dat_o”(实例ahb2wb_u0)和“m0_data_o”(实例conmax_u1)同时驱动。因此,这是一个有效的违反。

通过将鼠标放在原理图对象(端口、网络、门、模块)上,然后右键》Cross Probe,实现从原理图到RTL的交叉探测。

通过查看RTL代码我们知道该部分使用ifdef构造来启用固定代码。让我们通过在wb_subsystem.prj的# #Common Option Section中添加以下内容来启用宏,从而启用Fix_W415宏:

set_option define { Fix_W415 }

设置后重新加载项目文件和重新运行Goal:File -> Reload Project -> Analyze Results -> Run Goal。在高版本中重新加载工程文件会自动完成。在本实验中此时不会有W415的错误。

5.2 SYNTH_5159警告

展开警告消息可以看到由内置规则SYNTH_5159报告的消息。

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-fhd95PO6-1605094790082)(F:\VM_SHARE\synglass\22.jpg)]](https://img-blog.csdnimg.cn/20201111195534853.jpg?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMwODQzOTUz,size_16,color_FFFFFF,t_70#pic_center)

规则SYNTH_5159识别可能不能综合的RTL结构。双击SYNTH_5159规则的消息,它将突出显示RTL中的错误。该语句包含在“synthesis”编译指令中,表示该语句不用于分析,但默认情况下,SpyGlass仅将“synopsys”和“pragma”注释识别为pragma(编译指令)。我们需要通过在项目文件中添加以下内容来启用“synthesis”的pragma处理:

set_option pragma { synopsys pragam synthesis}

所有设置都可以通过GUI中Design Setup的Set Options设置。

由于此错误发生在ima_adpcm_lib预编译库中,SpyGlass会检查该库的RTL是否已更改,只有在更改后才会重新编译,因此我们需要使用下面的指令删除现有的预编译库,以便使用新的pragma设置重新编译该库。手动删除ima_adpcm_lib的另一种方法是在.prj文件中临时添加“set_option force_compile yes”以强制重新编译库。

% rm -rf ima_adpcm_lib

保存修改后的项目文件后,将在图形用户界面中重新加载。删除预编译库后,重新运行目标(单击“Analyze Results”选项卡中的“Run Goal”),并验证SYNTH_5159违例是否消失。

5.3 UndrivenInTerm-ML错误

展开lint/lint_rtl报告消息,可以看到两个违反UndrivenInTerm-ML的错误消息。该规则识别浮动网(没有驱动程序但加载了)。该消息表明,实例“conmax_u1”的输入端口“m0_addr_i”的上半部分(31:16)范围是浮动的:![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-gVdO2cXb-1605094790082)(F:\VM_SHARE\synglass\23.jpg)]](https://img-blog.csdnimg.cn/2020111119555587.jpg?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMwODQzOTUz,size_16,color_FFFFFF,t_70#pic_center)

来对该错误进行具体分析:

(1)双击违规信息,它将高亮RTL代码中的第128行。高亮的行显示了端口“m0_addr_i”的端口映射,该端口映射带有地址信号“WB_master_addr”;

(2)在RTL窗口中选中通过双击选中WB_master_addr信号,然后右键》Signal:WB_master_addr:![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-8zXQZjM7-1605094790083)(F:\VM_SHARE\synglass\24.jpg)]](https://img-blog.csdnimg.cn/20201111195616954.jpg?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMwODQzOTUz,size_16,color_FFFFFF,t_70#pic_center)

折叠菜单显示声明、加载和驱动程序的多个超链接(蓝色)。点击蓝色字体,可以看到信号WB_master_addr的宽度为32位,与映射的实际端口m0_addr_i的宽度相同,即端口完全与位宽的信号总线相连,不是问题所在。接下来检查WB_master_addr的驱动器。

(3) View -> Windows -> HDL Navigator,可以看到被选中信号WB_master_addr的驱动和负载相关信息。可以注意到有一个驱动报告的信息:![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-NQEhfsFb-1605094790083)(F:\VM_SHARE\synglass\25.jpg)]](https://img-blog.csdnimg.cn/20201111195634621.jpg?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMwODQzOTUz,size_16,color_FFFFFF,t_70#pic_center)

驱动程序是实例“ahb2wb_u0”的o/p端口“adr_0”,但这仅驱动矢量号“WB_master_addr”的下半位(15:0),而其余位没有报告其他驱动程序,以确认上半位没有驱动程序。解决这一问题的方法是通过拼接算符将前16位与逻辑0绑定,并对RTL进行更新。

我们可以看到RTL中有通过拼接进行的驱动程序,但通过ifdef结构进行控制。因此可以通过设置Fix _ UndrivenInTerm宏来调用目标程序,像之前对W415所做的那样:

set_option define { Fix_UndrivenInTerm }

在.prj文件中添加上面的语句并保存。在重新加载工程文件后在Analyze Results点击Run Goal,然后查看报告以验证是否该错误得到结局。

5.4 Waiving 违规

在lint/lint_rtl报告中,还剩下3条错误严重性消息,是可能产生的非预期锁存结构。

展开规则文件夹,查看从信号hready推断的可能存在的锁存结构。使用RTL交叉探测,您可以看到信号hready在没有其他部分的if语句中被赋值。

假设这些锁存是有意的,那会希望下次检查时候可以跳过对这些锁存的检查,可以通过定义waivers来放弃对这些锁存的检查:鼠标在hready违规信息上》右键》Waive Selected Messages…

这将打开waivers编辑器窗口,并为其填充相关信息(违规消息、规则和设计单位(DU)):

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-LMGdsILb-1605094790084)(F:\VM_SHARE\synglass\26.jpg)]](https://img-blog.csdnimg.cn/20201111195655586.jpg?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMwODQzOTUz,size_16,color_FFFFFF,t_70#pic_center)

放弃检查声明以蓝色突出显示(2016.06+版本为绿色)-每个字段都可以在窗口的下半部分进行编辑。可以在Comments字段中添加放弃的原因。做出任何更改后,单击Apply。现在可以看到只显示了两个冲突。

在界面底部选择Waiver Tree可以查看已经被过过滤掉的错误选项。如果没有可以通过View -> Windows -> Waiver Tree打开。

可以将Waiver设置保存为文件然后重复使用:在waivers编辑器窗口中右键点击左侧面板中文件,然后选择Save Waiver Files。

SpyGlass会为每个Goal保存一个关于检查过滤的文件,本例中文件路径为:

./wb_subsystem/wb_subsystem/lint/lint_rtl/wb_subsystem_waiver_file.awl

我们可以将其复制到当前工作目录下,方便调用:

cp ./wb_subsystem/wb_subsystem/lint/lint_rtl/wb_subsystem_waiver_file.awl ./wb_subsystem.awl

然后将该过滤文件包含到工程中并将其设置为默认waiver 文件:

read_file -type awl ./wb_subsystem.awl

set_option default_waiver_file ./wb_subsystem.awl

然后重新加载工程文件且运行Goal。

6.生成结果报表

报表内容为运行的Goal的分析结果。有的功能需要使用SpyGlass的组件完成,如果具有相应的License则会将相应的运行结果包含在报表中。报表包括datasheet 和dashboard 。

在GUI界面下打开shell命令窗口,输入如下命令生成报表:

sg_shell> write_aggregate_report datasheet

sg_shell> write_aggregate_report dashboard

数据表和仪表板报告提供了在移交的设计中看到的结果的摘要。

通过在终端中输入下面命令可以在浏览器中查看报告

firefox wb_subsystem/html_reports/dashboard.html

firefox wb_subsystem/html_reports/datasheet.html

下面两张图为报表示例:

DashBoard:![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-TOsFGGO8-1605094790085)(F:\VM_SHARE\synglass\27.jpg)]](https://img-blog.csdnimg.cn/20201111195731192.jpg?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMwODQzOTUz,size_16,color_FFFFFF,t_70#pic_center)

DataBoard:![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-jIqHjnB8-1605094790085)(F:\VM_SHARE\synglass\28.jpg)]](https://img-blog.csdnimg.cn/20201111195746958.jpg?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMwODQzOTUz,size_16,color_FFFFFF,t_70#pic_center)

最终结束语

本人研二在读,因为热爱,所以不知疲倦。这是自己学习中做的总结,也为了给需要的人分享,所以写了这篇文档。这是自己写的第一篇文档,有不足欢迎交流指正。QQ:2562074834