输入输出

8086采用I/O端口独立编址

in AL/AX,imm8/DX

out imm8/DX,AL/AX

大于0FFH的端口只能存在DX

读外设(查询)

status:in al,dx

test al,80H;//测标志位

jz status

mov dx,100h

in al,dx

写外设(查询)

status:mov dx,102H

in al,dx

test al,80H

jnz status;//D7=1,忙,继续查

mov dx,100h

mov al,char

out dx,al

74LS273:锁存。输出锁存寄存器。

74LS244:缓冲。输入缓冲,输出锁存。

A 0 A_0 A0=0, R D ‾ = 1 \overline{RD}=1 RD=1,读IRR、ISR、查询自

A 0 A_0 A0=1, R D ‾ = 0 \overline{RD}=0 RD=0,读IMR

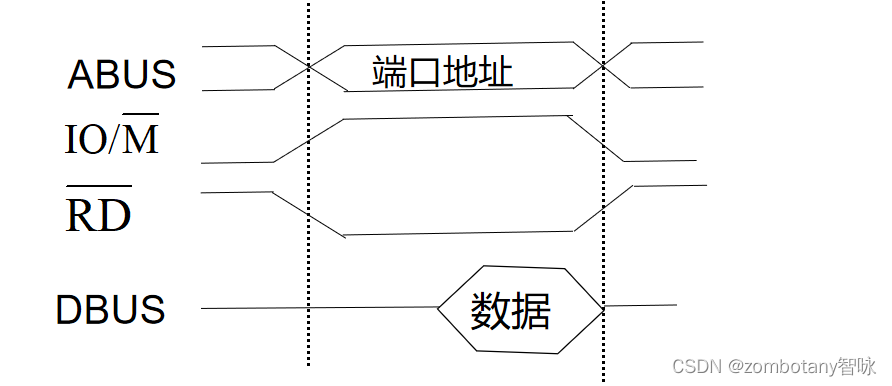

输入时序

输出时序

选通信号Ready将置1,状态口连在 D 7 D_7 D7上,选通信号置Ready

中断与8259

传送指令装入中断向量。

mov ax,0

mov es,ax

mov bx,N*4;//N为中断类型号

mov ax,offset intproc

mov es:[bx],ax

mov ax,seg intporc

mov es:[bx+2],ax

sti

内部中断:除法错误、溢出、指令单步、断点。

外部中断:NMI、INTR(高电平有效)。NMI类型号为2,边沿触发。

关中断情况:系统复位、中断被响应、CLI。

一条指令的结束是相应NMI的必要条件

普通屏蔽:IMR的 D i D_i Di为1,对应 I R i IR_i IRi屏蔽。

特殊屏蔽: I R i IR_i IRi被屏蔽时, I S R i ISR_i ISRi为0

中断结束: I S R ISR ISR某位为0

EOI:非自动中断结束,全嵌套清楚优先级最高位。

特殊:配合循环优先权,发EOI清楚ISR对应位。

缓冲:多片级联。非缓冲:单片。

IRR中断请求寄存器,1表示对应位有请求,响应后复位。

IMR中断屏蔽寄存器,0表示允许中断

ISR中断服务寄存器,1表示在被服务

PR优先级判别。

优先级固定方式:从高到低为 I R 0 IR_0 IR0, I R 1 IR_1 IR1,… I R 7 IR_7 IR7,完全嵌套

自动循环:初始 I R 0 , . . . , I R 7 IR_0,...,IR_7 IR0,...,IR7, I R i IR_i IRi被服务后, I R i IR_i IRi最低, I R i + 1 m o d 8 IR_{i+1\mod 8} IRi+1mod8最高

特殊循环:可设置初始最低优先级

普通全嵌套:禁止同级/低级优先权中断

特殊全嵌套:禁止低级中断,在主片。

S P ‾ / E N ‾ \overline{SP}/\overline{EN} SP/EN级联方式:主片 S P ‾ = 1 \overline {SP}=1 SP=1,从片 S P ‾ = 0 \overline{SP}=0 SP=0

I R 0 . . . I R 7 IR_0...IR_7 IR0...IR7中断请求。

C A S 0 . . . C A S 7 CAS_0...CAS_7 CAS0...CAS7级联引脚双相

C A S 2 . . . C A S 0 CAS_2...CAS_0 CAS2...CAS0:主片输出、从片输入、级联信号

例如

A 0 = 0 , W R ‾ = 0 A_0=0,\overline{WR}=0 A0=0,WR=0,写 I C W 1 , O C W 2 , O C W 3 ICW_1,OCW_2,OCW_3 ICW1,OCW2,OCW3.

A 0 = 1 , W R ‾ = 0 A_0=1,\overline{WR}=0 A0=1,WR=0,写 I C W 2 − I C W 4 , O C W 1 ICW_2-ICW_4,OCW_1 ICW2−ICW4,OCW1

O C W 1 OCW_1 OCW1:中断屏蔽字寄存器,写

in al,81H

and al,11111101B;IR1开放中断

out 81H,al

O C W 2 OCW_2 OCW2:优先级循环方式和发中断结束命令

EOI=1发中断结束,清除相应位

O C W 3 OCW_3 OCW3:查询字

mov al,0AH;读IRR的OCW3

out 20H,al

in al,20H;读IRR到AL

中断服务子程序整体流程:保护现场、开中断、中断处理、关中断、恢复现场、中断返回。

intproc proc far

push ax

push ds

sti

mov ax,seg done

mov ds,ax

in al,0a0h;读开关状态

out 0c0h,al;输出控制led

cmp al,0ffh

jnz exit

int al,82h;中断屏蔽

or al,00000100B

out 82h,al

exit:

cli

mov al,20H;EOI

out 80H,al

pop ds

pop ax

iret

intproc endp

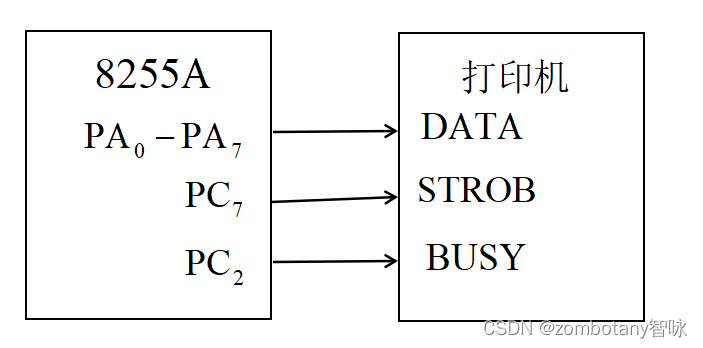

8255

D 0 − D 7 D_0-D_7 D0−D7数据线, A 0 − A 1 A_0-A_1 A0−A1地址, C S ‾ \overline{CS} CS片选, P A 0 − P A 7 PA_0-PA_7 PA0−PA7, P B 0 − P B 7 PB_0-PB_7 PB0−PB7, P C 0 − P C 7 PC_0-PC_7 PC0−PC7

A组:A口、C口高4位。B组:B口、C口低4位。

方式0:无条件/查询。

方式1/2:查询、中断

输入时,8255为数据缓冲。输出时,8255为数据锁存。可知已准备好数据。

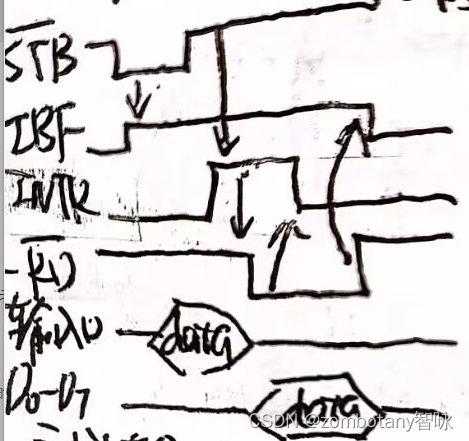

方式1输入: S T B ‾ \overline{STB} STB选通(外设准备好数据,将数据锁存、输入)

IBF:输入缓冲区满则,输出

I N T R A INTR_A INTRA:中断请求,输出。

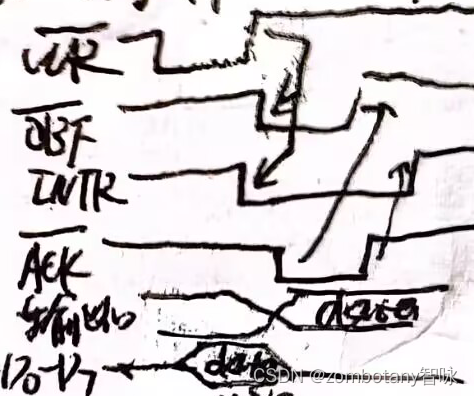

方式1输出: O B F ‾ \overline{OBF} OBF输入缓冲器满,可取走。

A C K ‾ \overline{ACK} ACK:外设响应,输入,低有效。

I N T R INTR INTR:中断请求,输出。

方式1输出时 O B F ‾ \overline{OBF} OBF有效时输出,外设接受后回送 A C K ‾ \overline{ACK} ACK。

方式2时外设提供 A C K ‾ \overline{ACK} ACK后输出数据

| 短口 | P C i PC_i PCi | 输入 | 输出 |

|---|---|---|---|

| A端口 | P C 7 PC_7 PC7 | O B F ‾ \overline{OBF} OBF | |

| A端口 | P C 6 PC_6 PC6 | A C K A ‾ / I N T E A \overline{ACK_A}/INTE_A ACKA/INTEA | |

| A端口 | P C 5 PC_5 PC5 | I B F A IBF_A IBFA | |

| A端口 | P C 4 PC_4 PC4 | S T B A ‾ / I N T E A \overline{STB_A}/INTE_A STBA/INTEA | |

| A端口 | P C 3 PC_3 PC3 | I N T R A INTR_A INTRA | I N T R A INTR_A INTRA |

| B端口 | P C 2 PC_2 PC2 | S T B B ‾ / I N T E B \overline{STB_B}/INTE_B STBB/INTEB | A C K B ‾ / I N T E B \overline{ACK_B}/INTE_B ACKB/INTEB |

| B端口 | P C 1 PC_1 PC1 | I B F B IBF_B IBFB | O B F B ‾ \overline{OBF_B} OBFB |

| B端口 | P C 0 PC_0 PC0 | I N T R B INTR_B INTRB | I N T R B INTR_B INTRB |

输入时序图

输出时序图

方式控制字

| D 7 D_7 D7 | D 6 D_6 D6 | D 5 D_5 D5 | D 4 D_4 D4 | D 3 D_3 D3 | D 2 D_2 D2 | D 1 D_1 D1 | D 0 D_0 D0 |

|---|---|---|---|---|---|---|---|

| 1 | A方式高位 | A方式低位 | A输入输出 | P C 7 − P C 4 PC_7-PC_4 PC7−PC4输入输出 | B方式 | B输入输出 | P C 3 − P C 0 PC_3-PC_0 PC3−PC0输入输出 |

其中,0表示输出,1表示输入。

C口位控制字

| D 7 D_7 D7 | D 6 D_6 D6 | D 5 D_5 D5 | D 4 D_4 D4 | D 3 D_3 D3 | D 2 D_2 D2 | D 1 D_1 D1 | D 0 D_0 D0 |

|---|---|---|---|---|---|---|---|

| 0 | 无意义 | 无意义 | 无意义 | 选位 | 选位 | 选位 | 清零/置1 |

例:

mov dx,303H

mov al,81H

out dx,al

mov al,0FH

out dx,al;(PC7=1)

prn:

mov dx,302H

in al,dx

test al,04h

jz prn;//查询输入

mov dx,300H;A口

mov al,ah;//ah=打印数据

out dx,al

mov dx,303H

mov al,0eH;STB#=0

out dx,al

nop

nop

mov al,0FH;STB#=1

out dx,al

8254/8253奇数骑

8254每个奇数骑内都有个计数单元、初值寄存器、输出锁存器。GATE控制奇数骑工作。

工作过程:设定工作方式、计数初值、硬件启动,计数初值送入奇数骑、每个clk使得奇数骑-1、计数结束。

方式2/3连续计数,GATE高电平计数,上升沿重新计数。

方式0/4由软件启动(重写计数初值)。1/5硬件启动(GATE上升沿),0/4在高电平计数。

out初始值:方式0在写控制后变低,其余变高。

方式1输出N个CLK负脉冲,方式5输出1个CLK负脉冲(与2/4波形相同,N-1高,1低)。

方式3:若计数值为偶数,输出 N 2 \frac N2 2N个clk高电平和低电平。若计数值为奇数,输出 N + 1 2 \frac{N+1}2 2N+1个高电平和 N − 1 2 \frac{N-1}2 2N−1个低电平。

方式0:计数结束中断。1:可编程硬件触发单稳负脉冲发生器

方式2:速率发生器。3:方波速率发生器。4:软件触发选通信号发生。5:硬件选通发生。

读出控制字:只有8254有,8253没有。

| D 7 D_7 D7 | D 6 D_6 D6 | D 5 D_5 D5 | D 4 D_4 D4 | D 3 D_3 D3 | D 2 D_2 D2 | D 1 D_1 D1 | 0 | |

|---|---|---|---|---|---|---|---|---|

| 读出控制字 | 1 | 1 | 0:锁存计数值 | 0:锁存状态 | 1:2# | 1:1# | 1:0# | 0 |

| 状态字 | OUT | isNULL | 读写格式 | 读写格式 | 工作方式 | 工作方式 | 工作方式 | 进制 |

输入时钟信号频率 F c l k F_{clk} Fclk,周期 T c l k T_{clk} Tclk,输出频率 F o u t F_{out} Fout,周期 T o u t T_{out} Tout

则 T o u t = T c l k N T_{out}=T_{clk}N Tout=TclkN, N = F c l k F o u t N=\frac{F_{clk}}{F_{out}} N=FoutFclk,先写控制字,再写初值

某工厂计件系统,装一个零件产生一个脉冲接 C L K 0 CLK_0 CLK0,装100个后扬声器发声,则奇数骑0方式0,奇数骑1在方式3。

mov al,10H

mov dx,PORT_CTRL

out dx,al

mov al,100

mov dx,PORT_0

out dx,al

mov al,76H

mov dx,PORT_CTRL

out dx,al

mov ax,2000

mov dx,PORT_1

out dx,al

mov al,ah;写高8位

out dx,al

数字信号与模拟信号

单极性电压输出: V o u t = ( − D / ( 2 8 ) ) ∗ V R E F V_{out}=(-D/(2^8))*V_{REF} Vout=(−D/(28))∗VREF

双极性电压输出: V o u t = D − 2 7 2 7 ∗ V R E F V_{out}=\frac{D-2^7}{2^7}*V_{REF} Vout=27D−27∗VREF

正负范围-5~5

ILE:数据输入,锁存允许

C S ‾ \overline{CS} CS:片选

W R 1 ‾ \overline{WR_1} WR1:写数据

X F E R ‾ \overline {X_{FER}} XFER数据传送控制

W R 2 ‾ \overline{WR_2} WR2:第二级写。当 X F E R ‾ = W R 2 ‾ = 0 \overline{X_{FER}}=\overline{WR_2}=0 XFER=WR2=0,开始转换

L E 1 = L E 2 = 1 LE_1=LE_2=1 LE1=LE2=1直通,否则缓冲。 I o u t I_{out} Iout输出电压

双缓冲控制:

mov dx,portx

out dx,xdata

mov dx,porty

out dx,ydata

mov ax,portcon

out dx,al

call delay

读8路电压转换

lea di,buf

mov cx,8

mov dx,300

convert:

out dx,al;启动转换

push dx

mov dx,310H

state:

in al,dx;读EOC

test al,20H;D5(EOC)为1?

jz state

pop dx

in al,dx;读取结果

mov [di],al

add dx,2;下一模拟通道

add di,2

loop convert

0832锯齿波

N = V i n − V R E F − V R E F + − V R E F − ∗ 2 8 N=\frac{V_{in}-V^-_{REF}}{V^+_{REF}-V^-_{REF}}*2^8 N=VREF+−VREF−Vin−VREF−∗28

mov dx,330H

mov al,00H

aga:

out dx,al

call delay

inc al

jmp aga

delay proc

push cx

mov cx,10

loop $

pop cx

ret

delay endp