QuartusⅡ 13.1 安装

一、下载

正点原子百度云:https://pan.baidu.com/s/1a9d-bq9RZmWrRV542X4IEA

提取码:

ifte

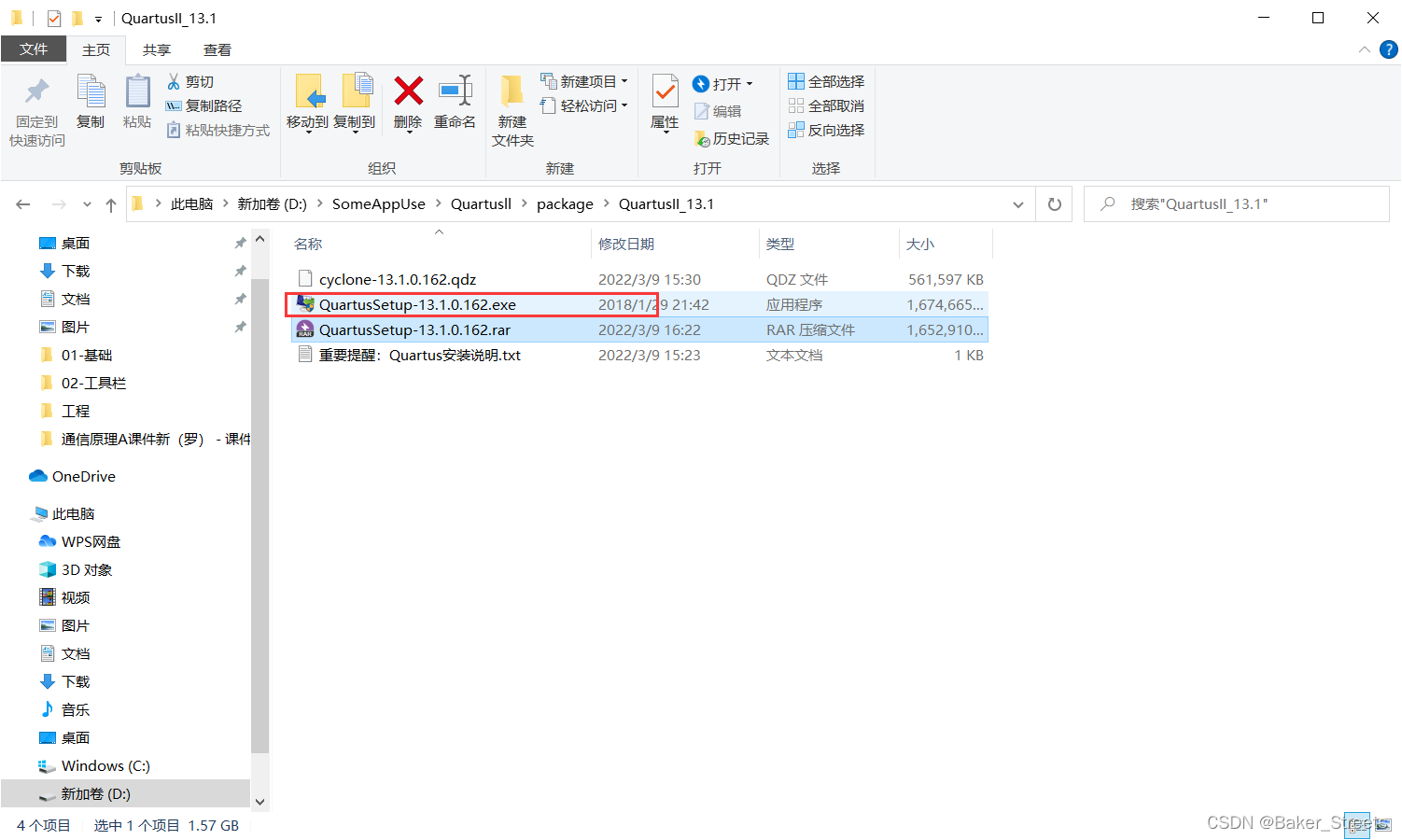

二、安装

解压后,双击安装:

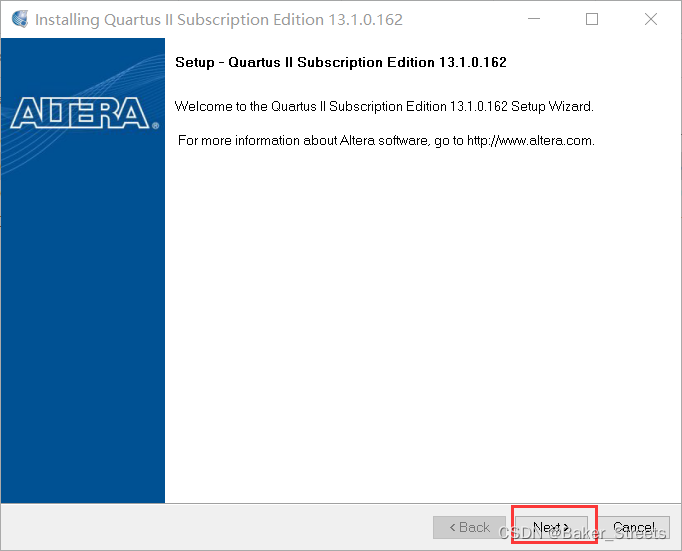

Next:

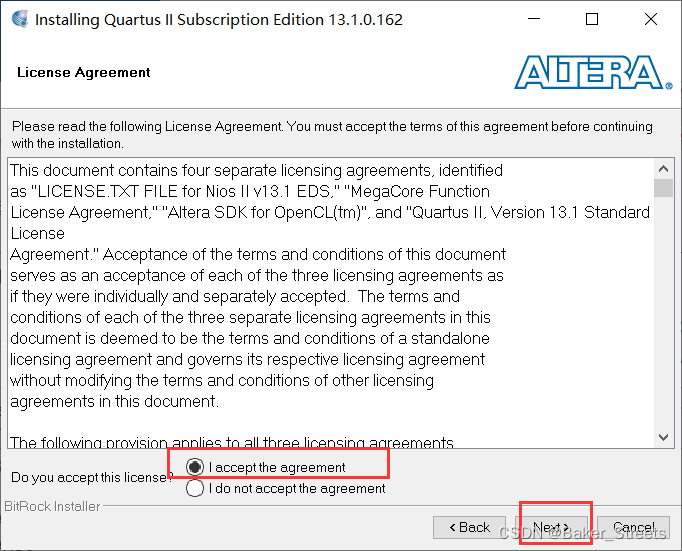

accept,Next:

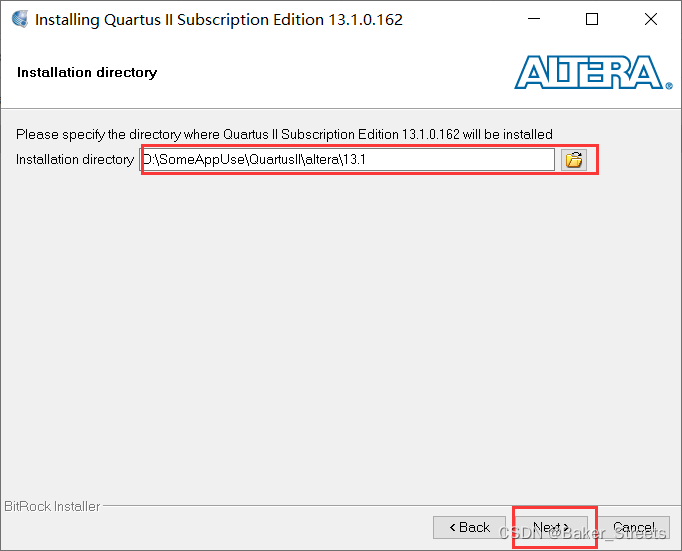

选择安装位置,Next:

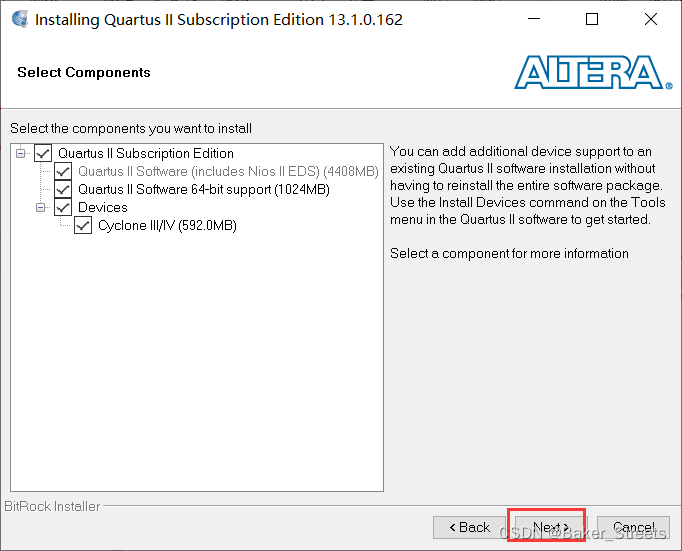

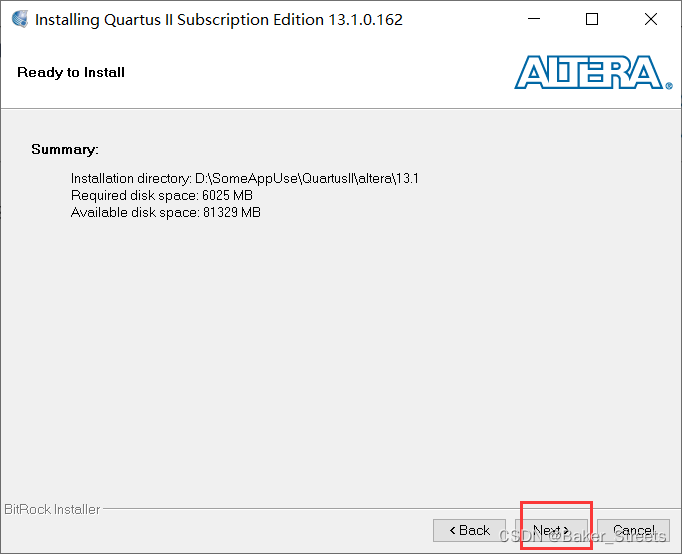

Next:

Next:

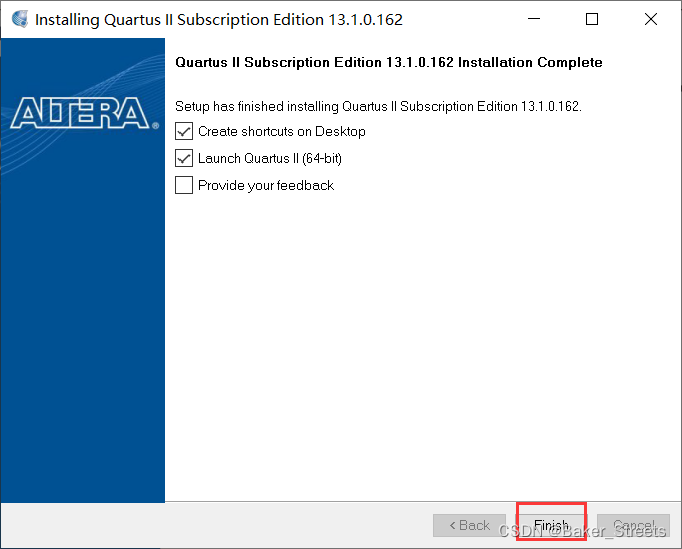

Finish:

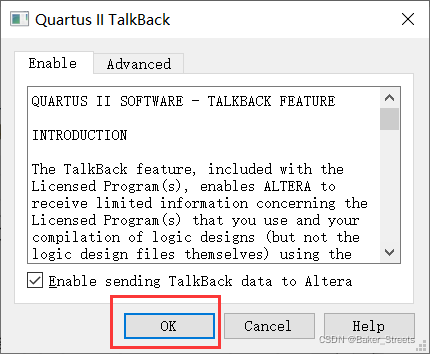

OK:

三、注册及驱动安装

注册文件:

https://pan.baidu.com/s/16GnGbr4v-EFKF0VZYUArsg

提取码:

766d

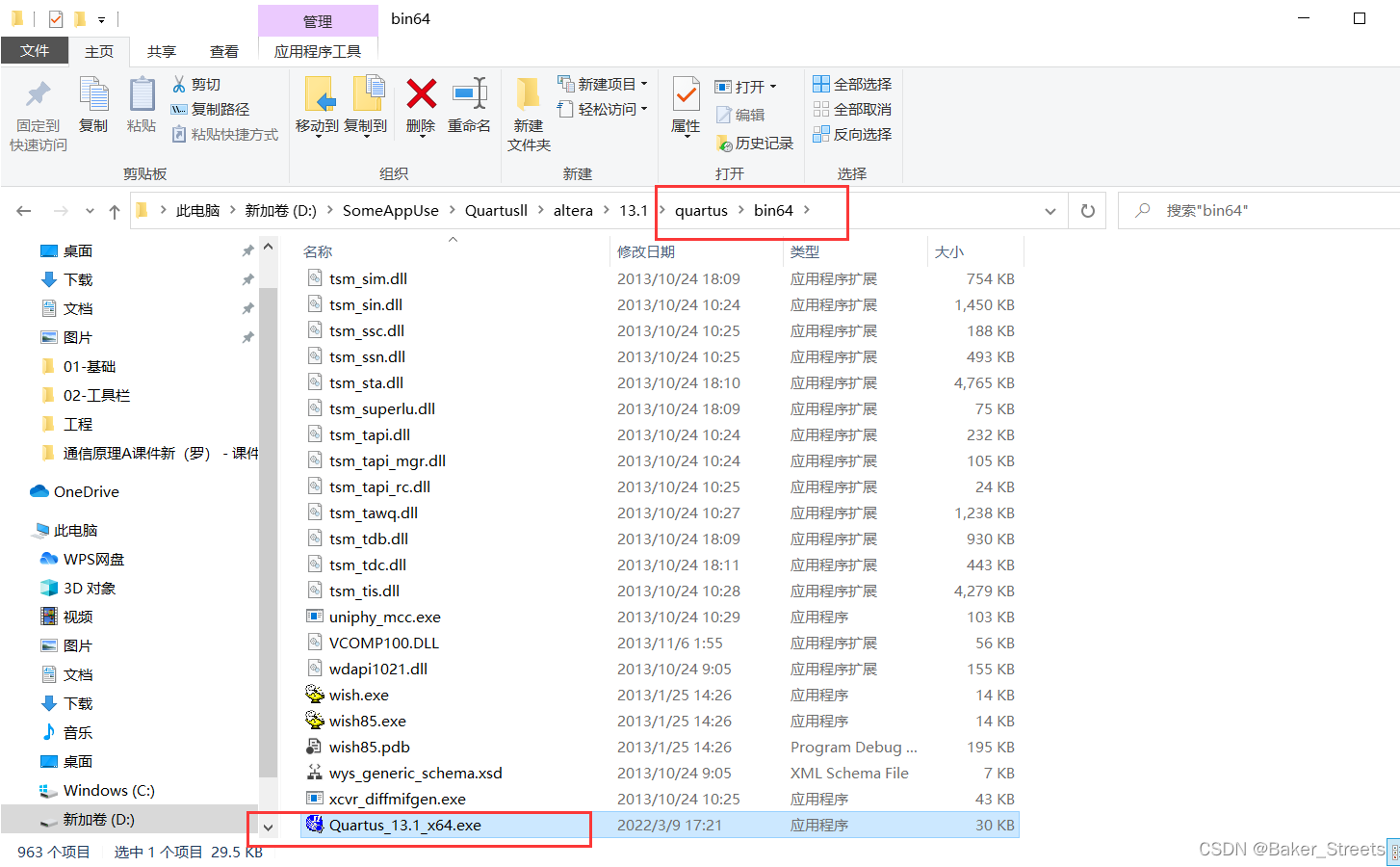

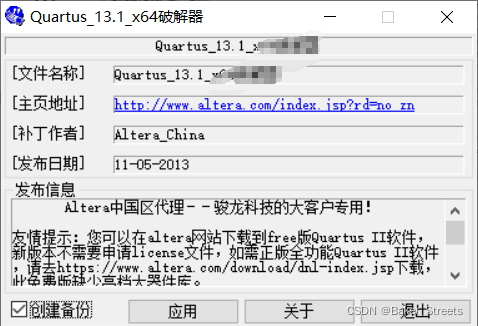

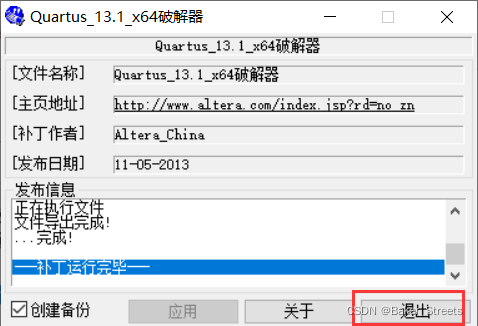

将下载的注册器Quartus_13.1_x64.exe 文件放在Quartus-ll安装路径 ..\quartus\bin64 下,并双击执行:

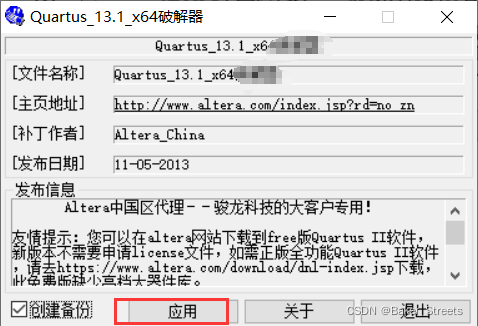

应用:

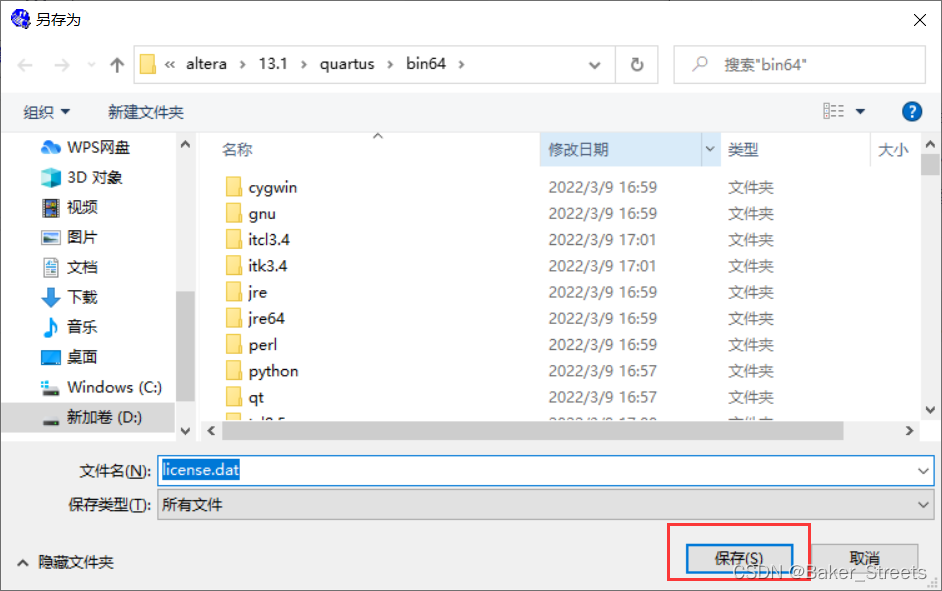

保存:

退出:

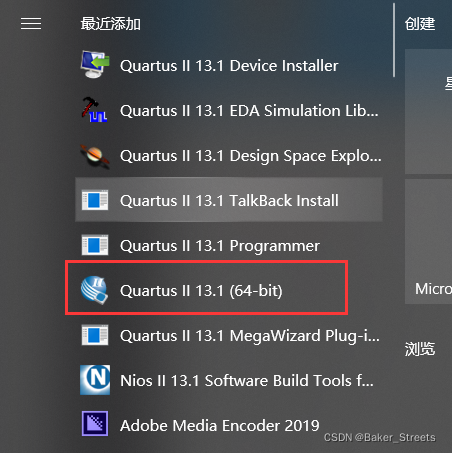

打开软件:

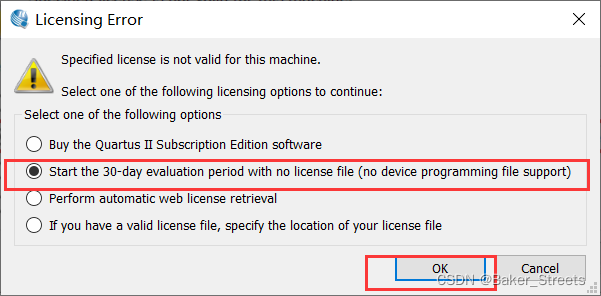

选择第二个,OK:

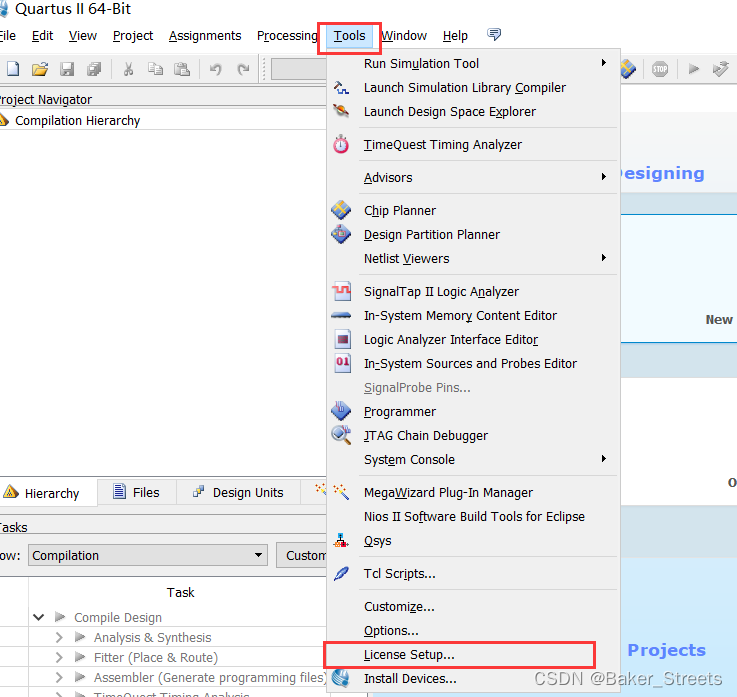

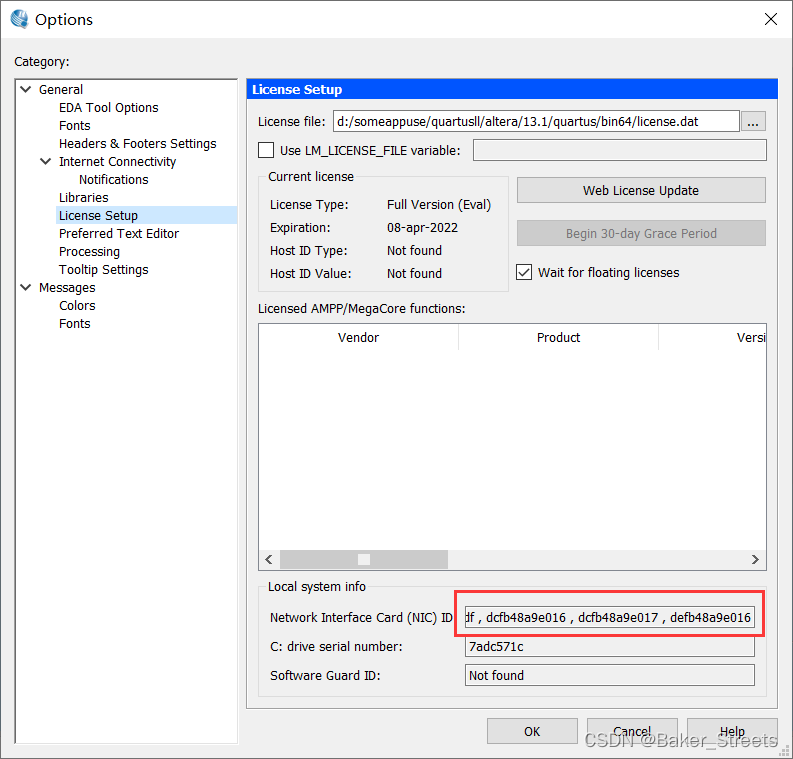

点击Tools下的License Setup…:

随便复制一个NIC:

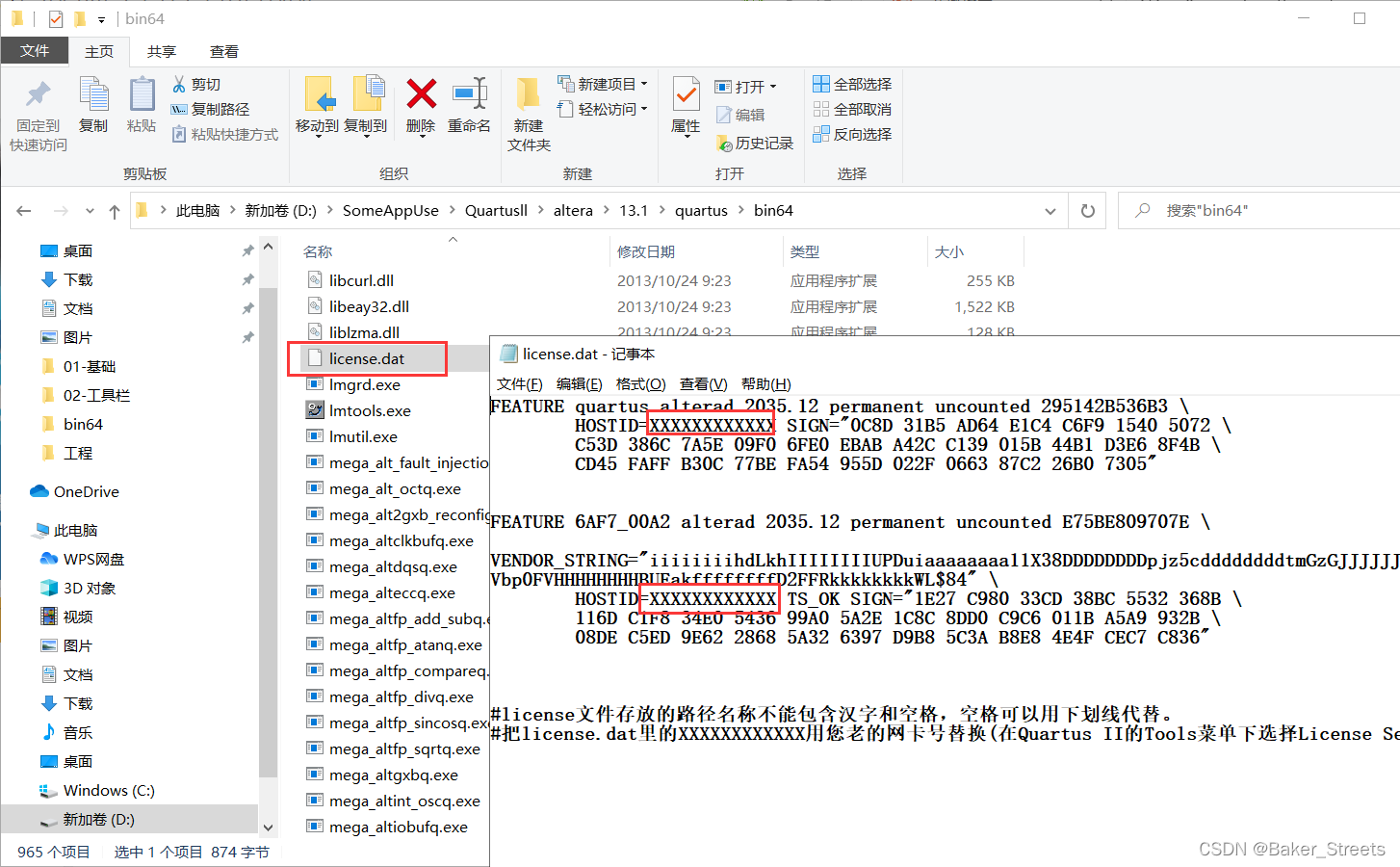

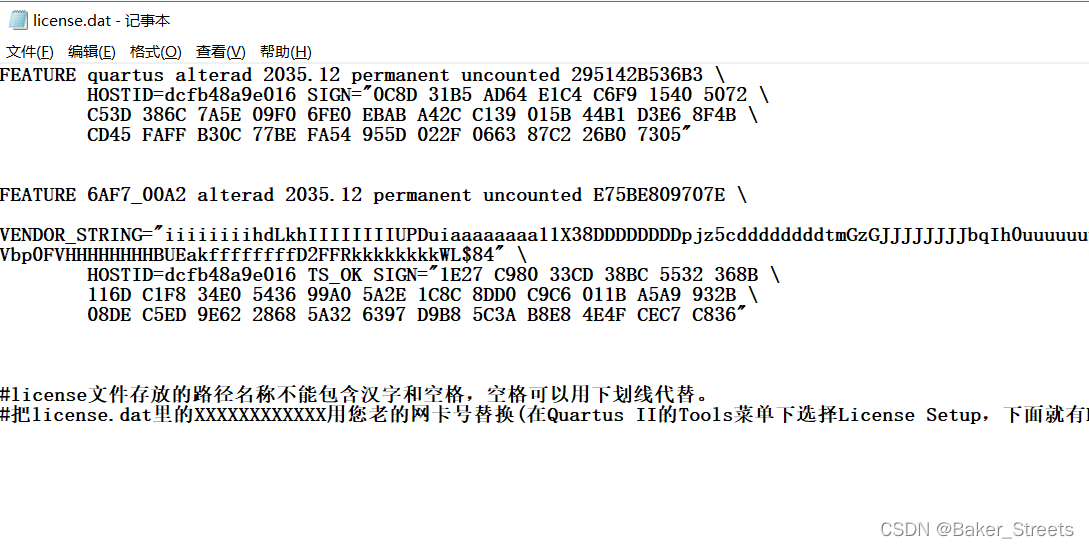

替换掉license.dat中的XXXXXXXXXXXX:

替换后:

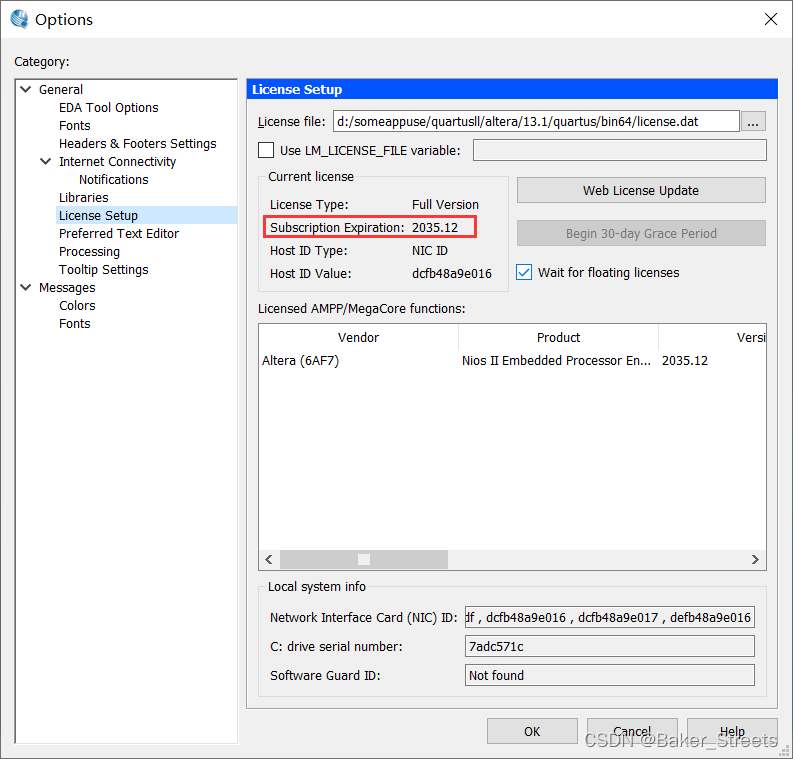

重新打开软件,发现日期已改变:

将 USB 线一端连接下载器,另一段插到电脑的 USB 接口上。

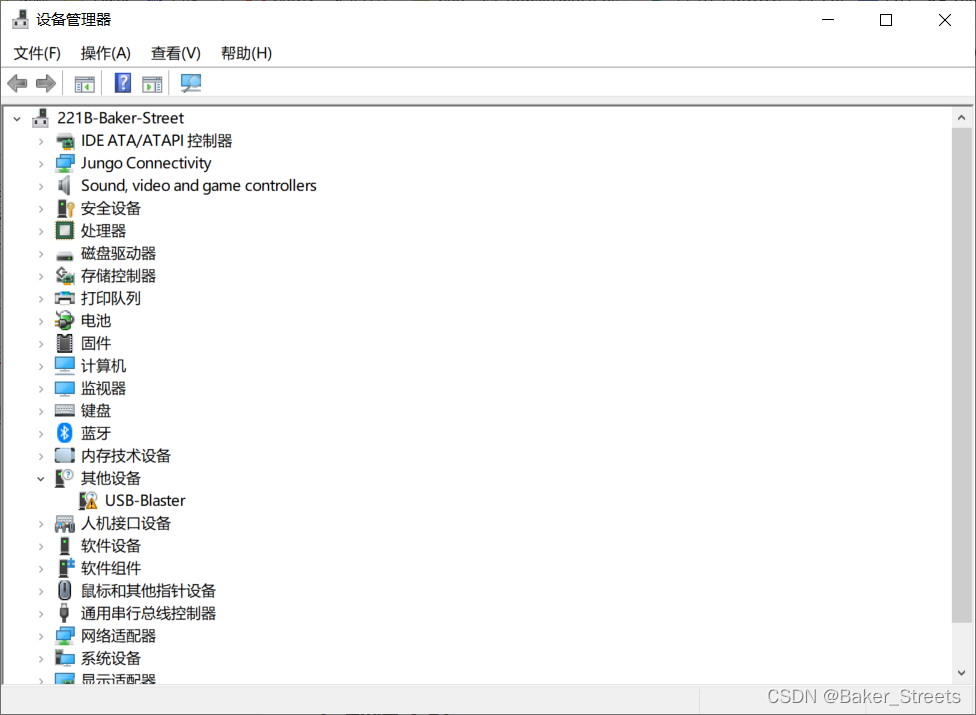

打开设备管理器:

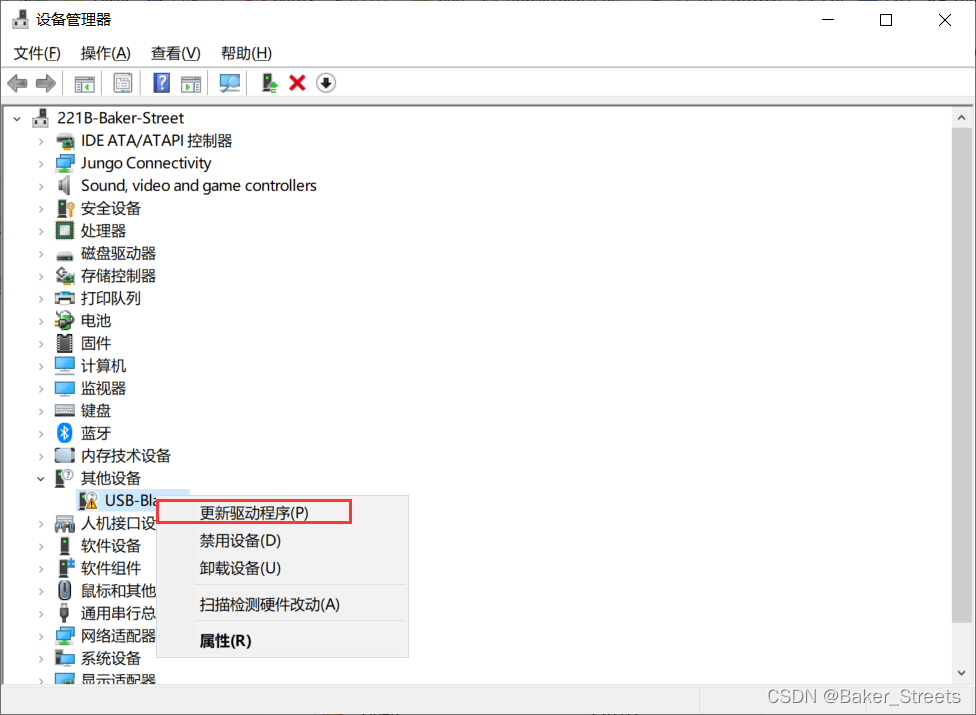

右击USB-Blaster,更新驱动程序软件:

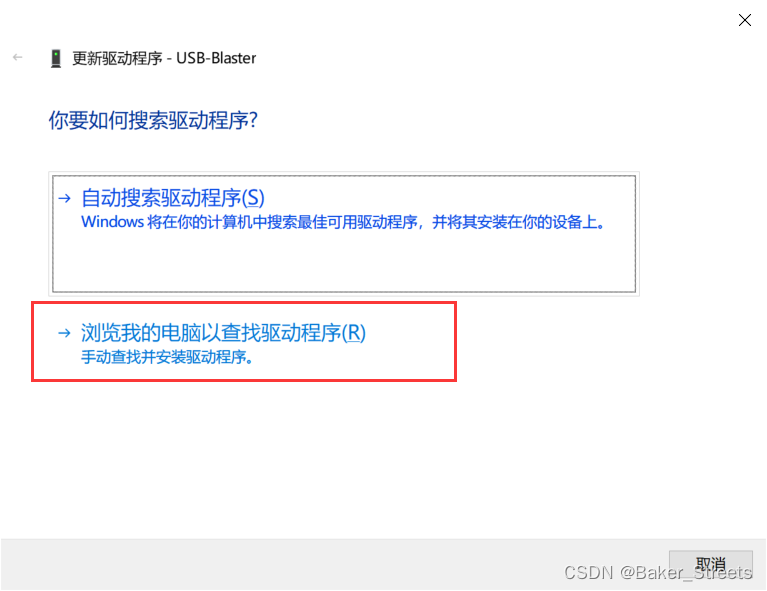

浏览我的计算机以查找驱动程序软件:

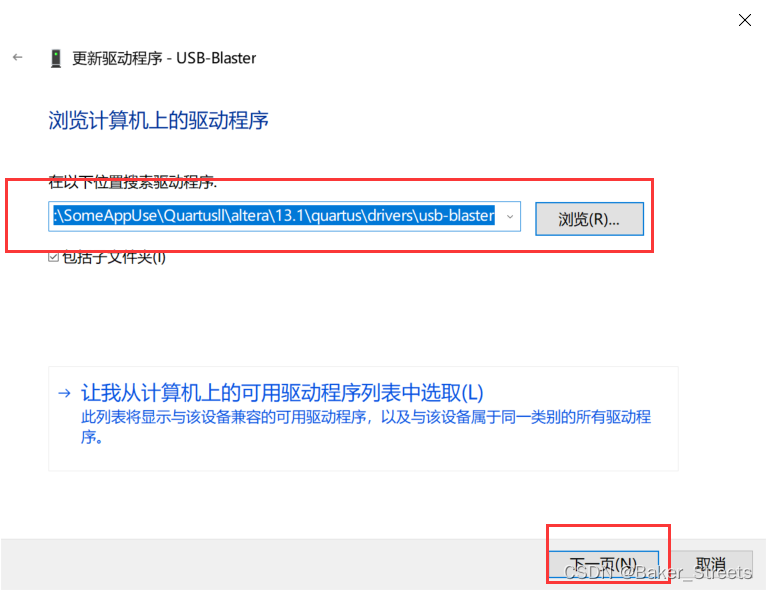

选择...\qurtus\drivers\usb-blaster,下一步:

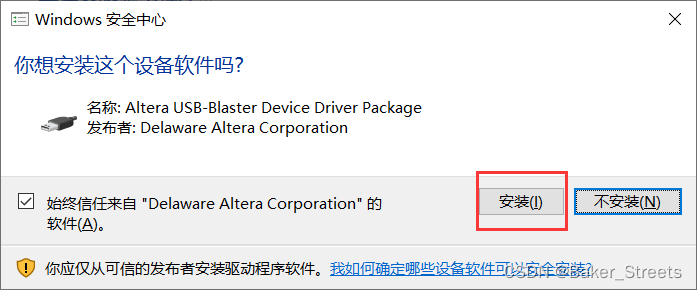

安装:

安装成功:

四、使用

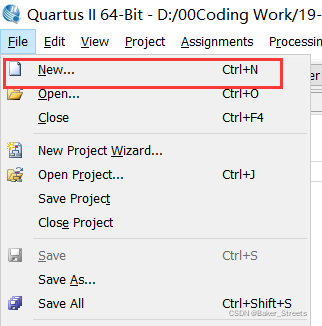

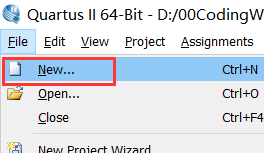

1. 新建工程

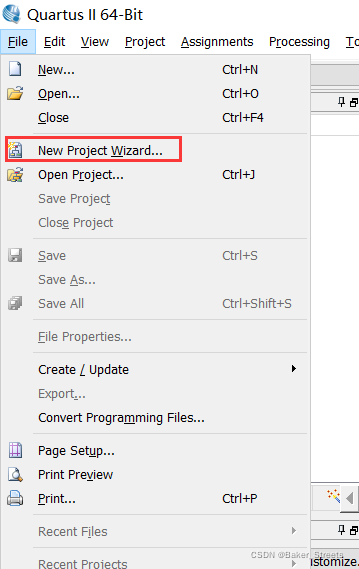

新建:

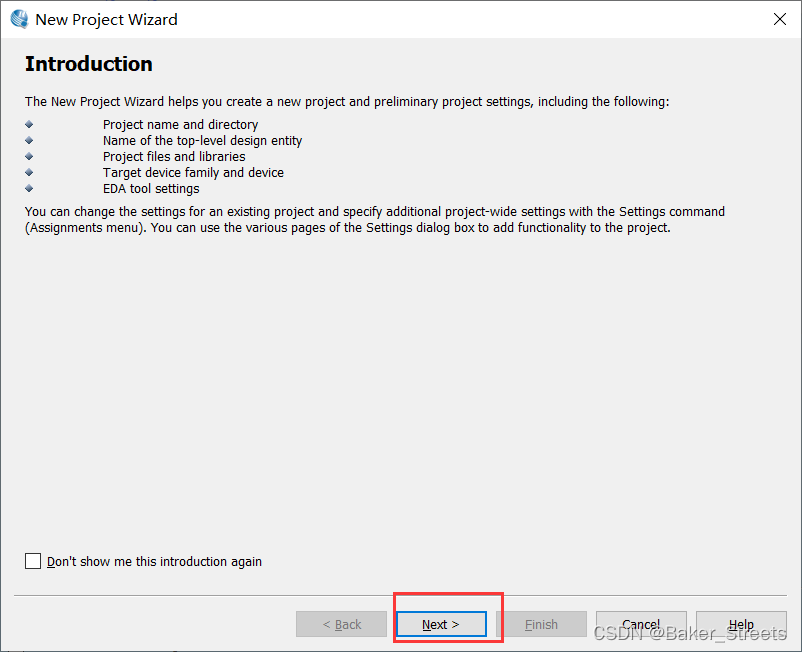

Next:

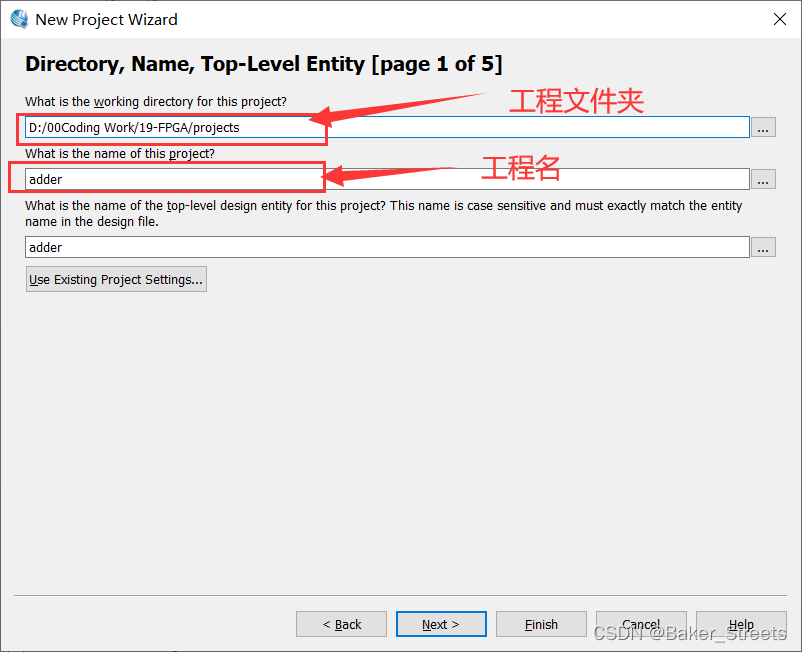

填写工程目录和工程名,Next:

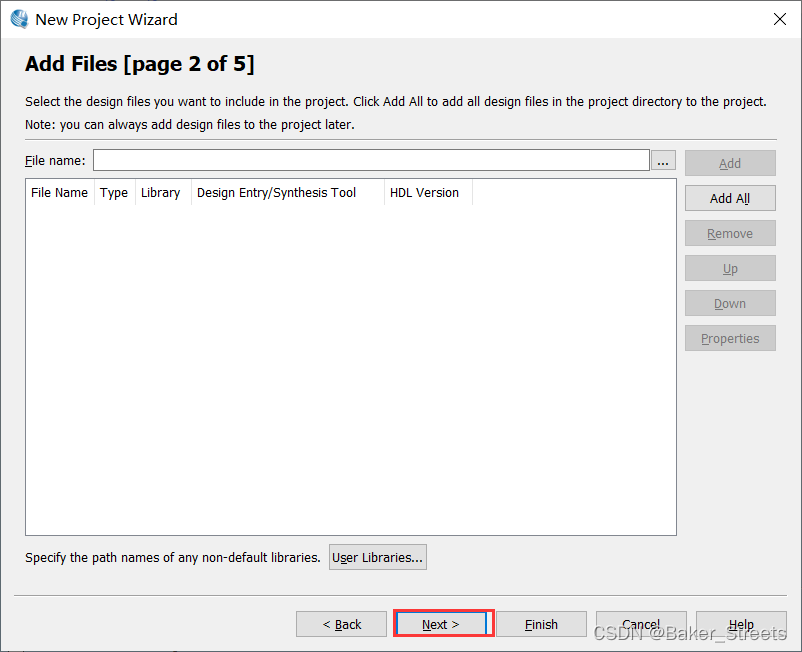

不需要添加已有的工程设计文件,直接Next:

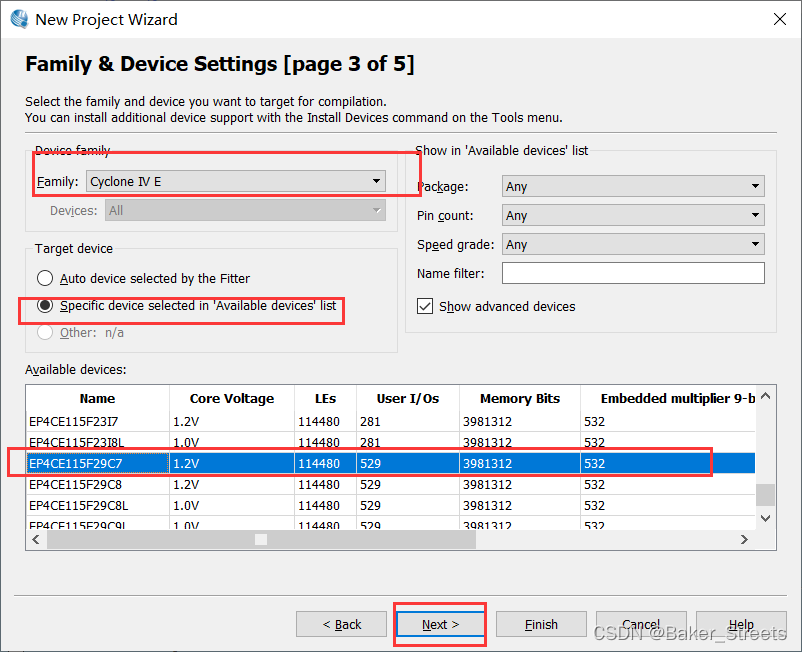

选择对应的芯片,Next:

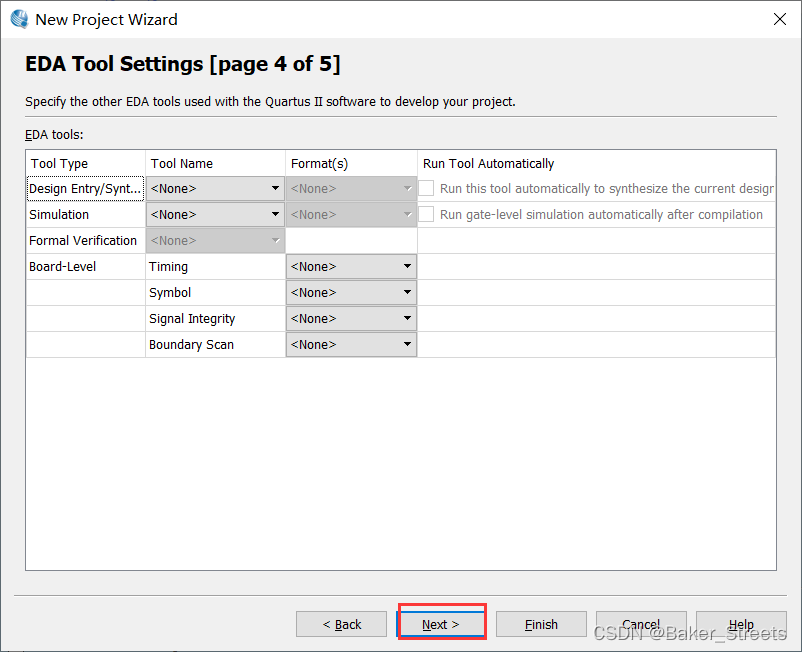

Next:

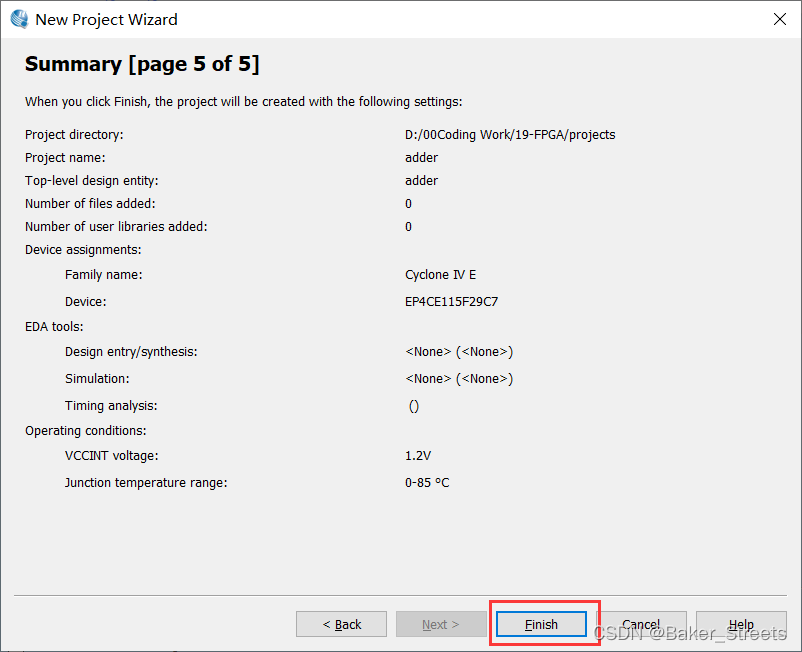

Finish:

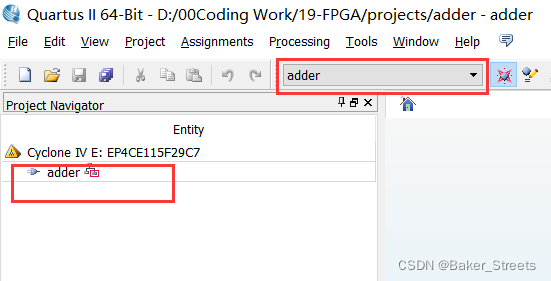

创建成功:

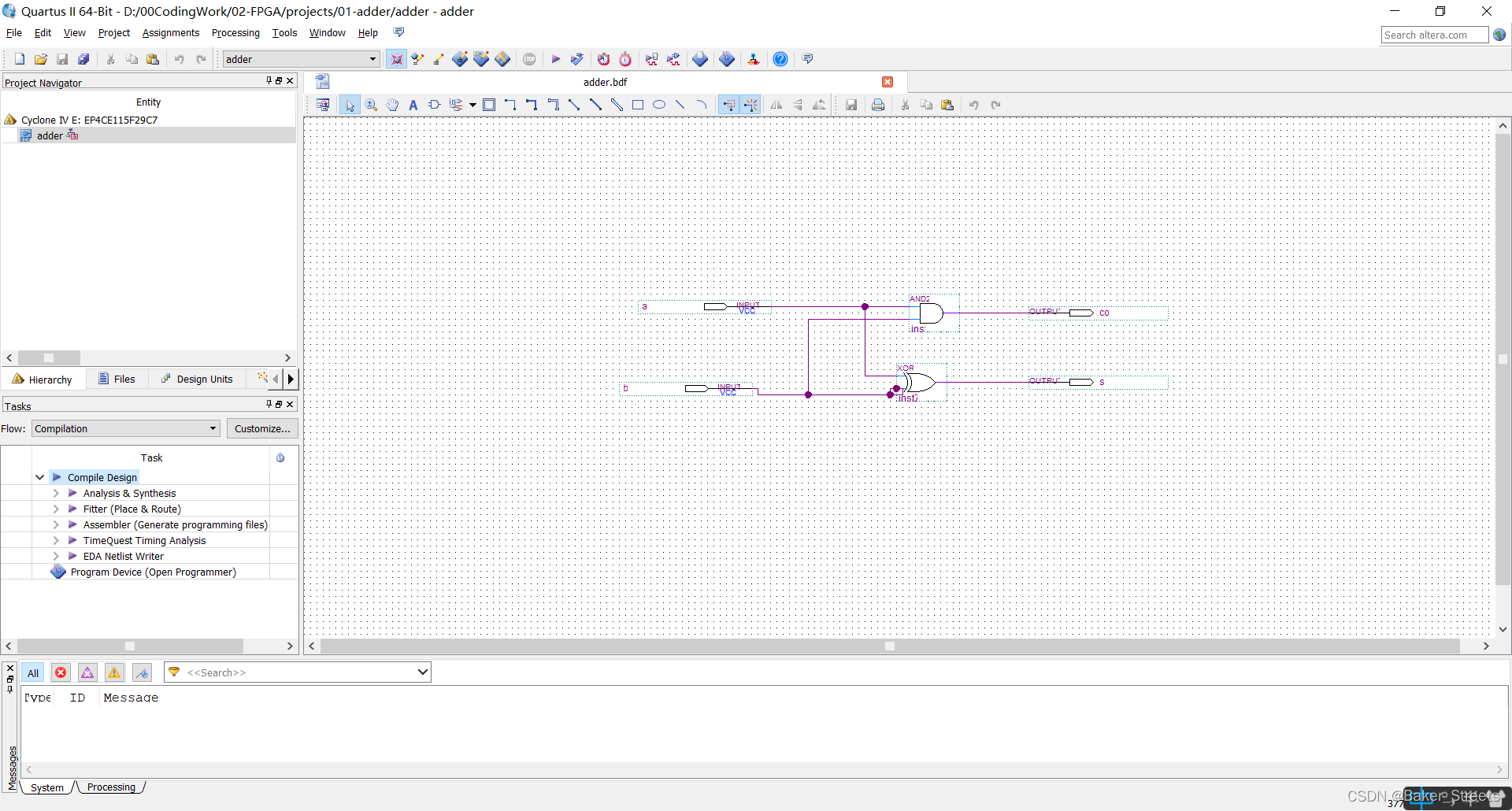

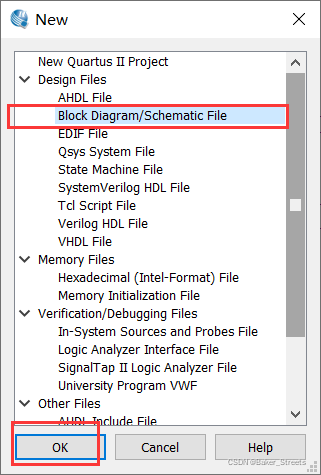

2. 新建原理图文件

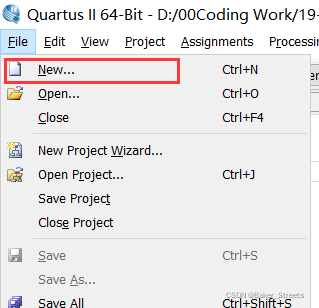

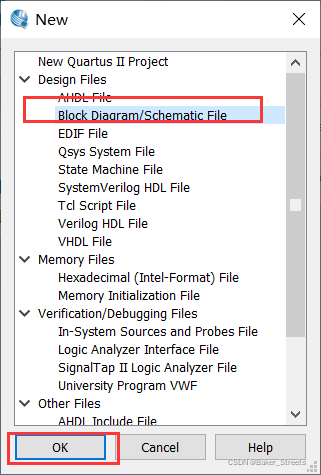

选择Block Diagram/Schematic File,OK:

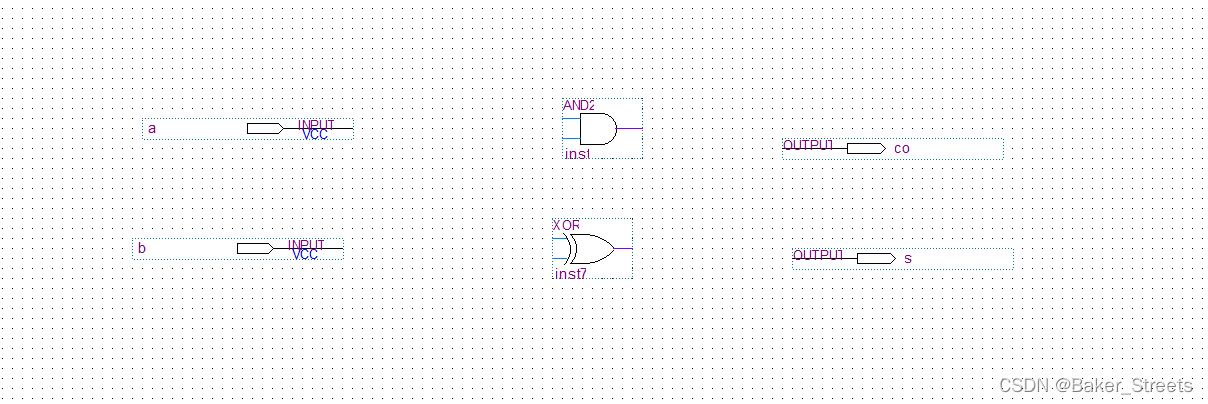

点击插头图标,搜索元件,然后在图纸上摆放:

- 1 个 and2

- 1 个 xor

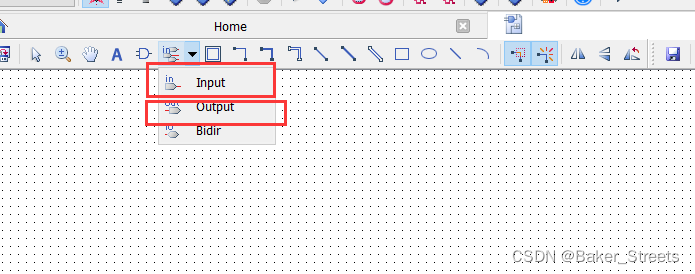

添加两个输入管脚和两个输出管脚,双击 Pin Name 即可修改管脚名,将输入管脚命名为a和b,将输出管脚命名为co和s :

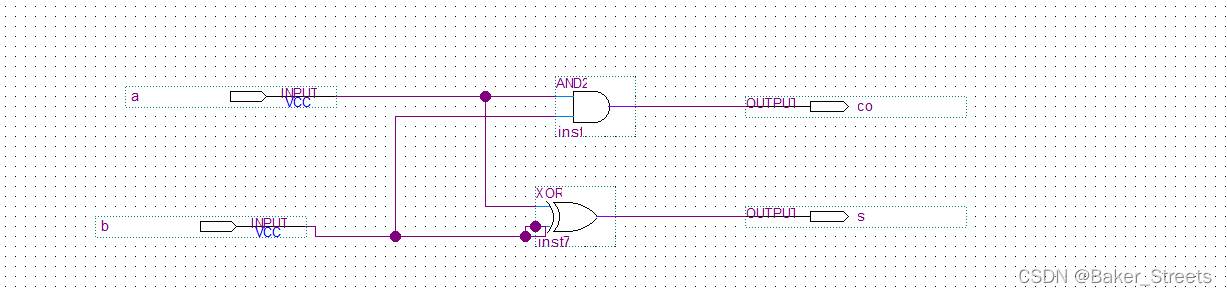

拖动管脚连接:

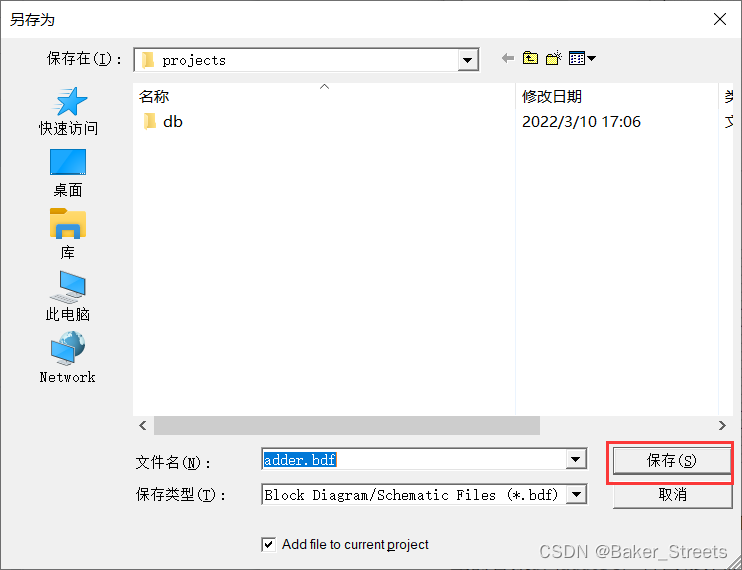

保存文件:

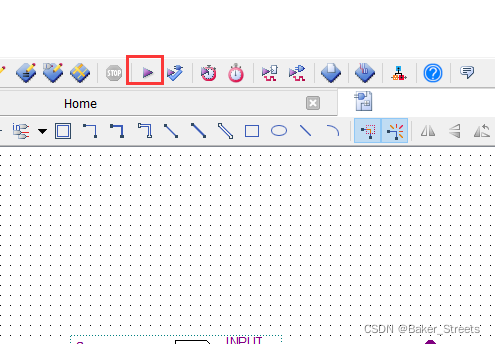

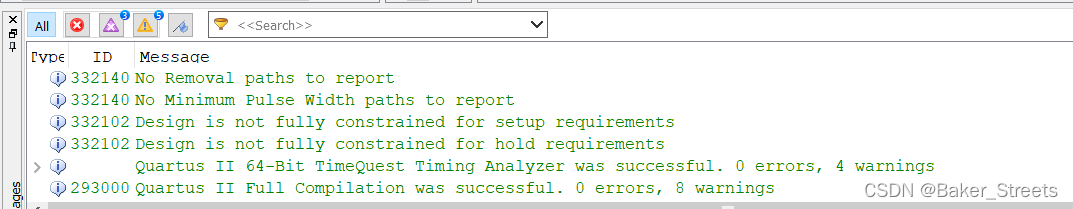

编译:

编译成功:

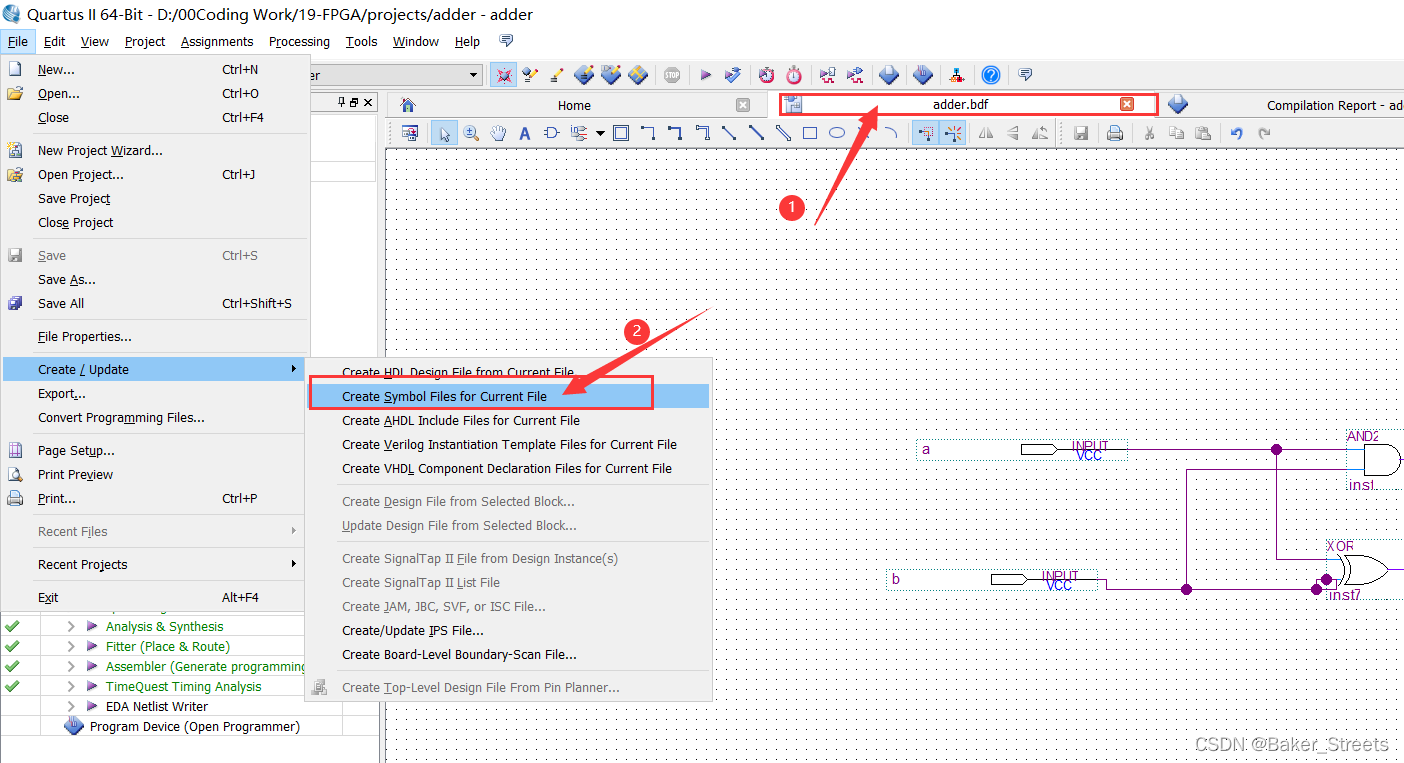

在打开adder.bdf的情况下,将设计项目设计为可调用的元件:

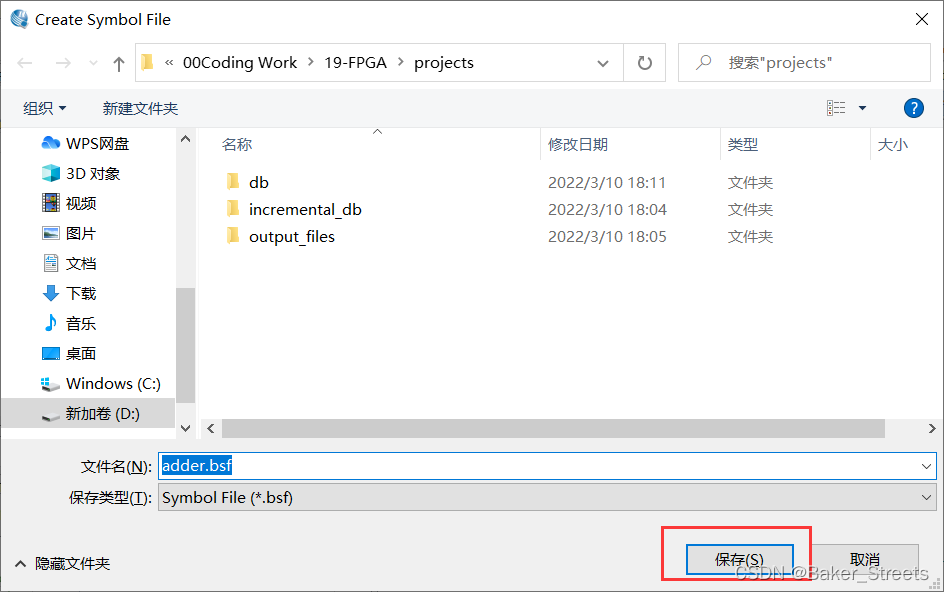

保存:

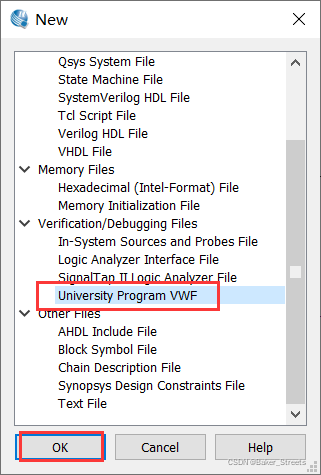

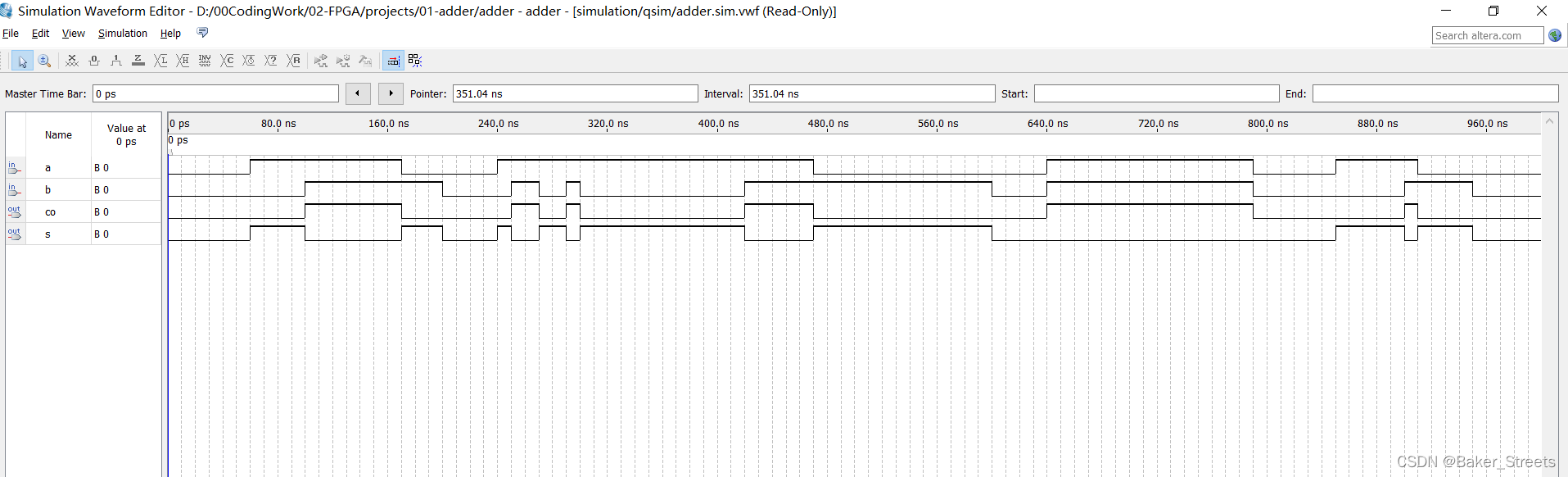

3. 半加器仿真

New:

选择University program VWF,OK:

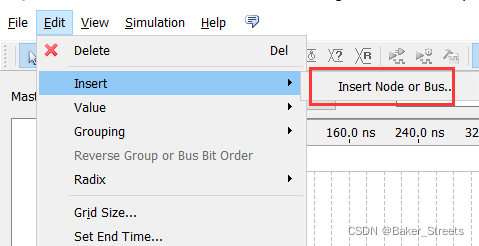

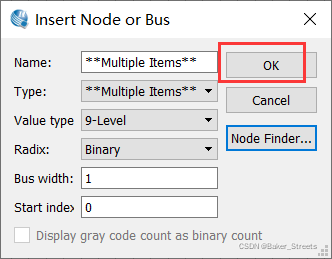

选择Edit→Insert→Insert Node or Bus…:

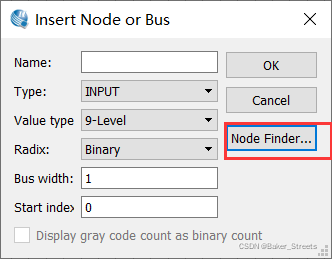

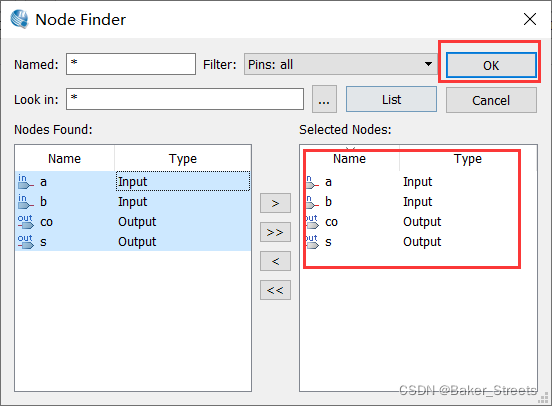

点击Node Finder:

List:

将左边所有端口移到右边,OK:

OK:

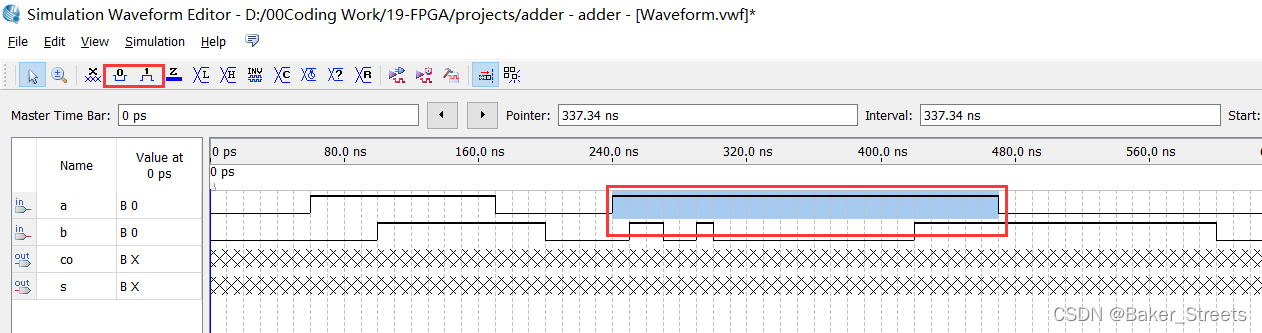

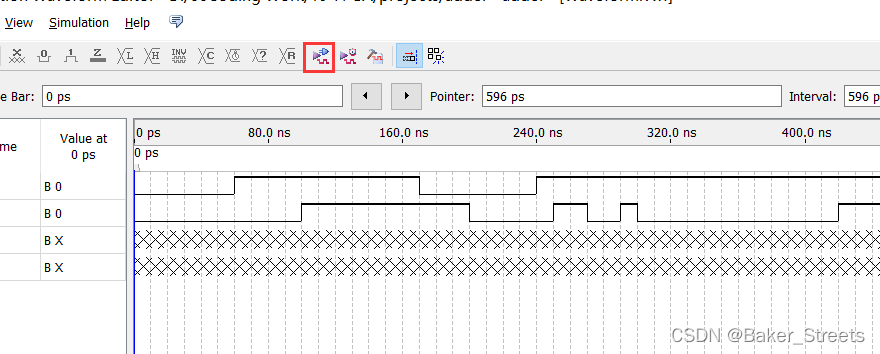

设置输入波形取值:

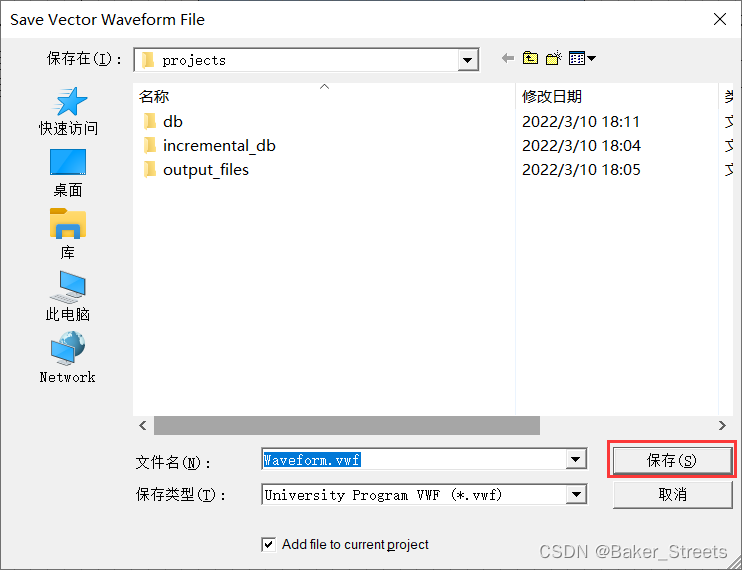

Ctrl + S 保存:

仿真:

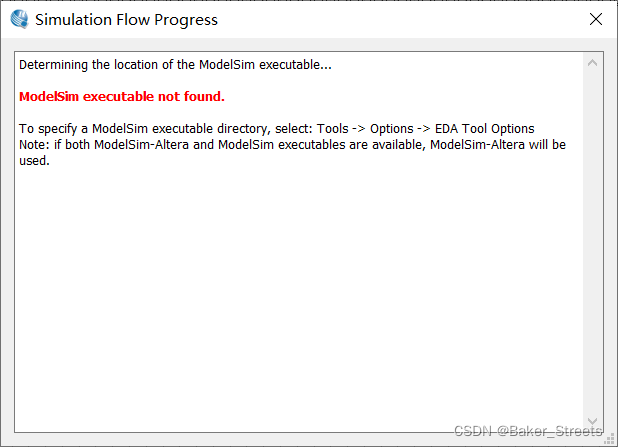

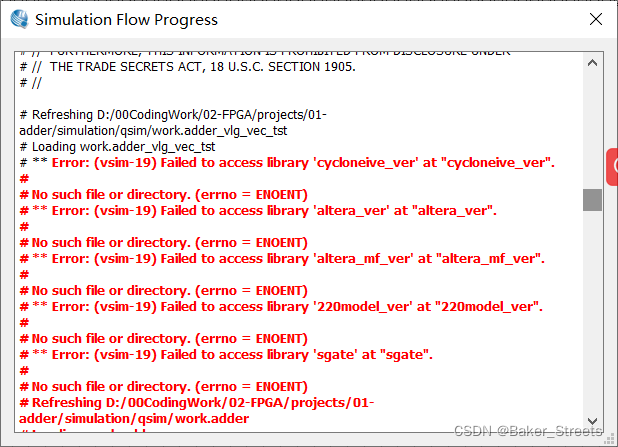

发现报错:

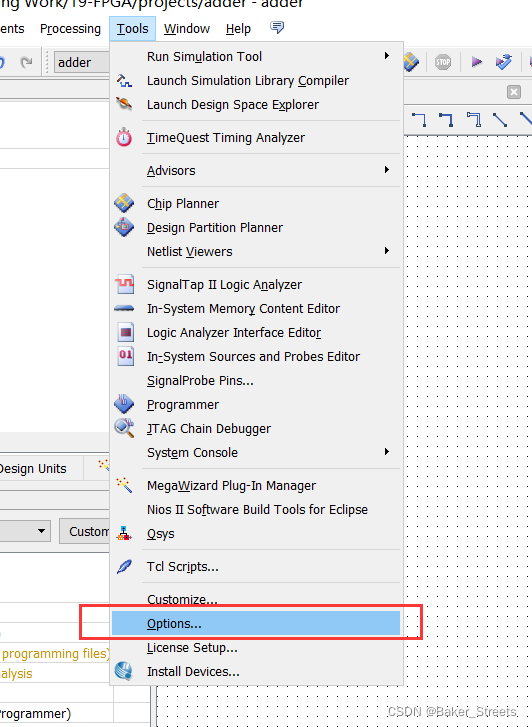

根据网上方法,加入modelisim.exe的位置:

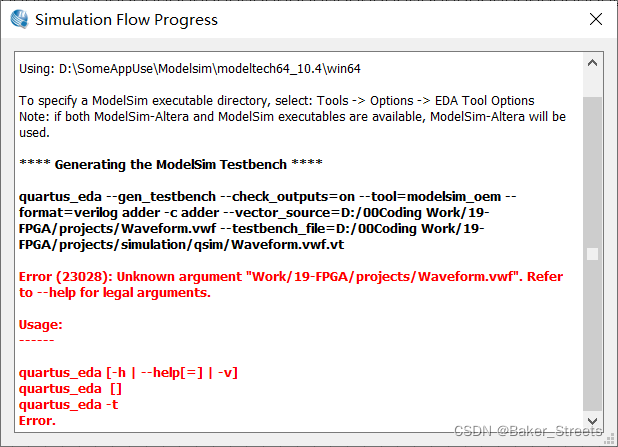

再次编译,发现任然报错:

但错误信息不同,此次错误原因为项目文件不能有空格。

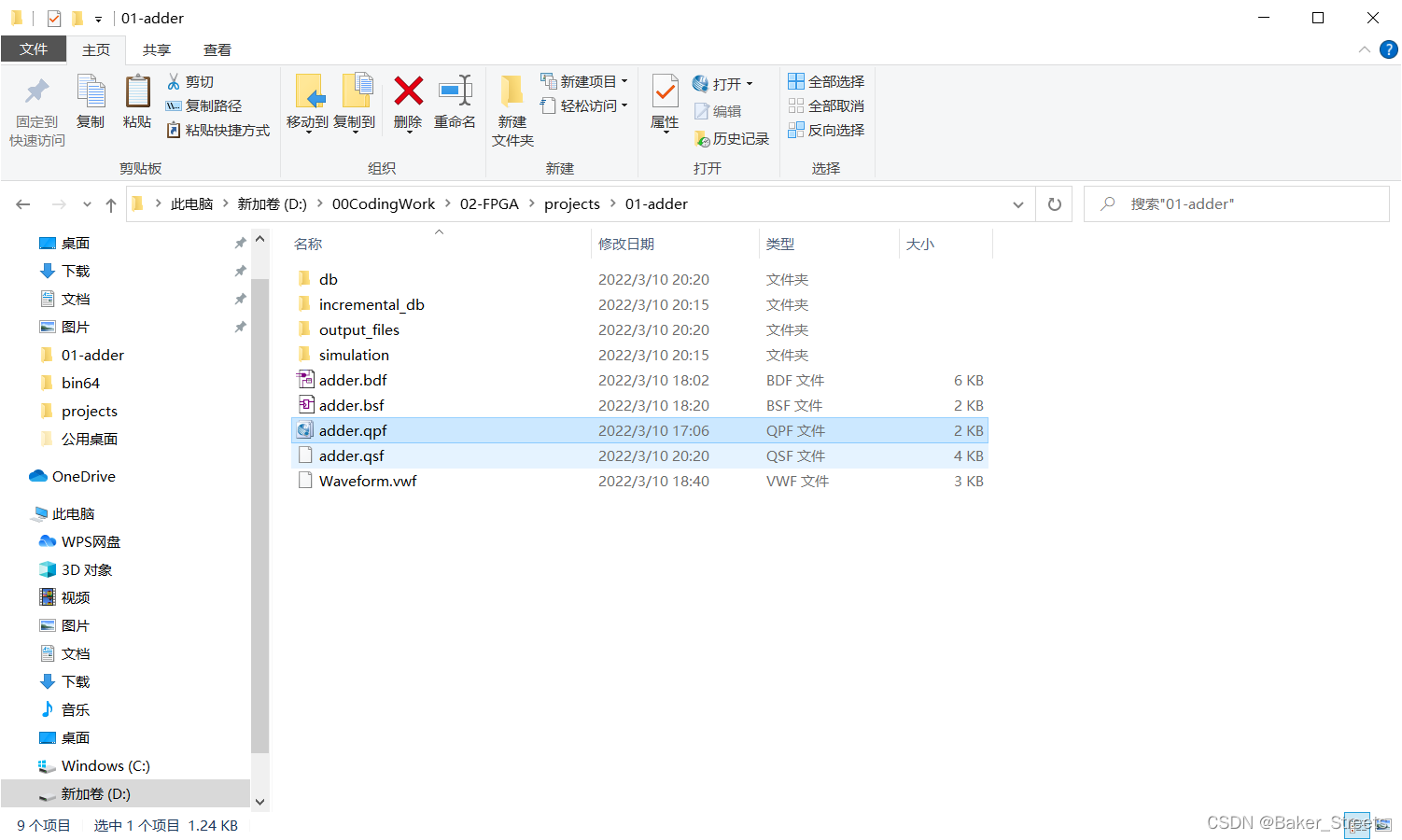

于是,将该项目复制到新文件夹:

双击.qpf文件打开项目:

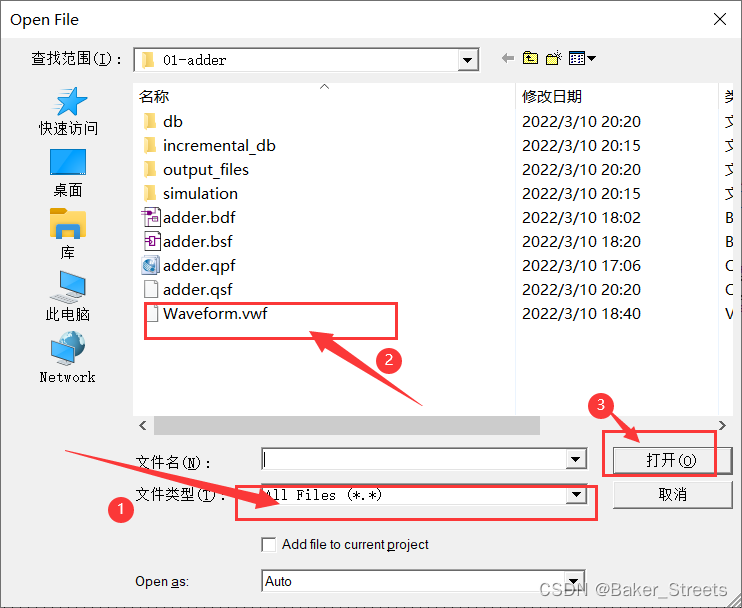

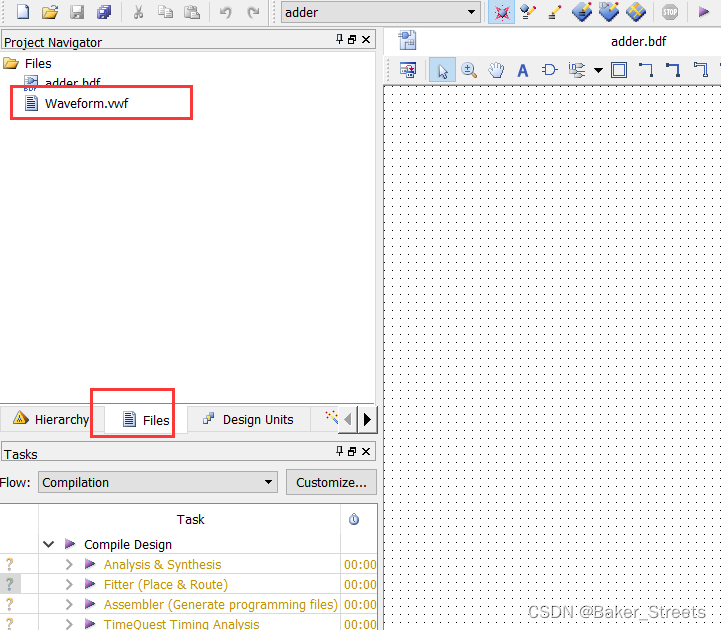

Open打开之前的.vwf(仿真)文件:

仿真,发现任然报错:

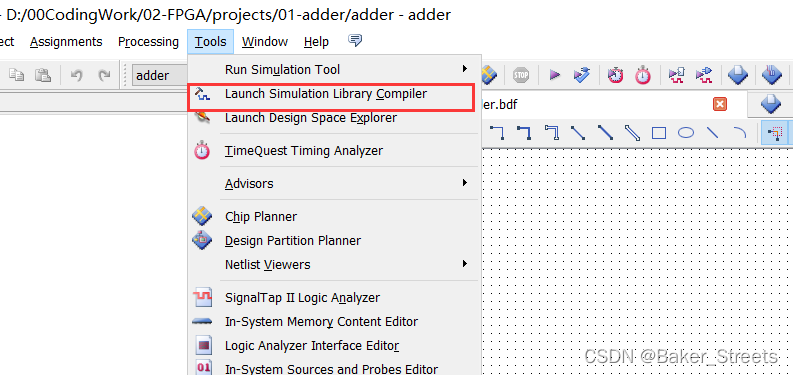

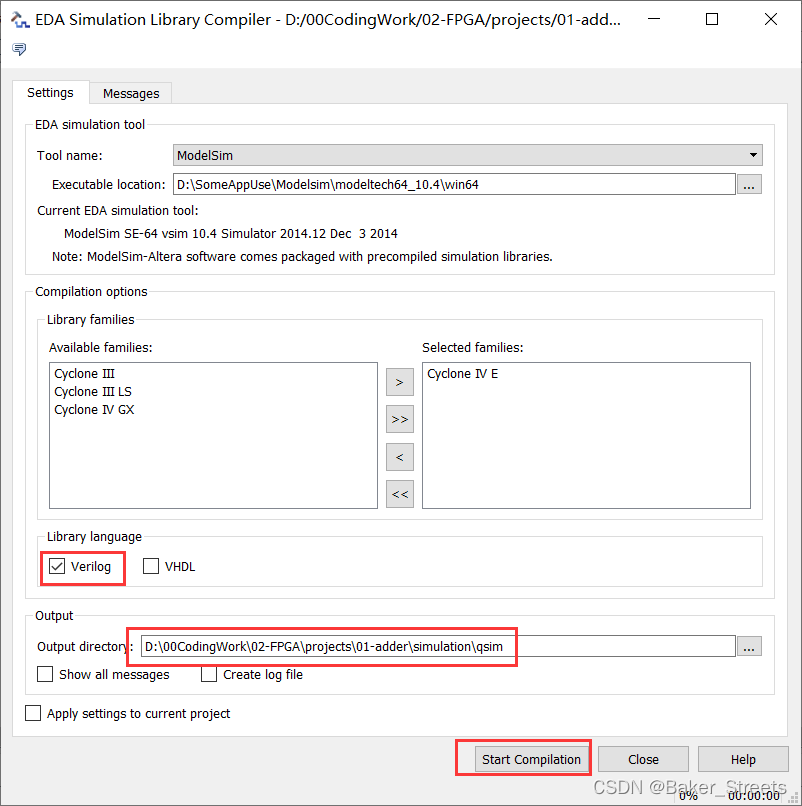

解决方法:

Output directory一定要选择项目下的simulation\qism:

打开.vwf文件,再次仿真,成功:

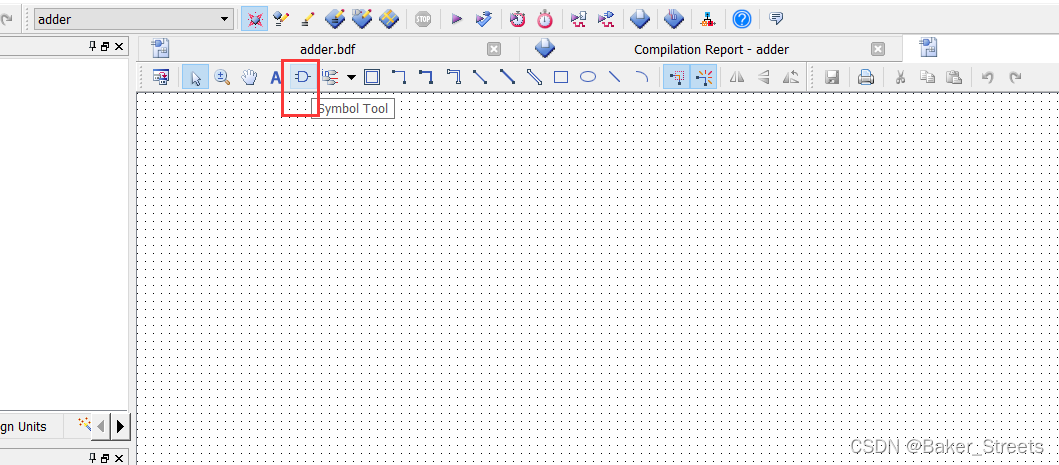

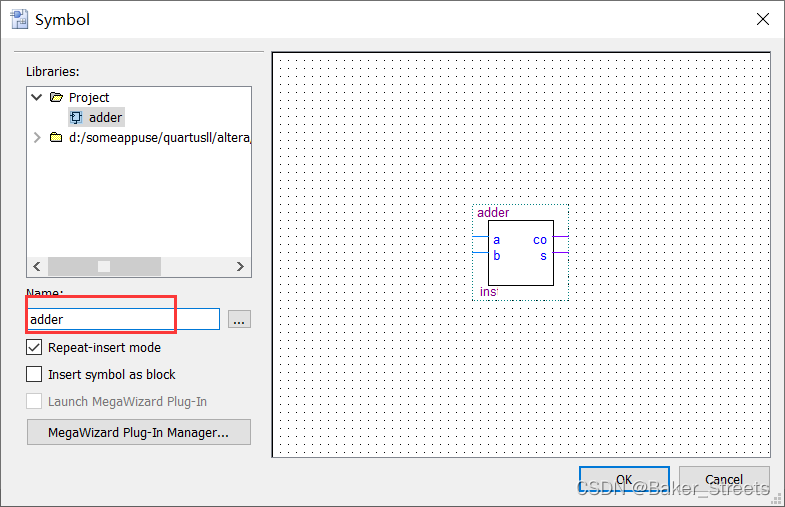

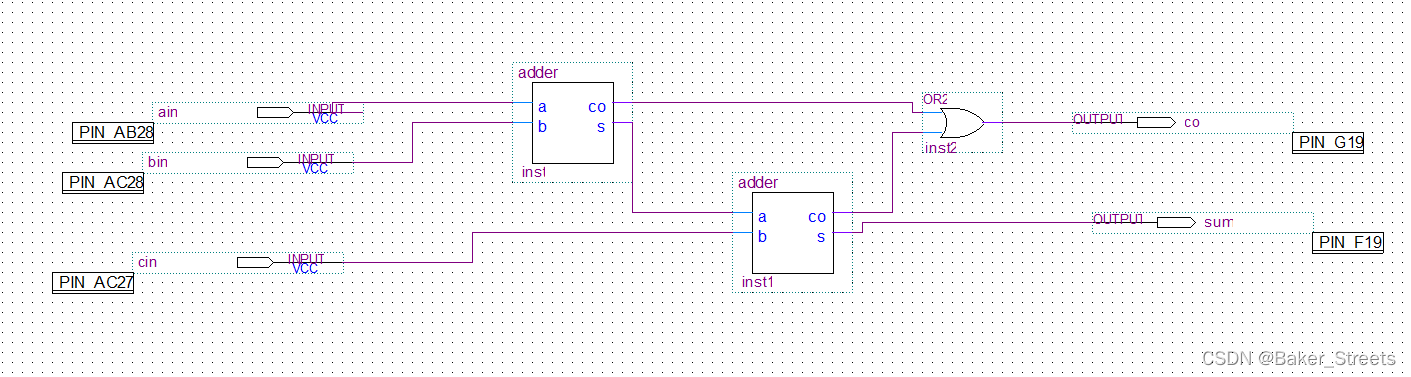

4. 设计全加器顶层文件

New:

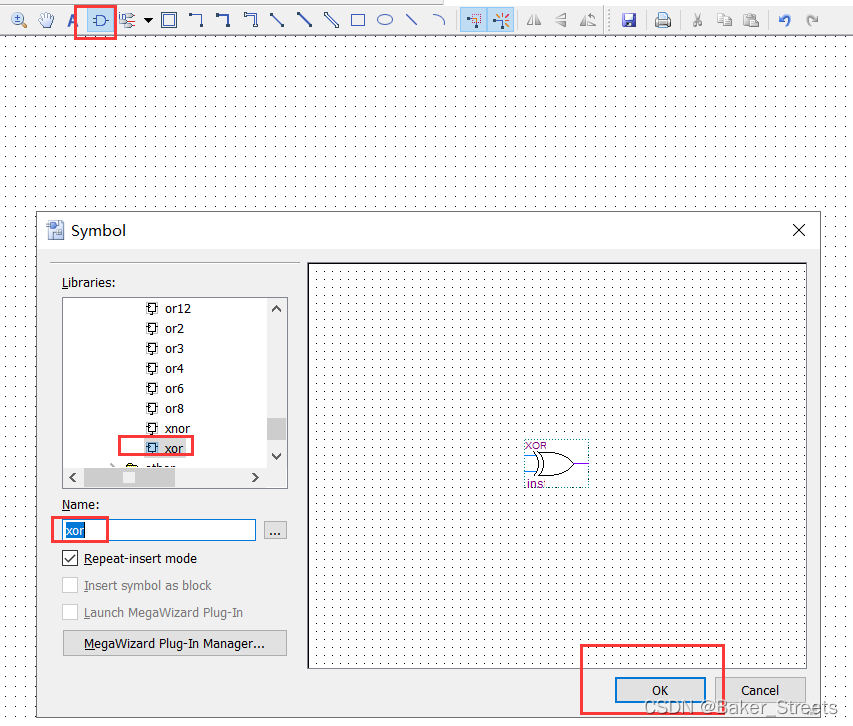

选择Symbole Tool,搜索adder,即之前的半加器:

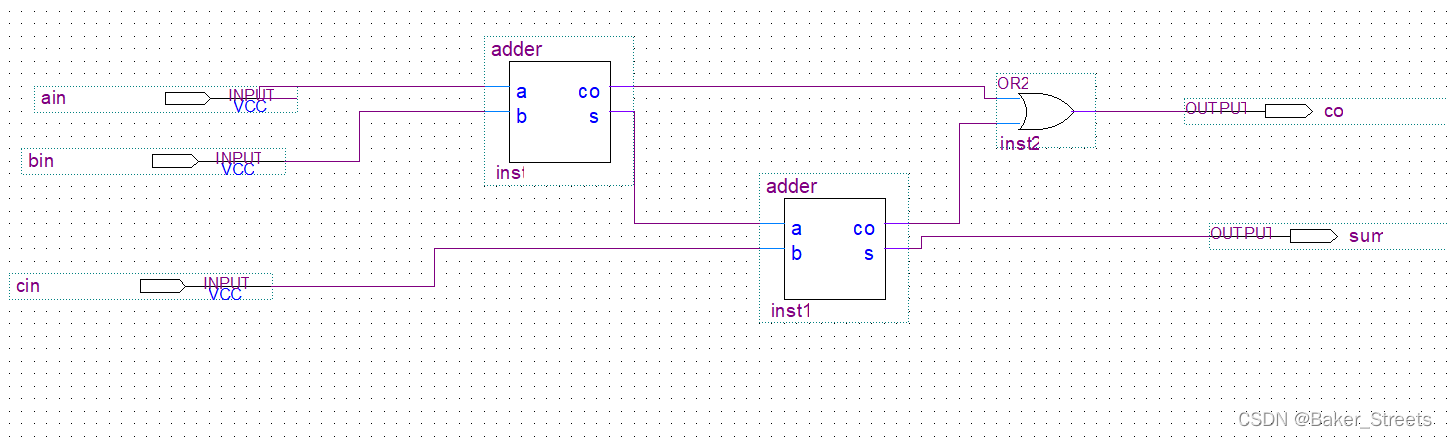

再加上其他元件,构成全加器:

- 两个半加器

- 一个or2

- 三个input

- 2个output

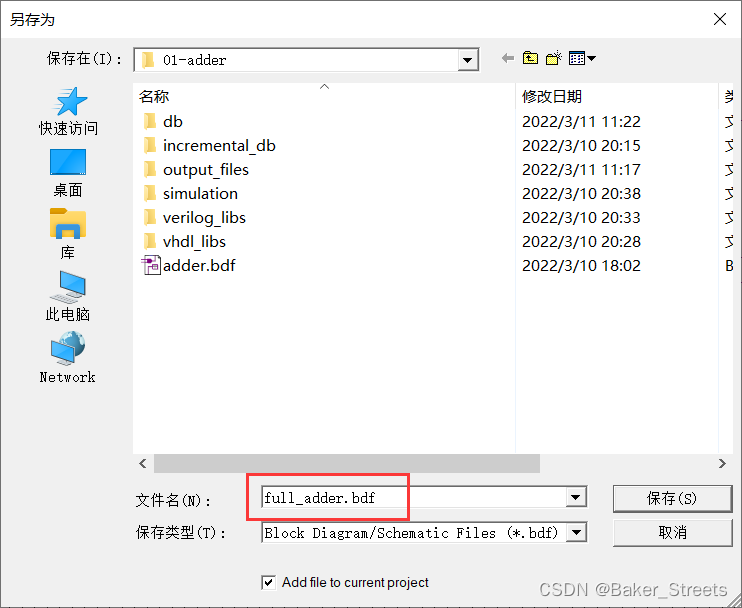

Ctrl + S 保存为full_adder.bdf:

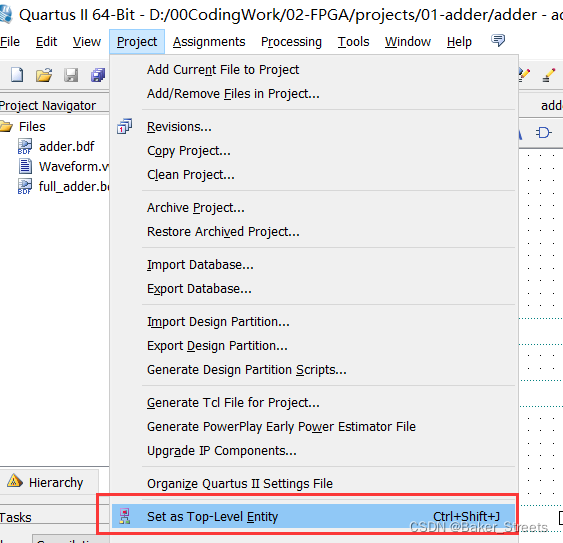

将其设置为顶层文件:

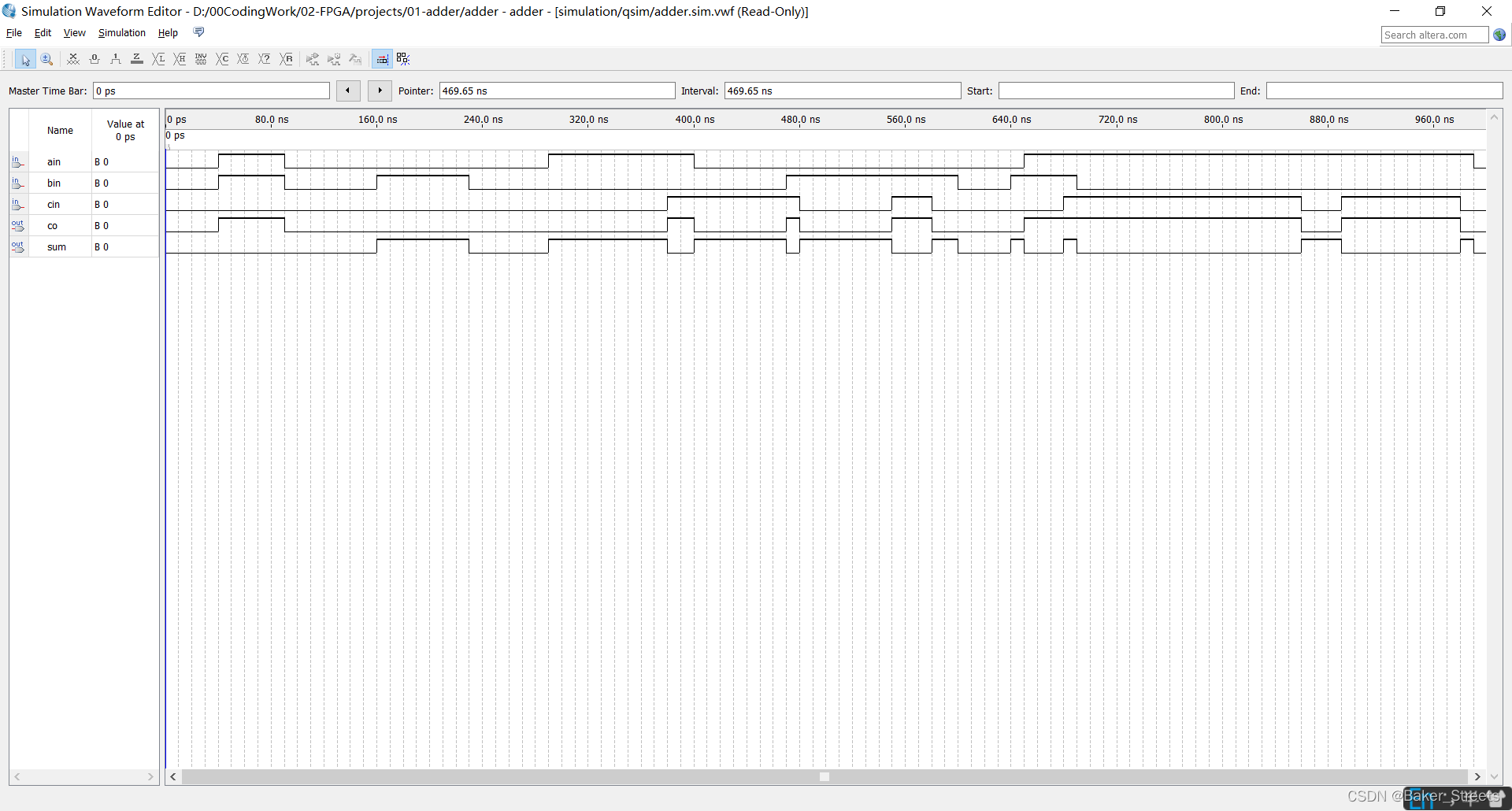

编译、仿真:

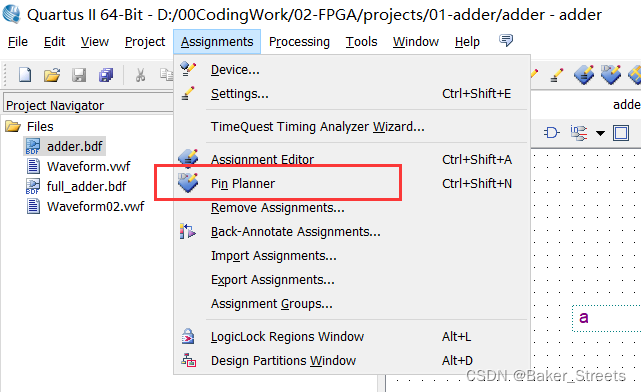

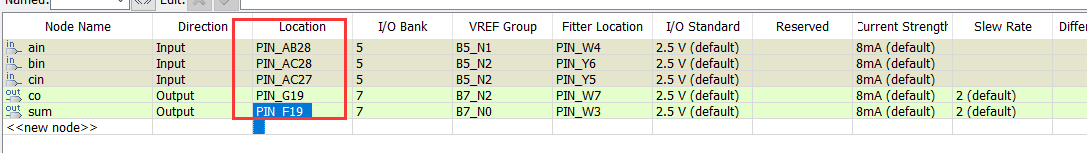

5. 引脚绑定

选择Pin Planner:

绑定相应引脚:

再次编译:

6. 烧录

烧录:

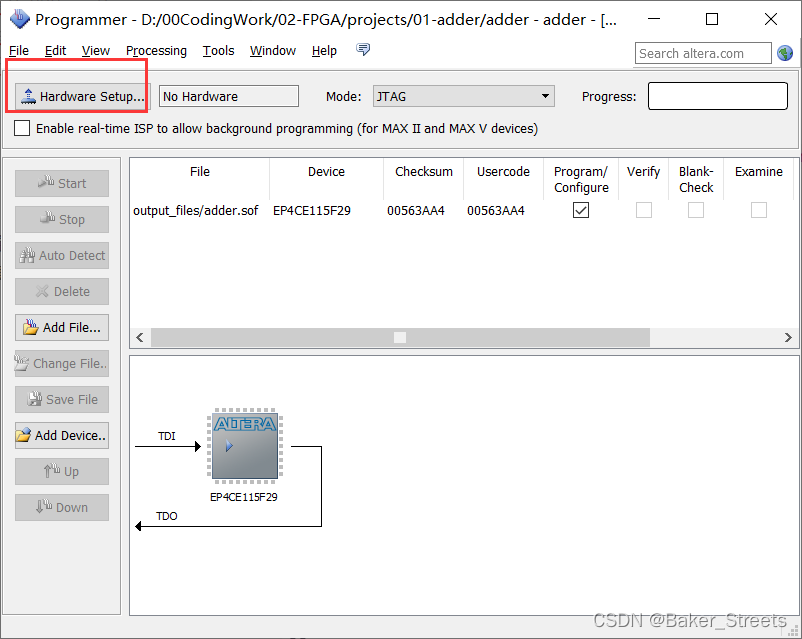

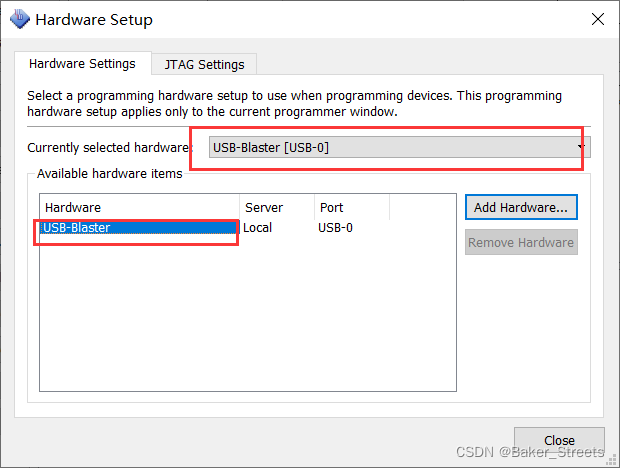

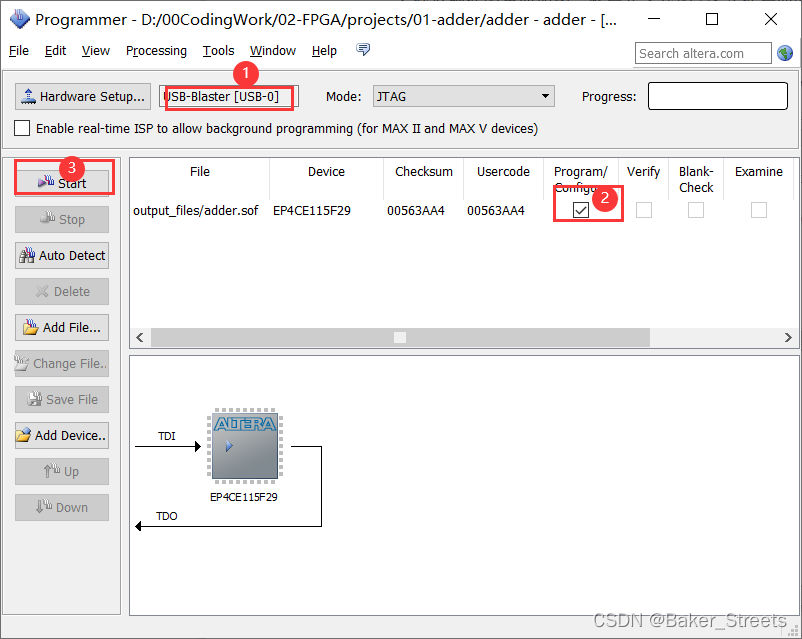

第一次下载需安装硬件。即在下载界面中点击按钮hardware setup...,然后在弹出的对话框中选择USB blaster,再点击ok,则硬件被安装上:

Start:

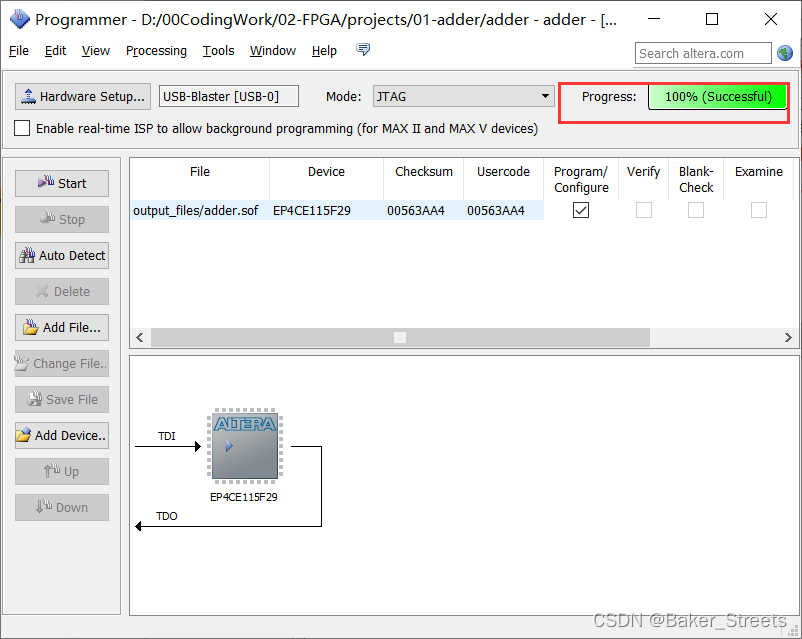

烧录成功:

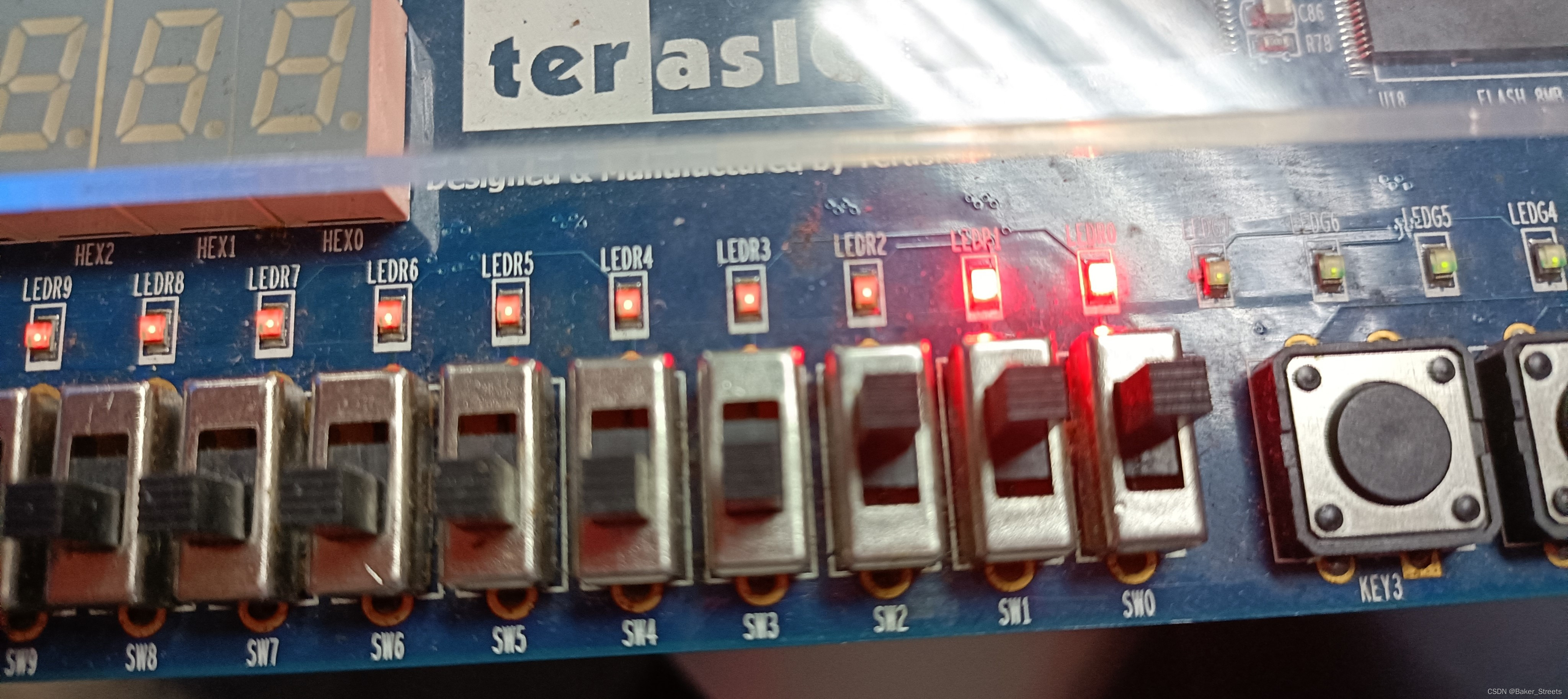

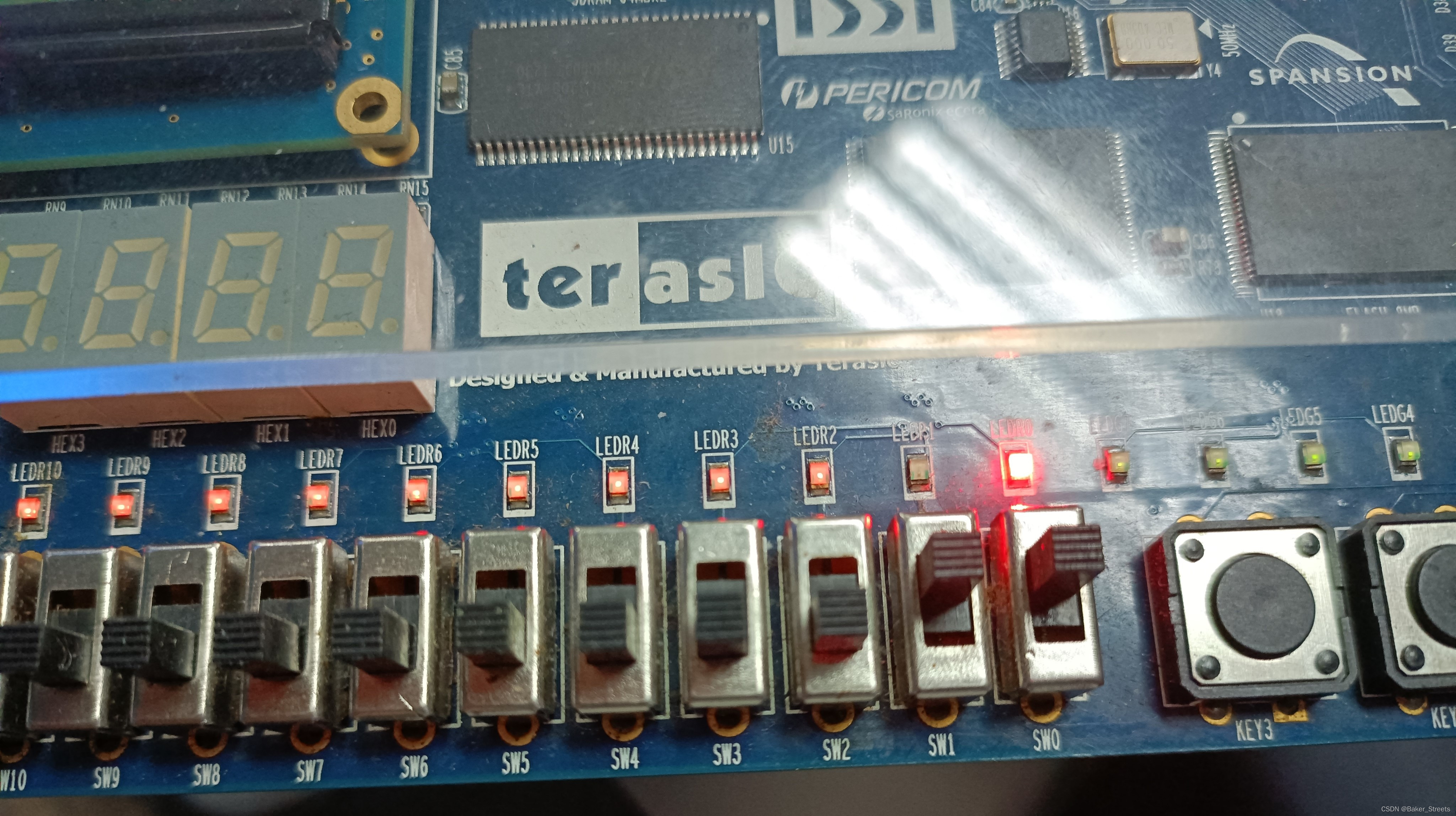

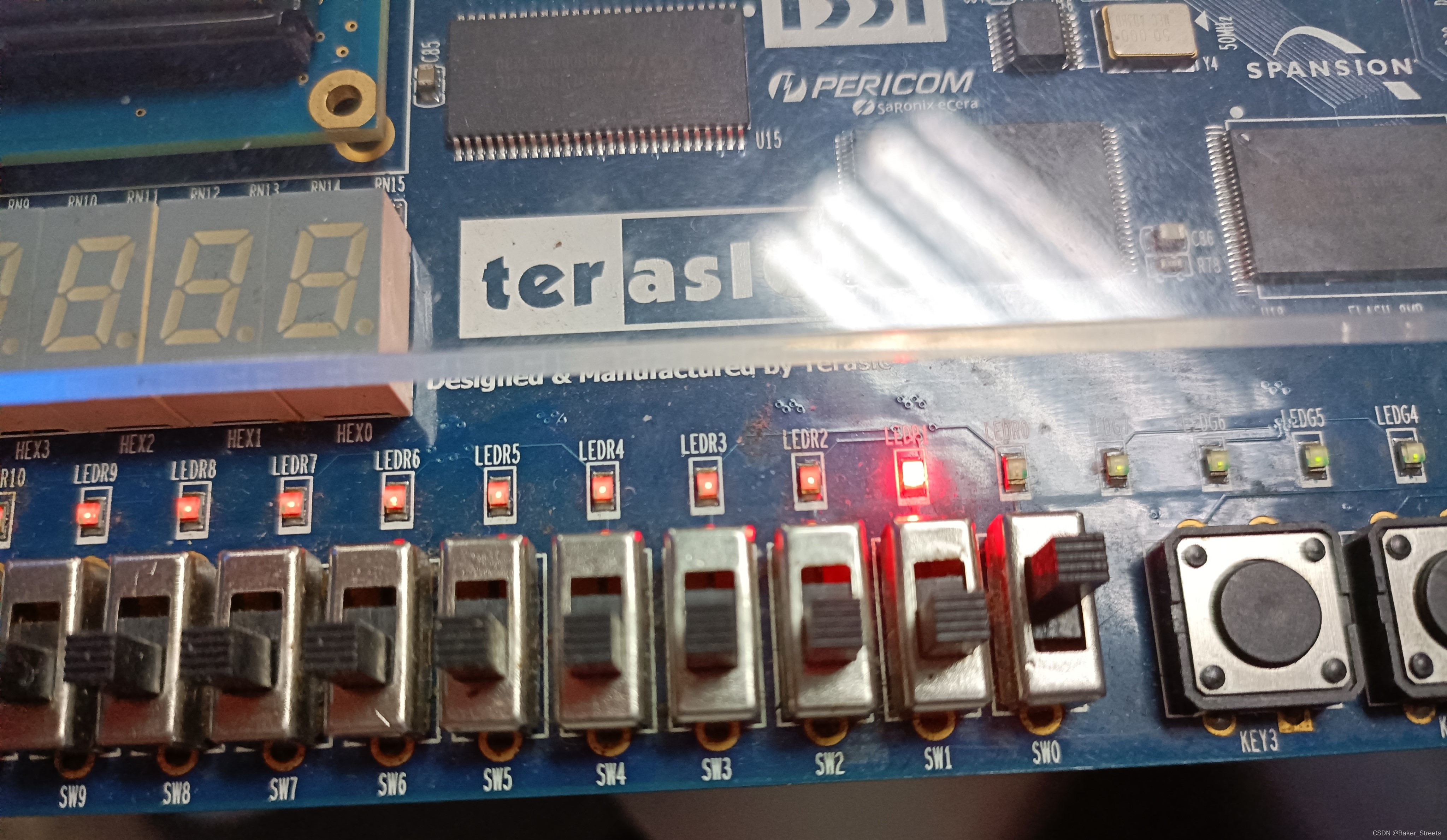

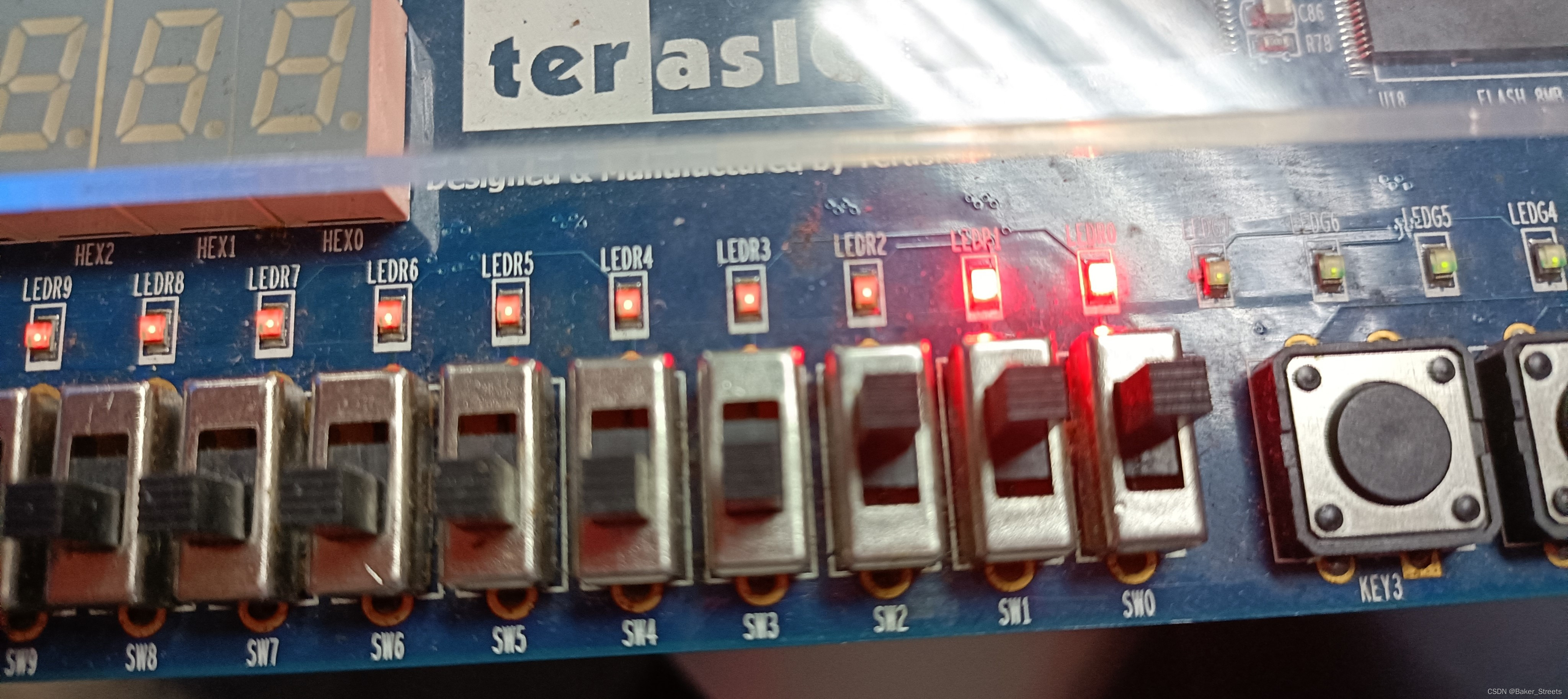

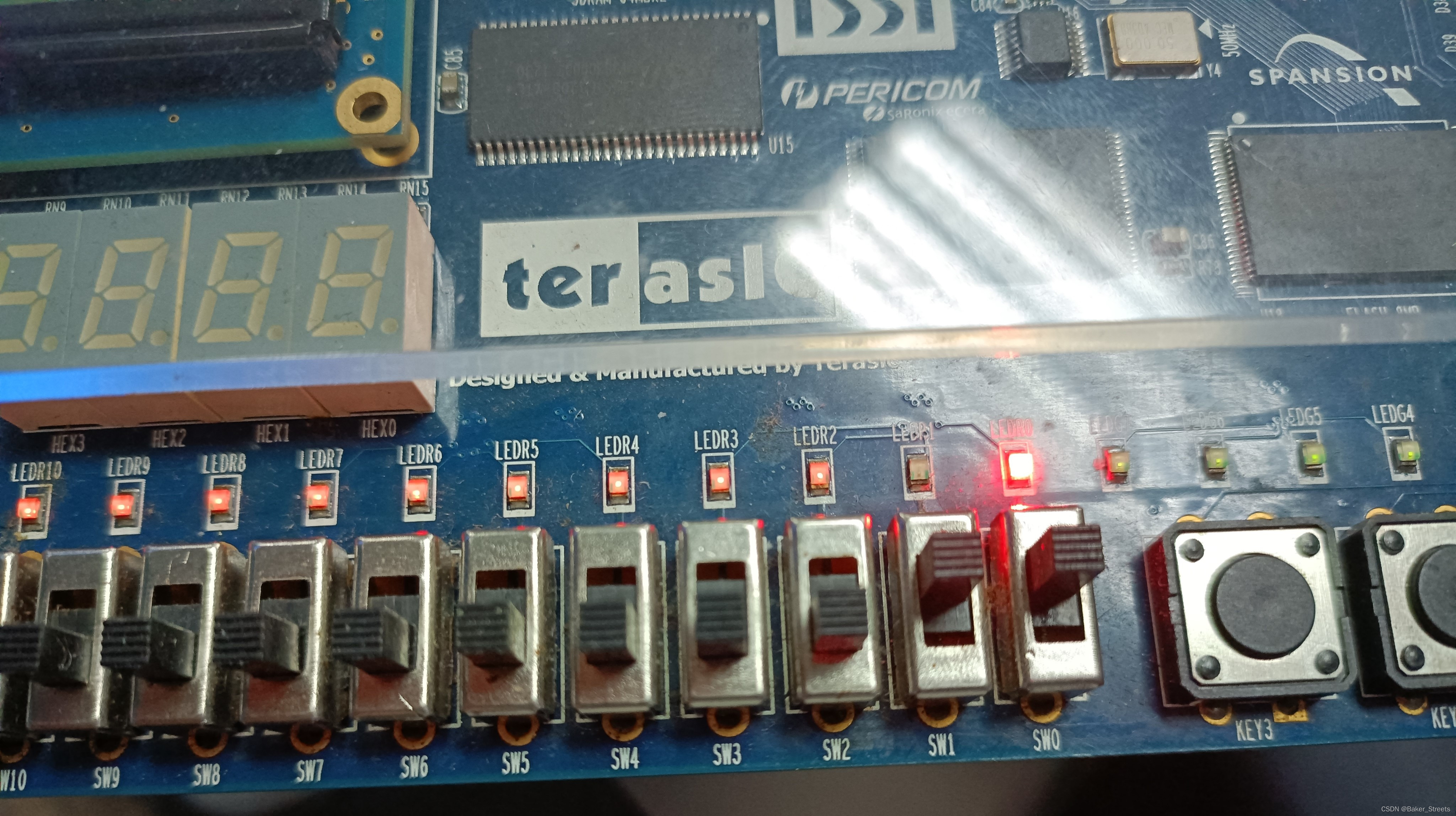

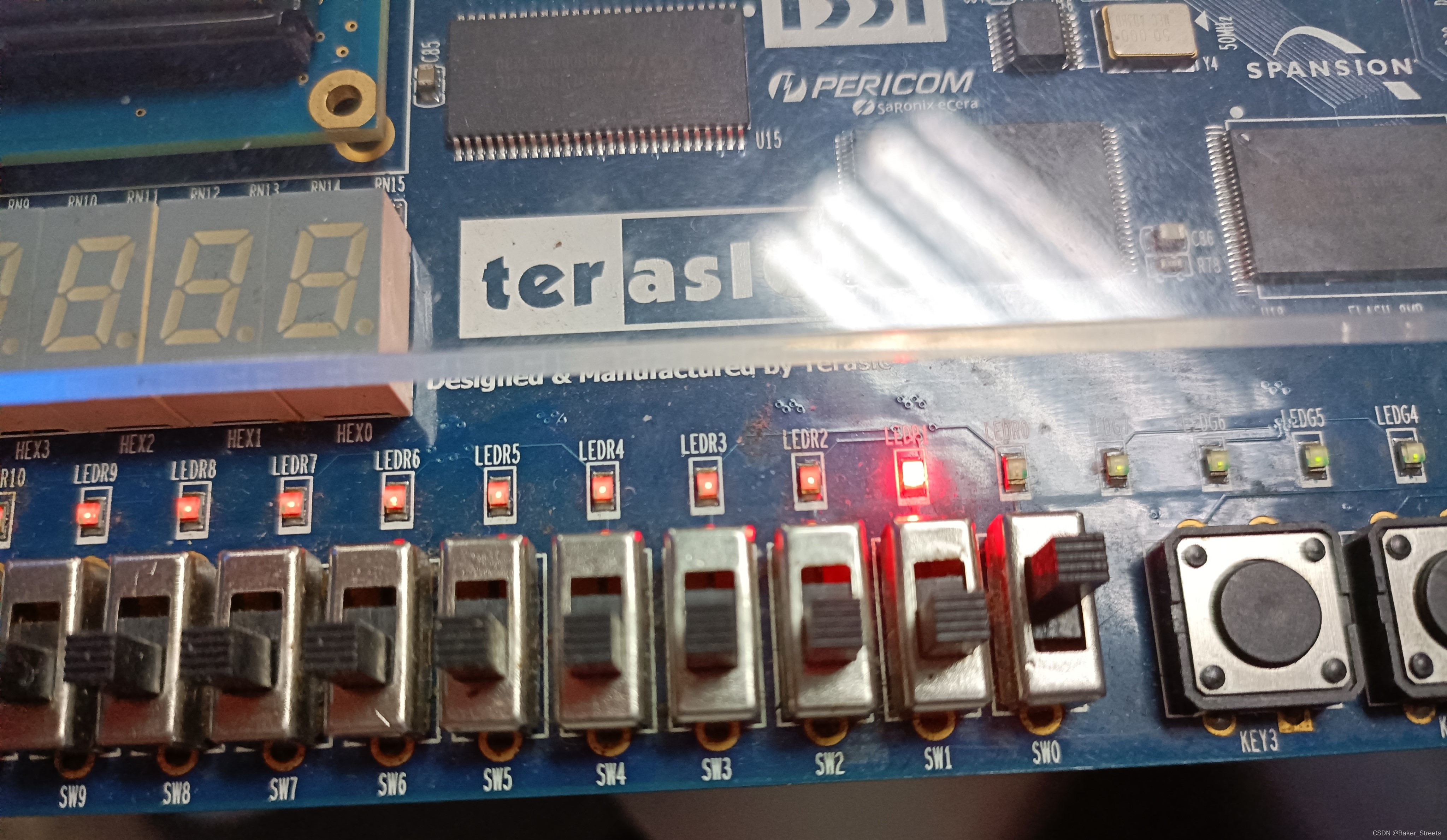

7. 结果

8. Verilog实现

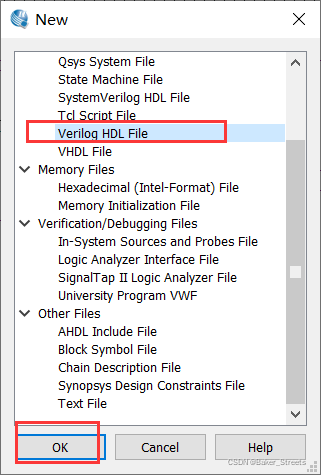

8.1 创建verilog文件

New:

第一行的my_fuller_adder需要和自己的文件同名:

module my_fuller_adder(

//输入信号,ain表示被加数,bin表示加数,cin表示低位向高位的进位

input ain,bin,cin,

//输出信号,cout表示向高位的进位,sum表示本位的相加和

output reg cout,sum

);

reg s1,s2,s3;

always @(ain or bin or cin) begin

sum=(ain^bin)^cin;//本位和输出表达式

s1=ain&cin;

s2=bin&cin;

s3=ain&bin;

cout=(s1|s2)|s3;//高位进位输出表达式

end

endmodule

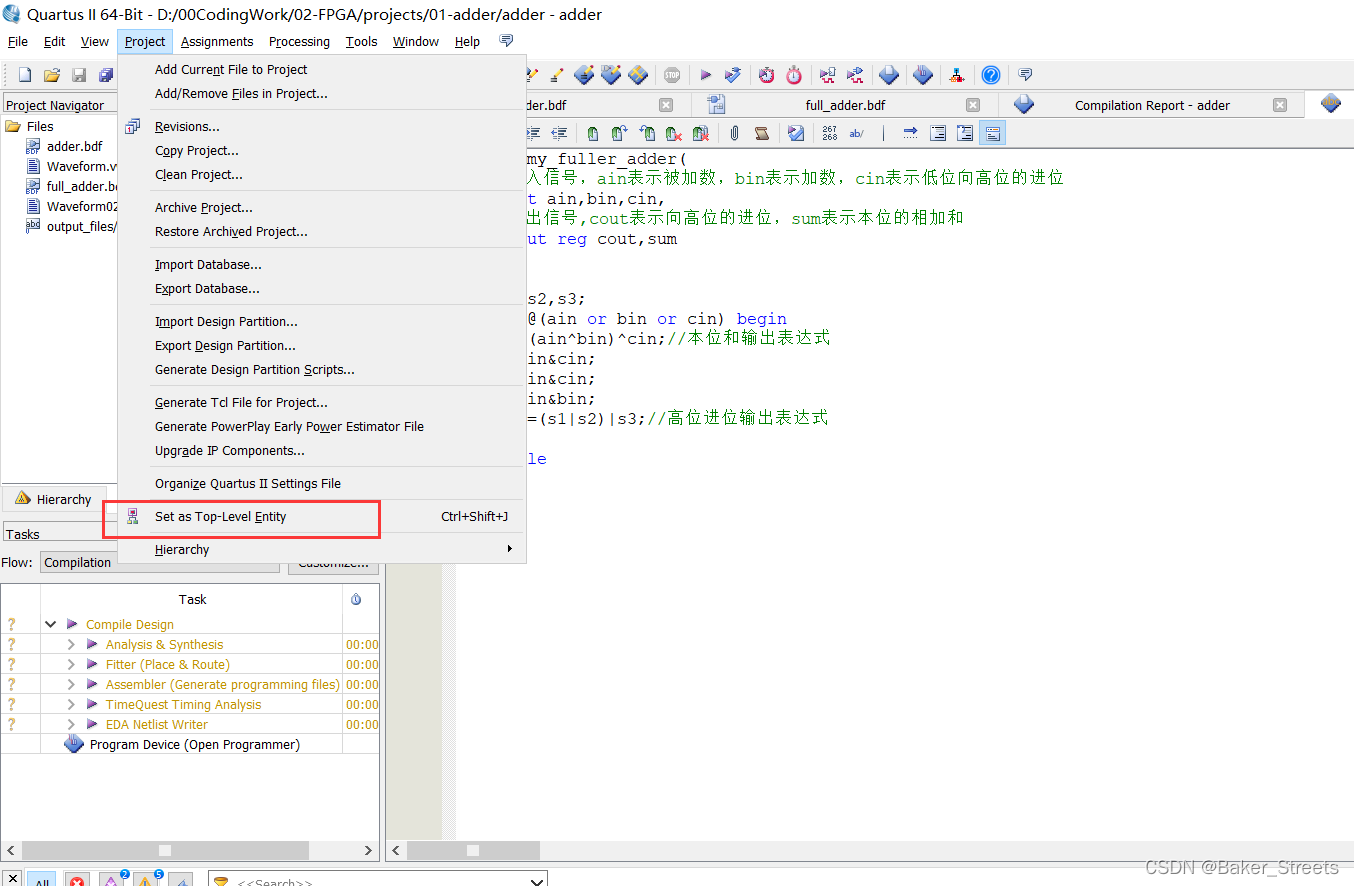

设置为顶部文件:

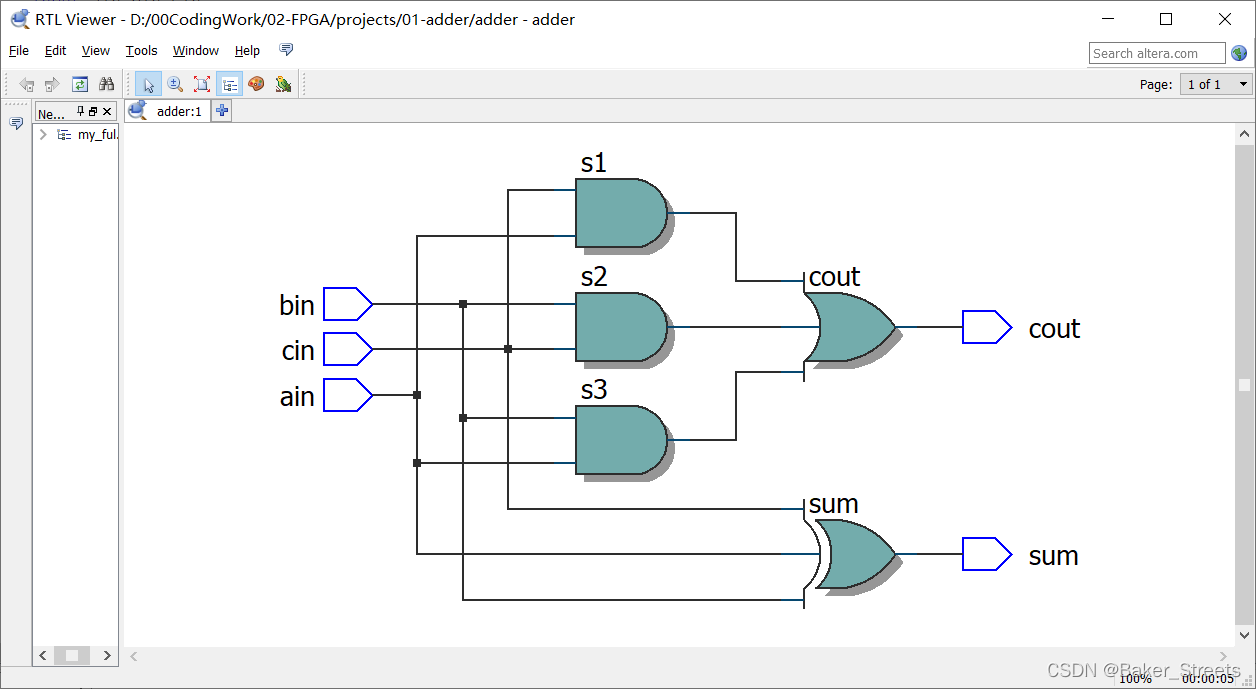

编译,查看电路图:

8.2 仿真

8.3 烧录

五、总结

Verilog编写相对于自己搭建电路,十分方便。

参考

https://stackoverflow.com/questions/28919269/waveform-file-not-running-under-simulation