文章目录

RISC-V ISA基本介绍

RISC-V历史简介

念作”risk-five”,代表Berkeley研发的第五代精简指令集。

RISC-V是什么

一款高质量、免许可证、开放的RISC ISA,有非盈利的基金会维护的标准,适用于所有类型的计算机系统,不是一家公司,也不是一款CPU,

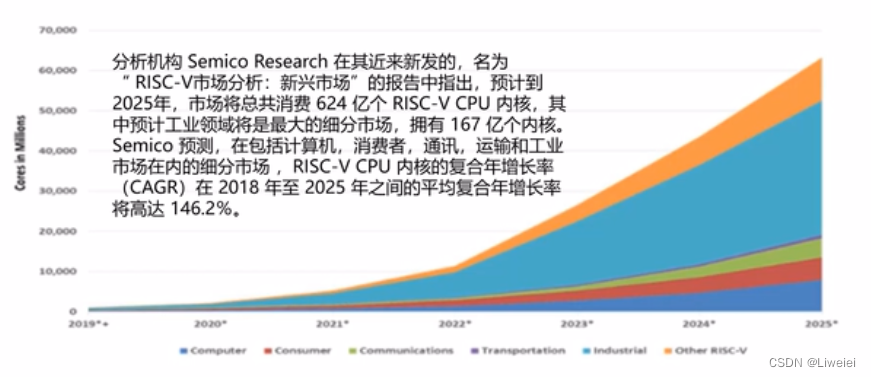

RISC-V发展现状

RISC-V成员已超过700个,分布在全球50个国家。

RISC-V特点

- 简单:规范手册简短(几百页)

- 清晰的分层设计

- 模块化

- 增量ISA:计算机体系结构的传统方法,以8086为代表,即向下兼容,不可以抛弃旧指令,缺点是后学系者成本较高。

- 模块化ISA:由1个基本整数指令集+多个可选拓展指令集组成,基础指令是固定的。

RISC-V属于模块化指令集

- 稳定

- 社区化

RISC-V规范

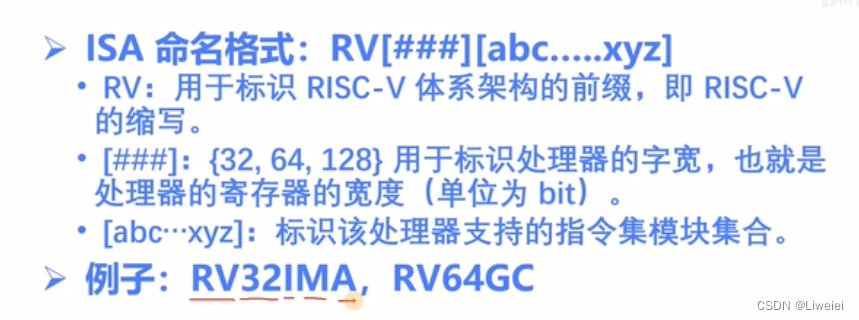

命名格式

RV[###][abc…xyz] 基本整数指令集:

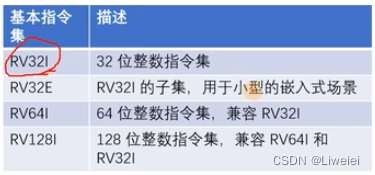

基本整数指令集:

拓展模块指令集

通用寄存器(32个)

RISC-V定义了32个通用寄存器和一个PC

寄存器的宽度由ISA指定:

- RV32的寄存器宽度为32位

- RV64的寄存器宽度为64位,依次类推

Hart

HARdware Rhread 硬件线程,代表一个独立运行的指令流

一个Hart相当于一个虚拟的CPU

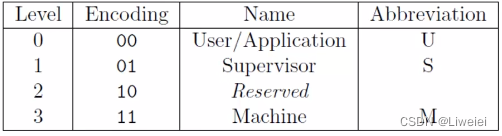

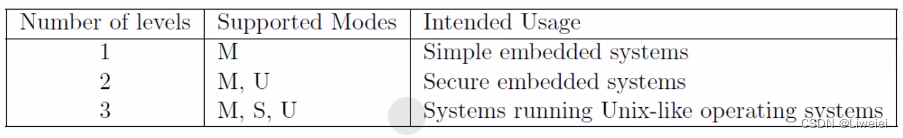

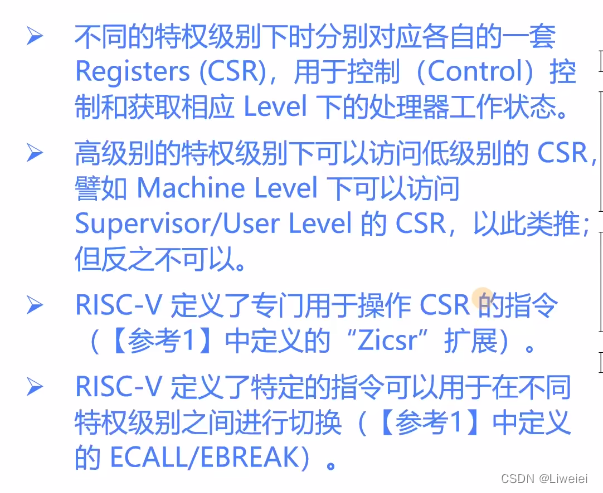

特权级别

RISC-V的Prvileged Soecification定义了三个特权级别

Machine是最高的级别,所有的实现都需要支持

可选的Debug级别:

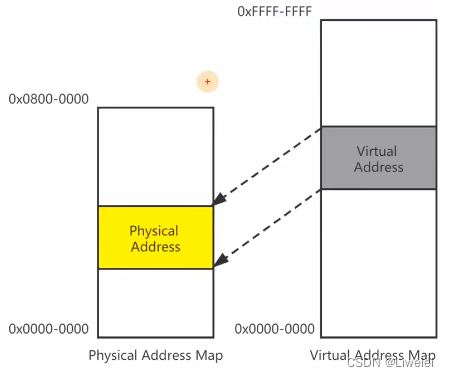

内存管理和保护

RISC-V内存管理分两种

物理内存保护

- 运行M模式指定U模式可以访问的内存地址

虚拟内存

- 需要支持Supervisor Level

- 用于实现高级的操作系统特性

- 多种映射方式

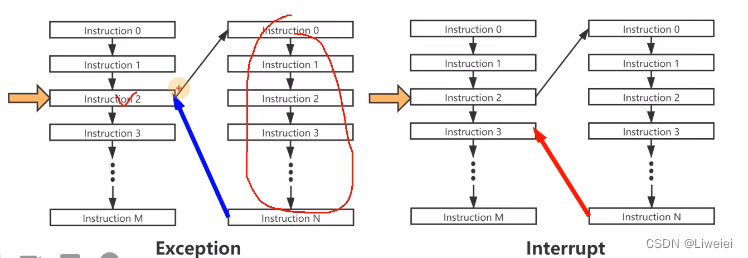

异常和中断

异常处理程序在执行完之后会再次执行之前出现异常的一行命令,但中断处理程序执行完之后会回到发生中断时正在执行的指令的下一条指令