系统总线概念

各部件之间为了通信,单独连线,太复杂,于是诞生了总线的概念

基本概念

是一组能为多个部分分时共享的公共信息传送路线

总线分类

按传送方式

- 串行:在总线上1位1位的传输和接收

- 并行:多位在总线上传输和接收,需要多条数据线

按使用范围

- 片内总线

芯片内部的总线 - 系统总线

CPU、主存、I/O设备之间的信息传输线,又称板级总线或板间总线- 数据总线

传输数据信息,是双向传输总线 - 地址总线

指出数据总线上源数据或目标数据在主存单元的地址,是出自CPU的单项传输总线 - 控制总线

发出控制信号的传输线,控制线单体单向,总线总体双向

- 数据总线

- 通信总线

用于计算机系统间或者与其它系统通信的传输线- 串行

- 并行

总线特性

- 机械特性

总线的机械连接标准,如插头插座规格等 - 电器特性

每根传输线上信号的传递方向和有效电平范围 - 功能特性

总线中每根传输线有各自负责的功能 - 时间特性

每根总线上的各个信号互相存在一定的有效时序关系,可以通过信号时序图来描述

总线的性能指标

- 总线宽度

数据总线的根数,用位(bit)表示 - 总线带宽

总线的数据传输速率(单位时间内传输的数据位数),常用字节每秒来计量(MBps:Million Byte per second, 兆字节每秒) - 同步方式

- 同步:总线数据与时钟同步工作

- 异步:不同步工作

- 总线复用

一条传输线分时传送不同信号,在不同时间承担了不同的功能角色 - 信号线数

信号线数 = 地址总线 + 数据总线 + 控制总线 - 总线控制方式

突发工作、自动配置、仲裁方式、逻辑方式、计数方式等 - 其它

工作频率,时钟频率,负载能力,电源电压,总线宽度拓展性等

总线标准

- ISA

- 不支持总线仲裁

- 数据传送必须通过CPU/DMA

- 时钟频率:8 MHz

- 最大传输速率:16 MBps

- 数据线:16 位

- 地址线:24 位

- EISA

- 智能化总线,支持突发方式和多总线主控器

- 时钟频率:8 MHz

- 最大传输速率:33 MBps

- 数据线:32位

- 地址线:32位

- 扩充DMA访问范围:2^32

- VESA(VL-BUS)

- 局部总线,由CPU总线演化而来

- 时钟频率:33 MHz

- 最大传输速率:133 MBps

- 数据线:32 位,可通过扩展槽拓展至64 位

- PCI

- 图形界面渲染

- 高性能

- 兼容良好

- 即插即用

- 支持多主设备

- 具有完全并行操作能力

- 支持数据和地址的奇偶校验

- 支持两种电压标准:5V 和 3.3V

- 可扩充性

- 多路复用奇数

- AGP

- 三维数据的处理

- RS-232C

- 串行通信,数据中断和通信设备的二进制数据交换接口标准

- USB

- 通用的外设串行连接通信标准

- 真·即插即用

- 标准高度统一

- 连接线缆轻巧

- 生命力强,无专利版权限制

总线结构

单总线结构

将所有的CPU, 主存和 I/O 设备都挂到一条系统总线上,同一时刻只能有一对部件进行

优点:

- 结构简单,便于扩充

缺点:

- 数据传输效率较低

- 数据吞吐量较低

双总线结构

- 存储器中心的双总线结构

在单总线的基础上,开辟了一条存储总线,专门负责主存与CPU之间的信息传输,既提高了传输效率又减轻了系统总线的负担,还保留了I/O设备与存储器交换信息时不经过CPU的特点

- I/O中心的双总线结构

将速度较低的I/O设备分离出来,减轻了系统总线的压力

- 面向CPU的双总线结构

M总线也是存储总线,所有的I/O设备通过I/O接口挂载到I/O总线上,便于增删I/O设备,但I/O设备在于主存交换信息时会占用CPU,从而影响CPU的工作效率

三总线结构

主存总线用于CPU和主存之间的信息传送,I/O总线用于CPU和各个I/O之间进行信息传输,DMA总线用于高速外设和主存之间的信息交换。在这种三总线结构中,DMA总线和主存总线不能同时用于访问主存

另一种形式

四总线结构

I/O性能的进一步提升,高速设备和CPU更加紧密,低速设备则通过扩展总线进行连接

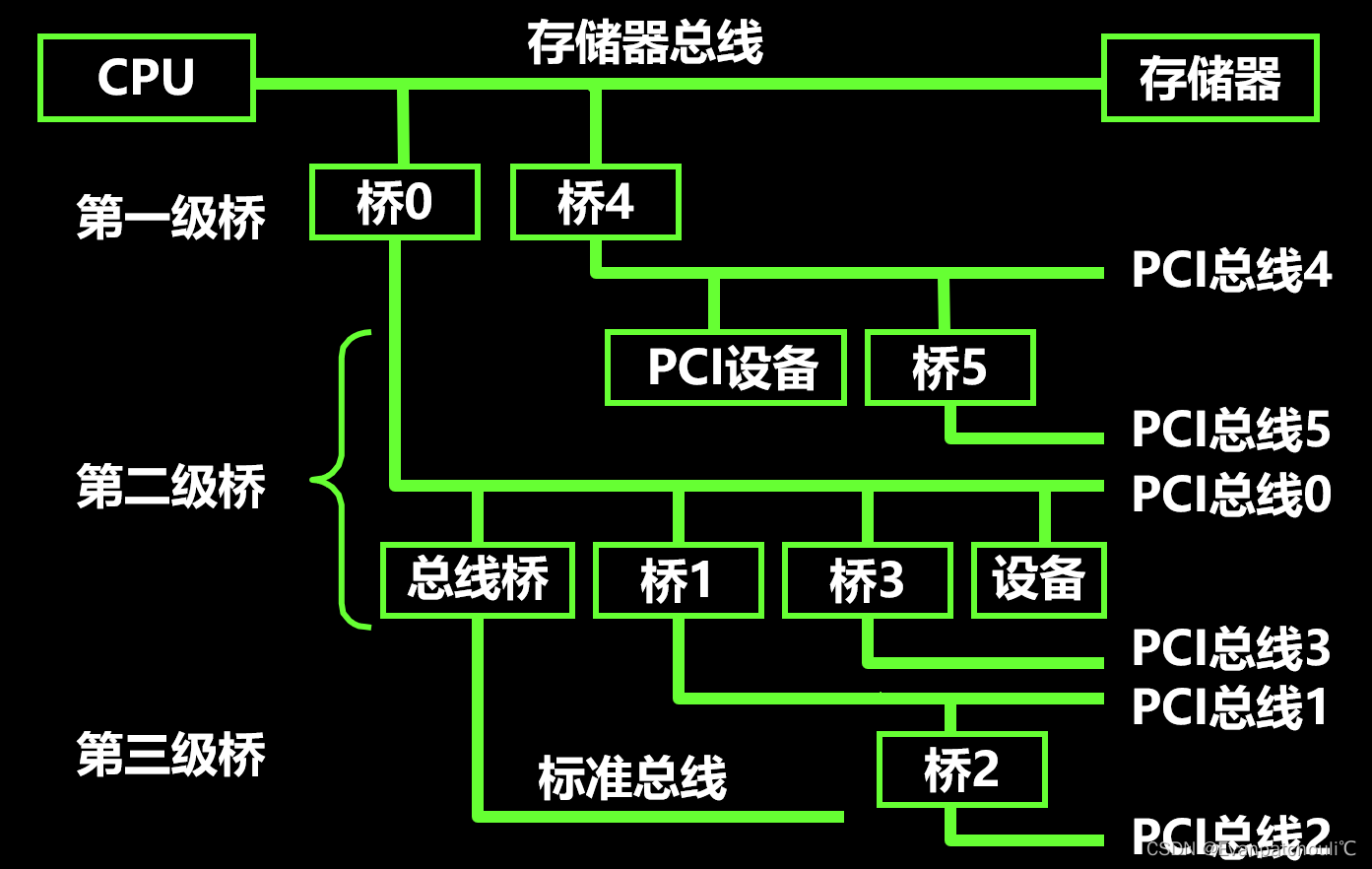

PCI总线结构

PCI总线通过 PCI桥 与系统总线相连接,使得CPU总线与PCI总线相互隔离,具有更高的灵活性,支持更多的高速设备,而低速设备则挂载在ISA和EISA总线上。当PCI总线驱动能力不足时,可以扩展为多层PCI总线结构。