1.

写出下列各整数的原码、反码、补码表示(用

8

位二进制数)。其中

MSB

是最高位(符号位),

LSB

是最低位。

(

1

)

–35

(

2

)

–128

(

3

)

–127

(

4

)

–1

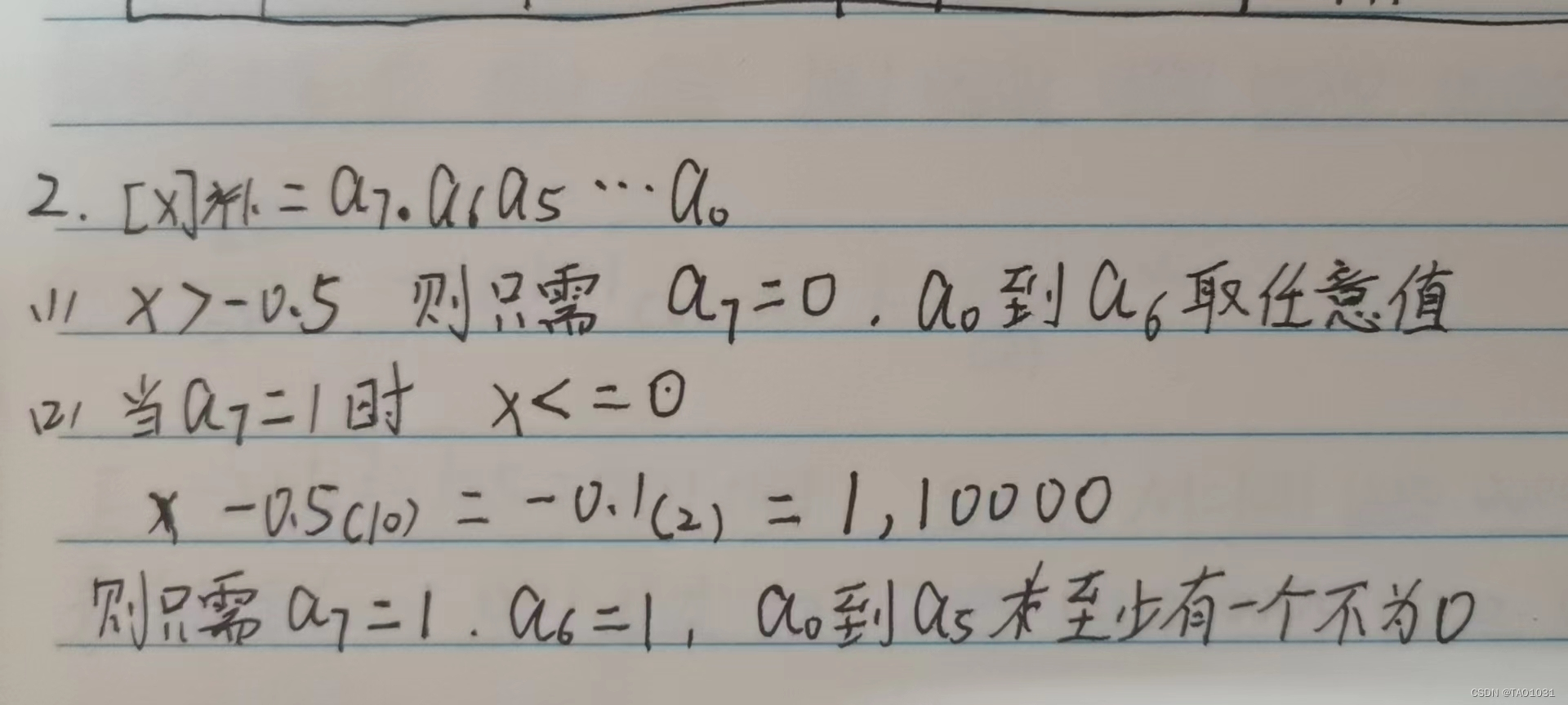

2. 设[x]补=a7.a6a5…a0,其中 ai 取 0 或 1,若要 x>–0.5,求 a0, a1, a2, …, a6 的取值。

3.

有一个字长为

32

位的浮点数,符号位

1

位;阶码

8

位,用移码表示;尾数

23

位,用补码表示;基

数为

2

。请写出:

(

1

)最大数的二进制表示;(

2

)最小数的二进制表示;(

3

)规格化数所能表示的数的范围。

4.

将下列十进制数表示成

IEEE754

标准的

32

位浮点规格化数。

(

1

)

27/64

(

2

)

–27/64

5.

已知

x

和

y

,用变形补码计算

x

+

y

,同时指出结果是否溢出。

(

1

)

x

=11011

,

y

=00011

(

2

)

x

=11011

,

y

= –10101

(

3

)

x

= –10110

,

y

= –00001

6.

已知

x

和

y

,用变形补码计算

x

–

y

,同时指出结果是否溢出。

(

1

)

x

=11011

,

y

= –11111

(

2

)

x

=10111

,

y

=11011

(

3

)

x

=11011

,

y

= –10011

7.

用原码阵列乘法器、补码阵列乘法器分别计算

x

×

y

。

(

1

)

x

=11011

,

y

= –11111

(

2

)

x

= –11111

,

y

= –11011

8.

用原码阵列除法器计算

x

÷

y

(注:先乘

1

个比例因子变成小数)。

(

1

)

x

=11000

,

y

= –11111

(

2

)

x

= –01011

,

y

=11001

9.

设阶码

3

位,尾数

6

位,按浮点运算方法,完成下列取值的[

x

+

y

],[

x

–

y

]运算:

(

1

)

x

=2

–011

×

0.100101

,

y

=2

–010

×(

–0.011110

)

(

2

)

x

=2

–101

×(

–0.010110

),

y

=2

–100

×(

0.010110

)

11.

某加法器进位链小组信号为

C

4

C

3

C

2

C

1

,低位来的进位信号为

C

0

,请分别按下述两种方式写出

C

4

C

3

C

2

C

1

的逻辑表达式:

(

1

)串行进位方式;(

2

)并行进位方式

12.

用

IEEE 32

位浮点格式表示如下的数:

(

1

)

–5

(

2

)

–1.5

(

3

)

384

(

4

)

1/16

(

5

)

–1/32

13.

下列各数使用了

IEEE 32

位浮点格式,相等的十进制是什么?

(

1

)

1 10000011 110 0000 0000 0000 0000 0000

(

2

)

0 01111110 101 0000 0000 0000 0000 0000

14.

32

位格式最多能表示

2

32

个不同的数。用

IEEE 32

位浮点格式最多能表示多少不同的数?为

什么?

15.

设计一个带有原码阵列乘法器(使用芯片)和原码阵列除法器(使用芯片)的定点运算器。

16.

设计一个

ALU

(

4

位),完成加、减、取反、取补、逻辑乘、逻辑加、传送、加

1

等

8

种运算功能