LPDDR是什么?

话不多说,先上大白话,一个网友总结的很好:简单地说DRR4是标准电压版的PC和服务器内存,LPDDR4属于手机等嵌入式移动设备使用的低电压低功耗内存,LPDDR4X则是LPDDR4的升级版,同等性能下功耗降低!

LP===Low Power

下面详细看看老哥的博客。

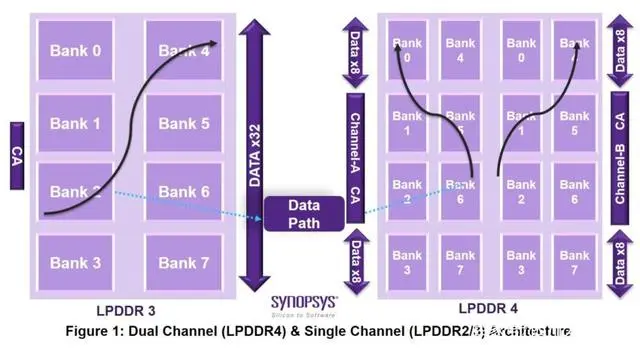

LPDDR4是与DDR4内存等效的移动设备。与DDR4相比,它具有更低的功耗,但是却以带宽为代价。LPDDR4具有两个16位通道,从而使每个DIMM的总线总长度为32位。相比之下,DDR4每个DIMM具有64位通道。

但是,与此同时,LPDDR4的预取宽度更宽,为16n,每个通道总共(16个字x 16位)256位/ 32字节,是两个通道总和的两倍。

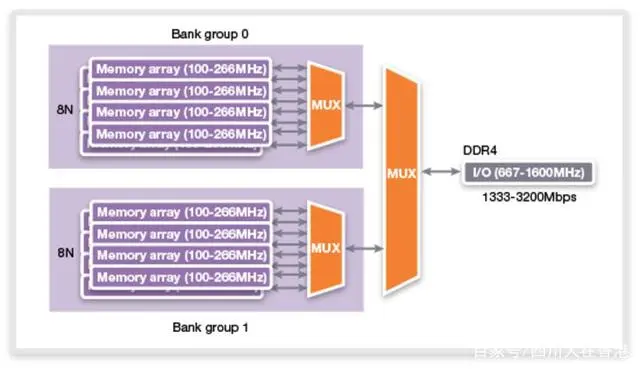

另一方面,DDR4每个通道具有两个8n预取存储体。这两个存储体是分开的,可以执行两个独立的8n预取。这是通过使用多路复用器对其内部存储库进行时分多路复用来完成的。每个组每个周期总共有8个字x 64位= 512位(64字节)。

与DDR4相比,LPDDR4降低了功耗,但这样做是以带宽为代价的。LPDDR4具有两个16位通道,从而形成了32位总总线。相比之下,DDR4具有64位通道。

LPDDR4还具有更灵活的突发长度,范围从16到32(256或512位,32或64字节),尽管大多数情况下使用16 BL。另一方面,DDR4被限制为每个周期8个突发长度(128位或16字节),尽管每个存储体都可以执行额外的传输(来自两个不同的存储体组)。

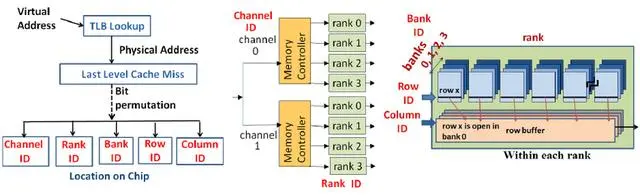

要了解突发长度的含义,您需要知道如何访问内存。

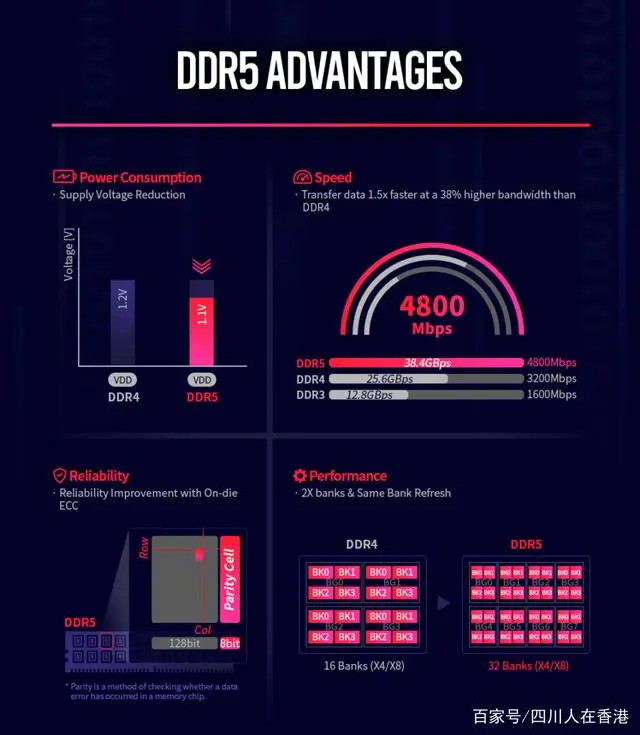

当CPU或高速缓存请求新数据时,该地址将发送到内存模块和所需的行,然后找到该列(如果不存在,则加载新行)。请记住,每步操作都会有延迟。之后,整列将以突发方式通过内存总线发送。对于DDR4,每个突发为8(或16B)。使用DDR5,它已增加到多达32个(最大64B)。每个时钟有两个脉冲串,它们以有效数据速率发生。此外,类似于LPDDR4,DDR5每个DIMM具有两个32位通道,而双DIMM配置中总共有四个通道。预取和BL也已增加到16。该数字非常理想,因为内存中的每个高速缓存行的大小都相同。

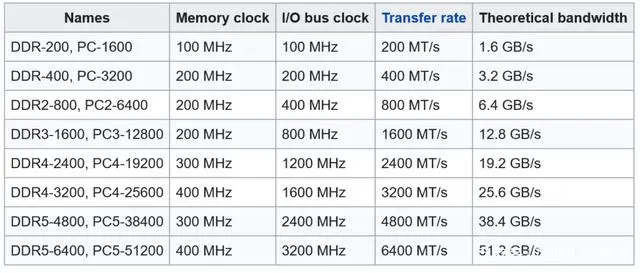

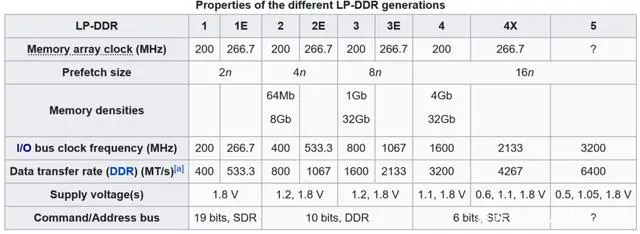

与标准DDR4内存相比,该设计使LPDDR4的电源效率更高,非常适合在电池待机时间长达8-10小时的智能手机中使用。美光的LPDDR4 RAM以2133 MHz的时钟达到了最高标准,传输速率为4266 MT / s,而三星紧随其后的是1600MHz的时钟和3200 MT / s的传输速率。此外,如您在下表中所见(来自Wikipedia),尽管LPDDR4(1.1v)具有类似或更高的I / O总线时钟,但其电压却比DDR4(1.3v)低得多。

低功耗DDR

最后,是存储库的问题。LPDDR4再一次针对低功耗性能进行了优化,而DDR4存储器则相反。DDR4内存由16个存储体组组成,每个存储体包装四个独立的存储体,而LPDDR4和LPDD4X DIMM每个通道总共具有八个存储体,因此总数为16(16位x 2)。LPDDR5采用类似于DDR4的结构,但这是另一次讨论。

LPDDR4与LPDDR4X:有什么区别?

类似于DDR5降低电压和功耗的方式,LPDDR4X的作用相同。它将I / O电压降低了50%(1.12至0.61v),从而大大降低了存储器以及存储器控制器的功耗。

此外,速度也从3200MT / s增加到了4266MT / s(无OC)。这是由于I / O总线时钟(1600MHz至2134MHz)和内存阵列(200-266.7MHz)更快的结果。命令和地址总线已保留有6位SDR空间。最后,它占用的片上空间更少,单个封装最多可以包含12GB的DRAM。不利的一面是,LPDDR4X不能与LPDDR4向后兼容。即使设备与更快的LPDDR4内存兼容,它也可能不适用于LPDDR4X。

DDR扫盲——DDR中的名词解析

-

AS: Row Address Strobe,行地址选通脉冲;

-

CAS: Column Address Strobe,列地址选通脉冲;

-

tRCD: RAS to CAS Delay,RAS至CAS延迟;

-

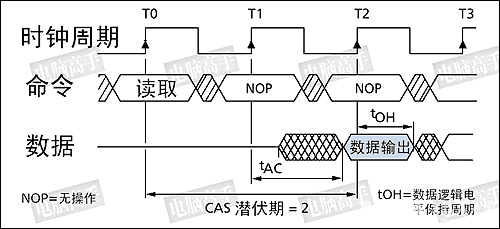

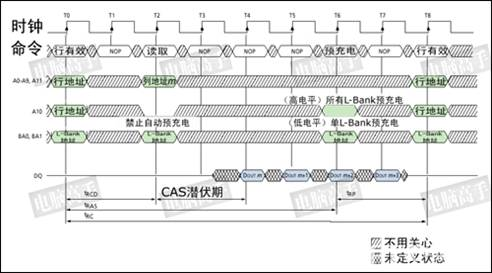

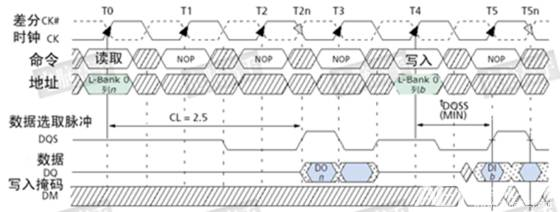

CL: CAS Latency,CAS潜伏期(又称读取潜伏期),从CAS与读取命令发出到第一笔数据输出的时间段;

-

RL: Read Latency,读取潜伏期;

-

tAC: Access Time from CLK,时钟触发后的访问时间,从数据I/O总线上有数据输出之前的一个时钟上升沿开始到数据传到I/O总线上止的这段时间;

-

tWR: Write Recovery Time,写回,保证数据的可靠写入而留出足够的写入/校正时间,被用来表明对同一个bank的最后有效操作到预充电命令之间的时间量;

-

BL: Burst Lengths,突发长度,突发是指在同一行中相邻的存储单元连续进行数据传输的方式,连续传输所涉及到存储单元(列)的数量就是突发长度(SDRAM),在DDR SDRAM中指连续传输的周期数;

-

Precharge:L-Bank关闭现有工作行,准备打开新行的操作;

-

tRP: Precharge command period,预充电有效周期,在发出预充电命令之后,要经过一段时间才能允许发送RAS行有效命令打开新的工作行;

-

AL: Additive Latency,附加潜伏期(DDR2);

-

WL: Write Latency,写入命令发出到第一笔数据输入的潜伏期;

-

tRAS: Active to Precharge Command,行有效至预充电命令间隔周期;

-

tDQSS: WRITE Command to the first corresponding rising edge of DQS,DQS相对于写入命令的延迟时间;

逻辑Bank

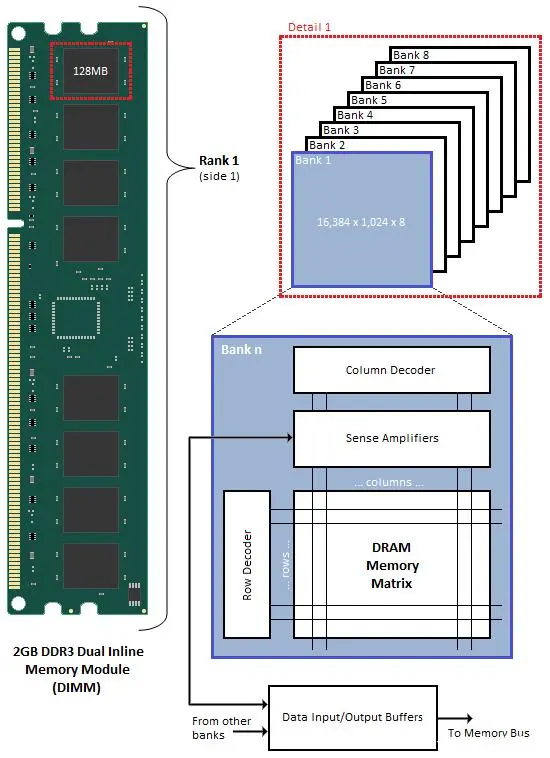

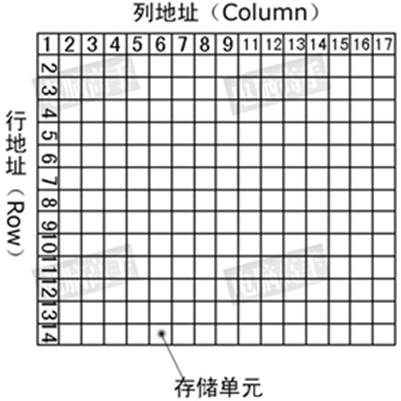

SDRAM的内部是一个存储阵列,要想准确地找到所需的存储单元就先指定一个(row),再指定一个列(Column),这就是内存芯片寻址的基本原理。

芯片位宽

SDRAM内存芯片一次传输率的数据量就是芯片位宽,那么这个存储单元的容量就是芯片的位宽(也是L-Bank的位宽);

存储单元数量=行数*列数(得到一个L-Bank的存储单元数量)L-Bank的数量也可用MW的方式表示芯片的容量,M是该芯片中存储单元的总数,单位是兆(英文简写M,精确值是1048576),W代表每个存储单元的容量,也就是SDRAM芯片的位宽,单位是bit;

-

DDR SDRAM内部存储单元容量是芯片位宽(芯片I/O口位宽)的一倍;

-

DDR2 SDRAM内部存储单元容量是芯片位宽的四倍;

-

DDR3 SDRAM内部存储单元容量是芯片位宽的八倍;

-

DDR4 SDRAM内部存储单元容量是芯片位宽的八倍。

参考资料:

https://mp.weixin.qq.com/s?__biz=MzA4NjQwNjMwOA==&mid=2650482661&idx=3&sn=78ffd8d0c704c5da4060eec9eb7fbc1d&chksm=87c6a22eb0b12b38514069f0ceff622cd20bd92c12d72ad5c049e8d0853b52f56d1529d1ffce&scene=27

https://baijiahao.baidu.com/s?id=1700533276647105969&wfr=spider&for=pc