1.前言

在于各个型号的单片机打交道的这几年越发清晰得发现学习一款单片机一定不能把它当作一个神奇的黑盒子,否则只能跑跑SDK带的例程,感动自己。经过在联盛德官网一通搜寻猛如虎下,终于找到了类似于参考手册和数据手册的文档,他们分别叫寄存器手册和产品规格书,下载连接如下:

链接:https://pan.baidu.com/s/1KG5hJetnraERyEQtrSYIdQ

提取码:SYHT

CSDN资源下载连接如下:

W801参考手册(寄存器手册),W801数据手册(产品规格书)-单片机文档类资源-CSDN下载

2.W801单片机里面有什么?各部分之间有何关系?

一般情况,在数据手册会有该单片机的总体功能介绍、管脚定义、电气特性等,可以从总体功能介绍中获知内部有什么。如下图(产品规格书第6页):

从图中上半部分可以看到,W801单片机里面有平头哥的XT804处理器,2MB的FLASH,288KB的SRAM, 蓝牙、WiFi以及他们公用的天线射频功放。下半部分有8通道的DMA,安全相关外设,SDIO主接口,PSRAM接口等等外设,均与我们在购买该芯片时的宝贝详情相符合,其余的就不一一介绍了。

这个图可以告诉我们W801里面有什么,但是要想用起来W801还是不够的,这幅图并没有明确表示各个部分之间的关系,于是我们需要看参考手册(寄存器手册43页),如下图:

从该图中可以看到W801单片机内部可以划分为两个由AHB总线矩阵连接起来部分,连部分之间通过总线桥相连接,其次仔细看会发现288KB的SRAM虽然在地址上是连续的,但实质上是由与AHB BUS1相连接的160KB和与AHB BUS2相连接的128KB两部分组成的,在使用时合理分配内存可以最大限度得减小总线上的延迟更加充分发挥处理器和外设的性能。例如,与计算相关的缓冲区应当放在AHB BUS1相连接的SRAM内,外设的输入输出缓冲区应当放在AHB BUS2相连接的SRAM内。

眼尖的朋友们可能第一眼看到这个图就发现AHB总线这个东西了,这是个老朋友,基于Cortex-M内核的单片机几乎都用这个,比如我们的老铁STM32,按经验来讲,既然有AHB,那APB必然不会缺席,就调那外设最多的地方,定能把他抓得住。果不其然,右下角一堆外设的框框上面赫然写着APB BUS。不过,好戏还没有结束,在这群外设里面找了一圈儿,发现”宝贝详情“里面介绍的几个牛逼外设怎么不见了,呜呜呜,不会被骗了吧?没有,他们在图左侧有自己独立的办公室,SDIO从接口和高速SPI单独使用外设总线连接AHB总线,SDIO主接口和PSRAM单独使用外设总线单独连接了AHB总线。

不得不说W801单片机设计的非常走心,这个格局让人不由得想起了牛逼哄哄的STM32H743,对比STM32H743的总线构架图如下:

STM32H743单片机同样使用了多个总线矩阵的设计,同样是每个总线矩阵都有自己的SRAM和APB连接外设,同样是将高速外设放置在CPU所在的总线,并且给高速外设从总线矩阵分配了高速接口而非通过APB总线。不过STM32H743还有一个优势,即每个总线矩阵都有各自的DMA,这样可以极大得降低在有大量数据从外设通过DMA输入或输出时,总线矩阵间的总线桥的压力。W801由于只有AHB BUS1有DMA,DMA在工作时需要通过总线桥才能完成工作,会占用总线桥大量带宽。

当然,这只是理论上的分析,实际情况是AHB总线带宽很高,在STM32F4或STM32F7上同时使用摄像头和LCD,并使用DMA实时接收摄像头图像并刷新显示到LCD时总线时若再增加其余大量的输入输出操作,如以太网功能等,才会出现总线卡壳的情况,这也是STM32H7系列直接上AXI总线的原因。反观W801,该单片机没有大吞吐量的外设,所以也无需给每个总线矩阵都给一个DMA 了。

最后,在两个文档中没有找到总线与设备的互联关系表,实属遗憾。通过该表可以清晰得知道每个具体的部分之间的连接关系,尤其要知道那些部分之间没有连接,这样可以避免在实际使用中出现莫名其妙的错误,比如STM32H743的SDMMC1躲猫猫问题,最后看了互联关系表才发现,SDMMC1就根本没有连接我的缓冲区所在的SRAM。

既然没有找到这个图,那就把希望寄托在SDK上面吧,乖巧跟着SDK走好了。

至此,W801的内部结构分析完毕。

3.W801的内存映射

W801作为一个32位单片机与32位单片机众生一样,具有32位的直接寻址范围,范围之大,再多外设都装得下,如下图(寄存器手册48页):

从图中可以看到,W801当前只使用了Block0、Block1、Block2这三个块,还有三个块保留没有使用。其中外设部分的地址映射我们可以直接交给SDK,而FLASH和SRAM的映射我们需要仔细看。

首先是FLASH,首先是从0X0000_0000地址开始的启动扇区,这部分存储的代码是出厂就有的,这部分代码负责在正常运行状态下引导单片机从0X0800_0000地址开始的FLASH启动,或是在更新固件状态下引导单片机从串口更新固件,例如在使用配套软件Upgrade Tools时就需要这样做。我们写的代码会存储在起始地址为0X0800_0000的那个FLASH里面,这个FLASH也正是”宝贝详情“里面说得2MB的那个大FLASH。

其次时SRAM, 书接上文,SRAM实际是两部分,这幅图中的"SRAM 160K"是上文提到的连接在AHB BUS1上的那个SRAM,”Mac SRAM 128K“是上文提到的连接在AHB BUS2上的SRAM。可以看到地址确实是连续的,且分界线为0X2002_8000。然后是外部扩展PSRAM,这个我个人认为不太能用到,因为W801加上背板页不过58个引脚,再剪掉供电用的引脚剩下的就很少了,接个PSRAM的话外设几乎没得接了,所以在通常的使用场景下也用不到这个PSRAM。

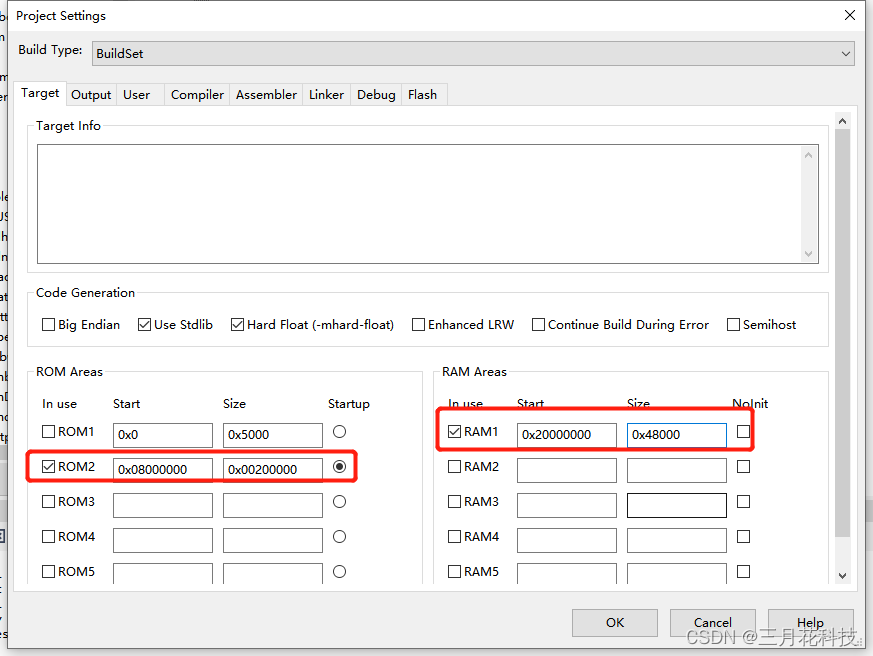

最后,分析完图,我们回到CDK的工程,在CDK工程中的设置界面中的Target页有如下的设置:

红色框框中的内容正是对应了映射表中FLASH 和SRAM的配置,为了方便使用可以把两部分SRAM分开写在不同的地方, 这个界面和KEIL5的几乎一样,因此这里就直接用KEIL5给大家举例子了:

在设置时,除了需要仔细确认地址是否正确外,还需要谨慎每个RAM和ROM前面的复选框,即CDK中的In use选项和KEIL5中的default选项,这个选项将会决定从哪个ROM启动,并将哪个RAM作为主堆栈。例如在启动初期,外部扩展内存控制器还未初始化,若将主堆栈选择在了外部扩展内存,将无法启动。

这样一通操作后,KEIL5的话就可以直接在右侧的工程树状图中选择分组或者单个文件规定其存放位置,不过CDK的话,emm不行,哈哈。看到这的朋友不要生气哈,期待后续更新版本的CDK加上这个功能。

在实际配合SDK使用时,会发现,好像在Target页面设置的东西根本用不到,这是因为SDK之际写了一个分配存储的文件,类似于KEIL5的分散加载文件,在Link界面可以看到该设置:

若选择2处,则使用Target页面的设置,而SDK默认选择的1处,配套使用的箭头所指的文件,可以按右边放大镜图表的按钮来查看此文件 。该文件开头部分如下:

可以看到该文件开头分了I-SRAM、D-SRAM和V-SRAM,三类,从地址可以看到D-SRAM就是前面提到的两部分SRAM的合体,V-SRAM就是外部扩展PSRAM。其次,下方这个框决定了堆大小,注意,这个堆是处理器在内核级模式下使用的,即全局变量和malloc申请的内存存放的地方,在实时操作系统中,实时操作系统申请的内存不在这个范围内,注意不要混了!

4.上电跑一下吧

终于到这个紧张刺激的环节了,不过跑前需要先热个身,具体是,跑多快,怎么跑两个问题。针对这个问题,需要查看单片机的时钟树,W801的时钟树如下图所示(寄存器手册47页):

从图中可以看到,W801单片机有一个倍频器,倍频后通过各级分频器将时钟信号分配给XT804处理器,内存,外设等。时钟方面的设置正是需要配置一个倍频器和图中所示的那些分频器。这个工作以及在SDK中做好,我们可以直接躺赢,不过注意,SDK中默认处理器工作在80MHZ,我们需要通过设置将其修改为240MHZ,具体修改方式为打开文件wm_main.c,找到main函数,找到如下函数调用,并修改参数。wm_main.c文件寻找方式,及修改内容如下图:

修改好后,编译,下载即可运行。

5.下期预告

SDK的启动流程,以及部分文件的修改尝试。