有机会用瑞芯微做EP,X86做RC ,调试两者建立连接。

环境配置

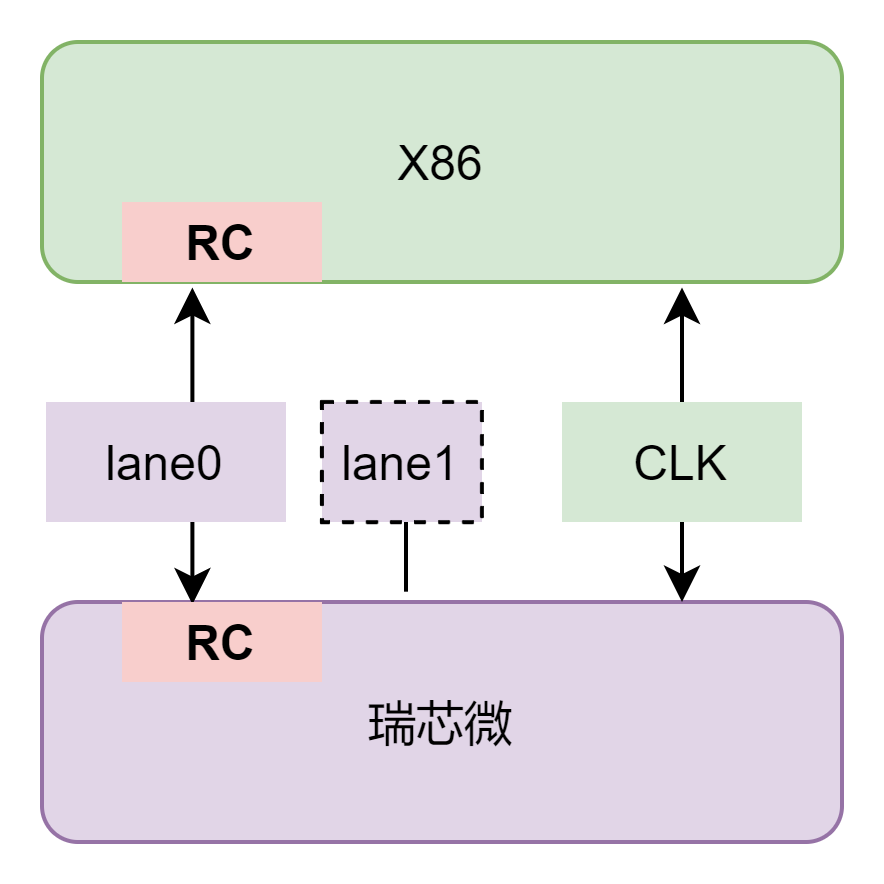

如图所示,两块单板,期望瑞芯微做EP,X86做RC,两者能够互联。

LINK 配置过程

主要配置瑞芯微

瑞芯微的芯片配置,在配置EP模式时,分为控制器和PHY两部分,两部分都需要配置为EP模式。

由于软件代码的bug,导致PHY的部分时钟工作的RC模式,并且配置时钟来自芯片本身,而非对端送过来的。于是乎导致实际环境中两个RC进行互联。

现象之瑞芯微EP侧

通过对瑞芯微单板进行复位,通过寄存器查看PCIE连接已经建立,相关寄存器为:

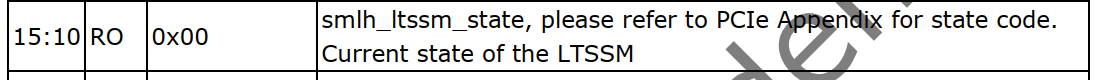

值为 0x4407,也就是物理层和数据链路层都被设置为1,都link了,并且LTSSM为0x11,根据瑞芯微手册说明,

也就是进入了连接状态。

现象之X86 RC侧

x86侧相关寄存器

在瑞芯微单板复位过程或者复位过后的2分钟左右的时间内,我们看到此寄存器的变化情况如下:

50: 00 00 11 38 00 b2 5c 00 00 00 48 01 08 00 00 00 (8 表示在link traing,3 bit29 表示已经link active)

50: 00 00 11 30 00 b2 5c 00 00 00 48 01 08 00 00 00 (link training为0,同时link up为1,表示已经进入L状态)

50: 00 00 11 38 00 b2 5c 00 00 00 48 01 08 00 00 00 (此处很快又进入link traing状态)

50: 00 00 11 30 00 b2 5c 00 00 00 48 01 08 00 00 00

50: 00 00 11 38 00 b2 5c 00 00 00 48 01 08 00 00 00

50: 00 00 11 38 00 b2 5c 00 00 00 48 01 08 00 00 00

50: 00 00 11 38 00 b2 5c 00 00 00 48 01 08 00 00 00

50: 00 00 11 10 00 b2 5c 00 00 00 48 01 08 00 00 00 后续一直link traing ,直到此时没有再traing,说明对端已经起来了。没又link traing的对象了!

通过上述寄存器变化,可以得知,X86侧看到的PCIE link状态为短暂的link (offset 0x53值为0x30时),而后大部分时间在0x38这个状态,也就是一直在link training。

LTSSM状态变化与对应寄存器的关系

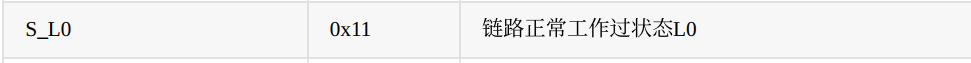

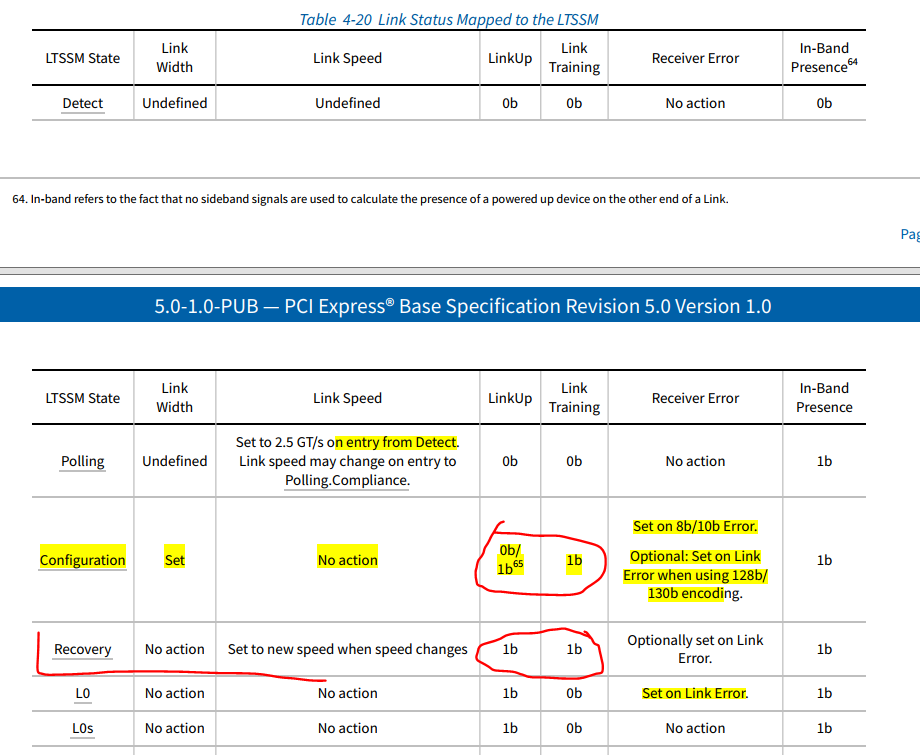

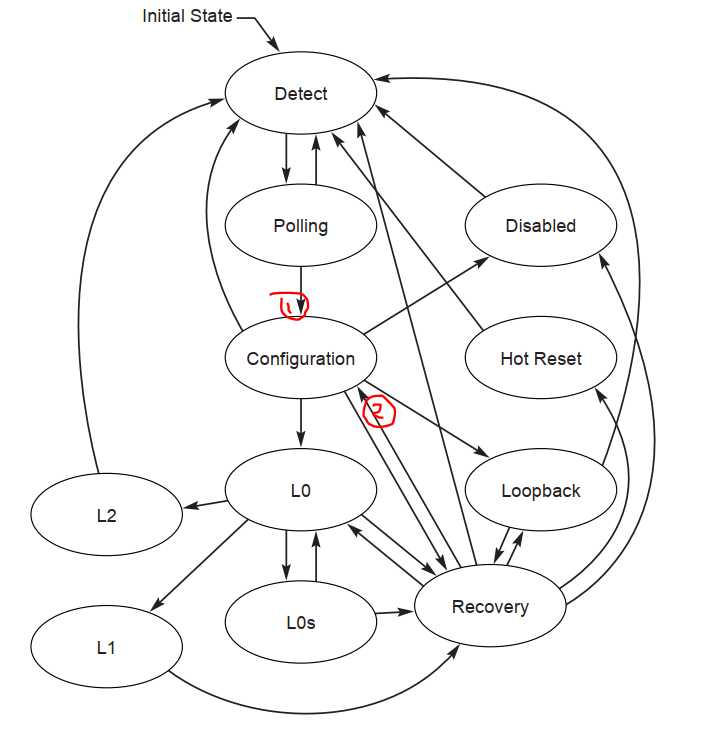

翻看PCIE协议,其中 当link up 1 并且 link training 也为1时,只有configuration和recovery两个状态。

而通过上面65标识文字及下面转换图,可以得到从Recovery进入configuration时才被设置为1。

于是我们想是什么导致 LINK 从Lx 状态变化到了Recovery状态 ?

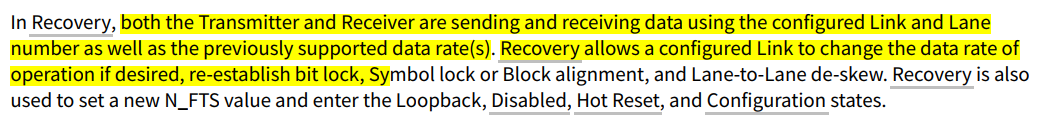

Recovery状态进入

通过上述发现后,我们在瑞芯微一侧持续跟踪连接状态,发现其LTSSM也在recovey的几个状态和L0之间转换

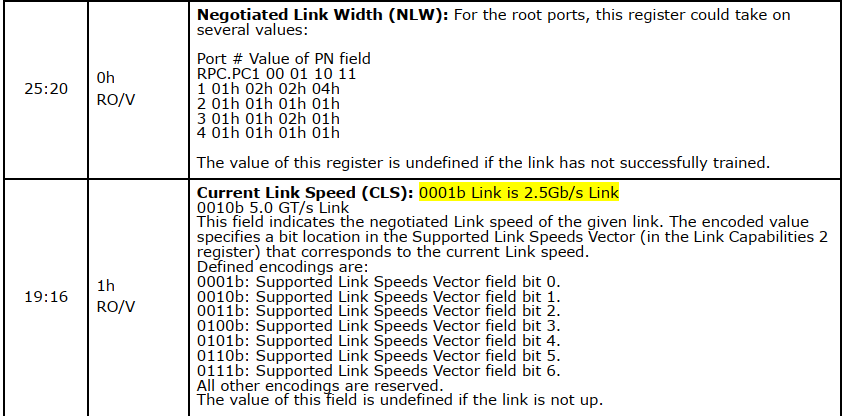

速率、带宽的改变是主要功能

然而我们已经配置X1 GEN1。

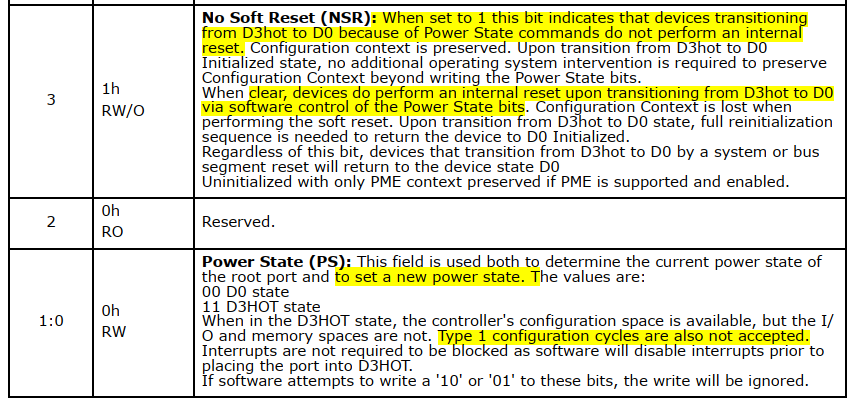

X86 桥片NSR功能

PCI Power Management Control

在实验过程钟,怀疑PCIE端口的电源状态相关,于是将其改配

setpci -s 0:1c.0 a4.b=0x8

如果写0,则下挂设备会跟着复位。注意。

rescan功能

1)在第二节的配置,LINK不稳定的情况下,我们通过lspci -vt命令可以看到对应的桥片端口信息如下:

+-1c.0-[01]----

虽然看到了桥片PCIE端口,但是看不到设备。

2)在第二节看到连接状态为0x30 0x38时,我们通过下面命令,

/sys/bus/pci/devices/0000:00:1c.0# echo 1 >rescan

此时,再查看lspci -vt

+-1c.0-[01]----00.0 Fuzhou Rockchip Electronics Co., Ltd Neural Network Processor Card

3)即可以看到设备信息,进而可以读取此设备的配置空间寄存器信息

lspci -xxx -s 1:0.0

10: 00 00 00 3c 00 00 00 00 00 00 00 00 00 00 00 00

20: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

4) 此时虽然看到了设备,但是0x10 bar0 寄存器的值并非X86地址空间的地址,而是原始瑞芯微芯片的地址。说明rescan并没有给设备分配地址,这也情有可原,毕竟其上游端口也没地址可分。

总结

我们纠结于 LTSSM状态机苦寻无果,而最终走读代码发现由于两侧都配置为RC导致了上述的现象。

至于为什么在此种配置下会llink training几分钟,而不是几十分钟后续再进一步探索。

intel 是否有寄存器直接指示LTSSM状态变化?还好此款桥片支持LINK状态查询,即寄存器的link active 位。