上一篇文章对rocketchip整个调试部分的硬件相关内容进行了梳理,这篇本章对debug_clock和debug_reset这两个dmInner的时钟复位SoC集成的方法进行分析,并给出一个参考的SoC级集成方案,并讨论下基于该连接方案的原因。

阅读本篇文章前,建议先阅读上一篇文章:

一、debug_clock

debug_clock must be synchronous to clock. The clock gate formerly in dmInnerAsync now resides outside the debug module in customer logic.

Customer logic can call connectDebugClockAndReset to achieve the same functionality as before.

debug_clock和debug_reset是新版rocketchip多出的顶层信号,该信号作为dmInner的时钟和复位。按照官方的信号说明,dmInner在旧版的时钟是经过内部处理得到,而新版本将其交由SoC集成的芯片设计人员处理。这里先看下旧版的dmInner时钟和复位是怎么处理的,如下图所示:

可以看出,dmInner的时钟受clock gate控制,clock gate使能信号由reset和dmactive控制,这也说明了官方的第二句话的含义,也就是说老版的dmInner时钟来自core clock,但是内部进过clock gate控制时钟有效,在复位有效(core处于复位状态)或调试复位释放(JTAG工作)的时候,core的clock会送给dmInner,其他时间关闭时钟降低功耗。

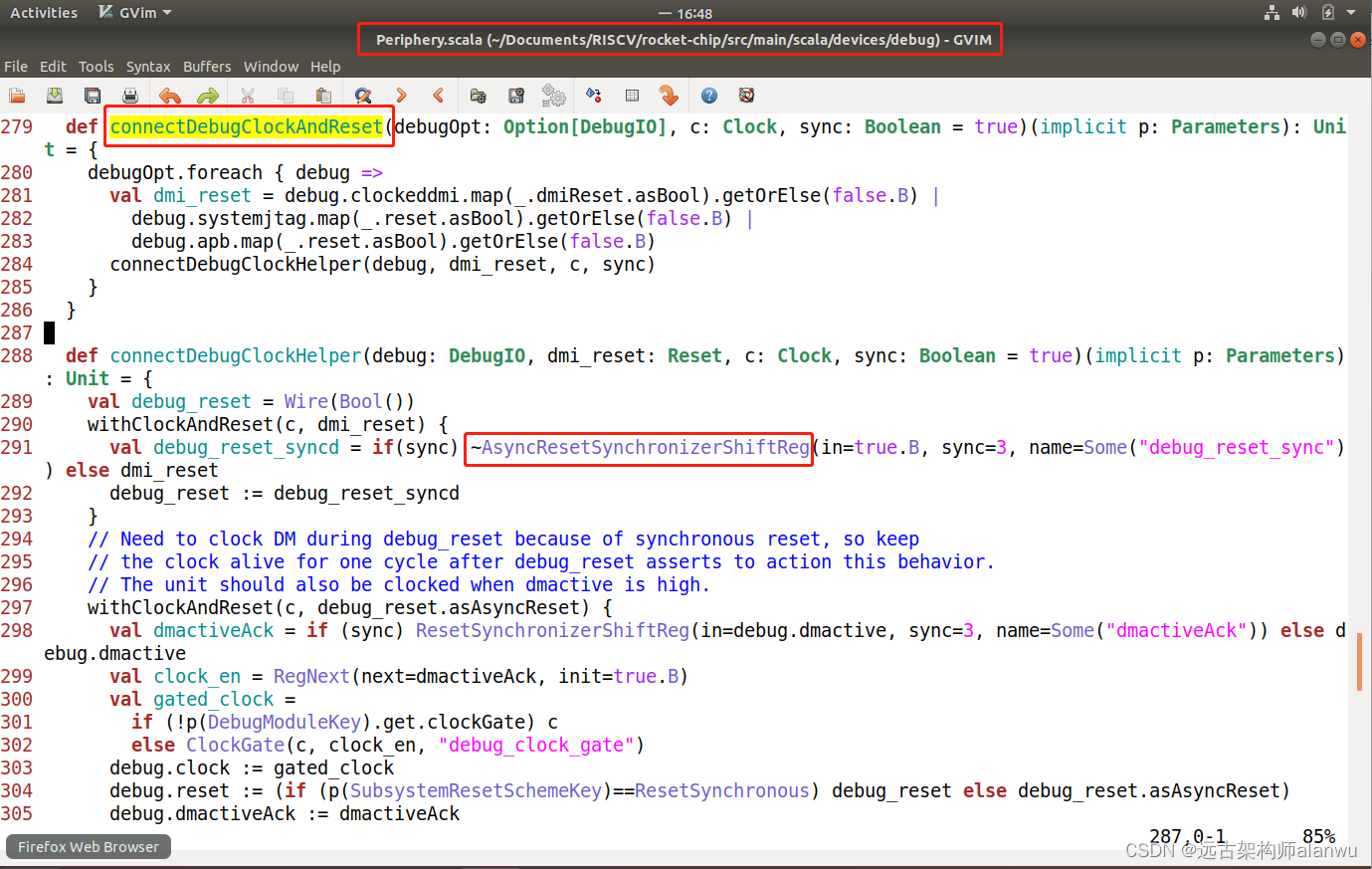

对于官方的第三句话,connectDebugClockAndReset可以在rocketchip文件夹里找到它的实现方式:

实际上就是调用了AsyncResetSynchorizerShiftReg模块来完成了上述的异步复位同步的处理,这个模块在代码里很好找到,是个被反复调用很多次的基础库模块。

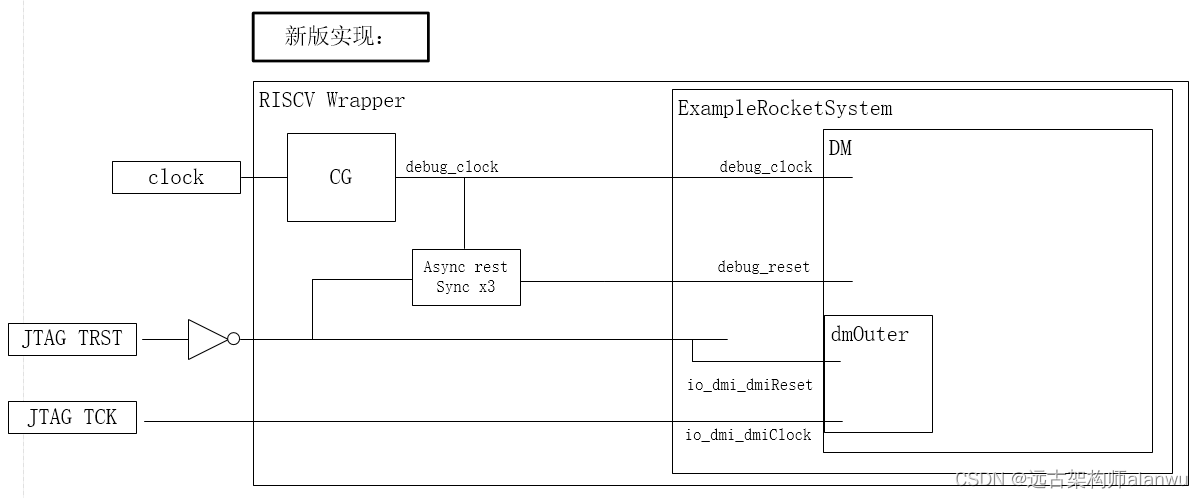

这里给出一种新版的debug_clock和debug_reset处理方法,实际上就是参考老版本连接信号:

也可以不按照参考设计连接,clock的使能也可以按照系统需要进行使能,但一定要保证core clock和debug clock同步关系。除此之外,官方参考的使能连接方法,后面会对其达到的目的进行解释。

二、debug_reset

dmi_reset must be asynchronous.

debug_reset may be either synchronous or asynchronous but its deassertion must always occur either when debug_clock is stopped or synchronously to debug_clock.

dmi_reset必须是异步复位,这是因为该复位实际上就是dmOuter的复位,而复位的来源是JTAG的复位,因此该复位是异步的。dmOuter和DTM模块内部,也是异步复位的设计,而dmInner是同步复位的设计。

debug_reset新版的要求是可以同步或者异步,如果同步可以同步到core reset,如果是异步的话可以直接接JTAG的复位,但如果是异步复位,该复位要同步到debug_clock释放,先看下旧版的debug_reset的实现方式:

旧版的dmInner的时钟复位直接连接的core clock和core reset,也就是和内核的时钟复位同步,内核复位时,会同时复位dmInner部分。除此以外,dmOuter的时钟和复位来自JTAG,且异步复位同步释放。

下面给出一种debug reset的处理方法,强烈建议按照该方法处理debug reset:

这里详细讨论不接core reset同步的原因,因为新版增加了core复位释放立即进debug调试的功能,也就是halt on reset功能,该功能是RISCV官方文档要求必须实现的功能之一。

该功能具体实现就是haltIsInReset输入信号,具体会在后续章节详细描述。由于该功能的加入,需要在core复位期间保持dmInner处于工作状态,保证core复位引起debug interrupt拉高有效,该中断拉高经过dmInner和dmOuter,最终给到hart核心。因此,在core复位期间,一定不能将dmInner复位,否则会导致halt on reset功能无法实现!

接TRST需要在上电复位时保持TRST复位状态,但是由于dmInner的需要同步复位,因此需要在上电复位时提供debug_clock时钟,保证该复位有效。

三、需要注意的几点

总结一下,这里有几个地方需要注意:

- debug_clock时钟必须和core clock时钟同步,但clock gate使能可以根据系统需要进行设计;

- dmInner模块是个同步复位模块,其复位有效必须需要debug_clock的时钟;

- DTM和dmOuter模块是异步复位模块,其复位可以是异步的,但复位的释放最好同步;

- dmInner如果没有时钟,初始状态下,reg和memory是random值,这个random值可能会影响debug interrupt和ndreset拉起,从而影响core正常工作,因此上电复位最好保持dmInner在复位状态;

- debug_reset必须和core_reset异步,且保持core在复位时dmInner能正常工作,这点会在后续详细描述。