(大疆2020数字IC)

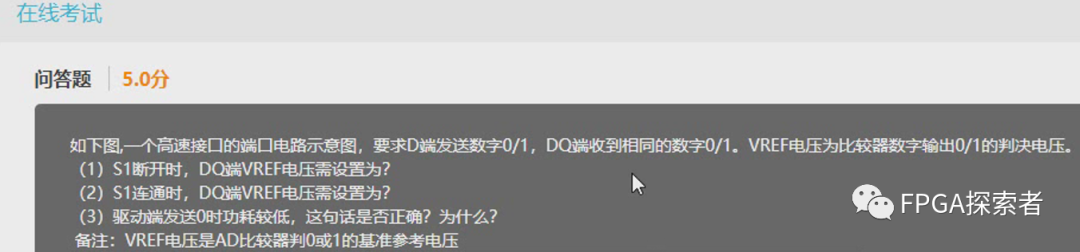

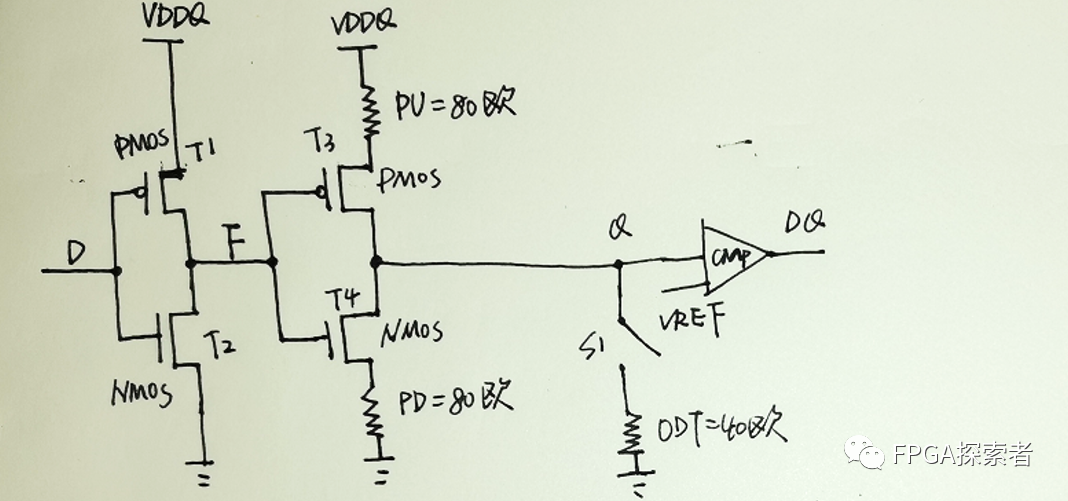

如下图,一个高速接口的端口电路示意图,要求D端发送数字0/1, DQ端收到相同的数字0/1. VREF电压为比较器数字输出0/1的判决电压。

(1)S1断开时,DQ端VREF电压需设置为?

(2)S1连通时,DQ端VREF电压需设置为?

(3)驱动端发送0时功耗较低,这句话是否正确?为什么?

备注:VREF电压是AD比较器判0或1的基准参考电压

答案:

(1)S1 断开时:

若 D 为 1,Q 端电压为 VDDQ,VREF 小于 VDDQ;

若 D 为 0,Q 端的电压为 0,VREF 要大于 0,因此 0<VREF<VDDQ;

扫描二维码关注公众号,回复:

14663777 查看本文章

(2)S1 连通时:

若 D 为 1,Q 端电压为 VDDQ /3 ;

若 D 为 0,Q 端的电压为 0,因此 0<VREF<VDDQ/3 。

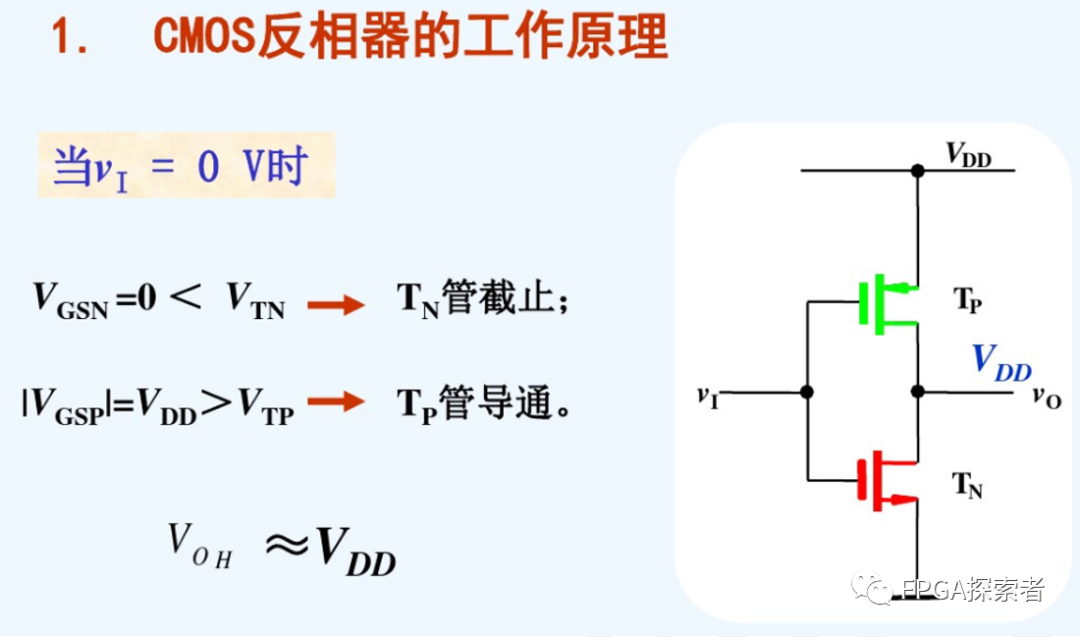

(3)驱动端为 0 时,NMOS 管导通,反相器输出接地,电阻上没有电流,因此功耗较低。

解析:

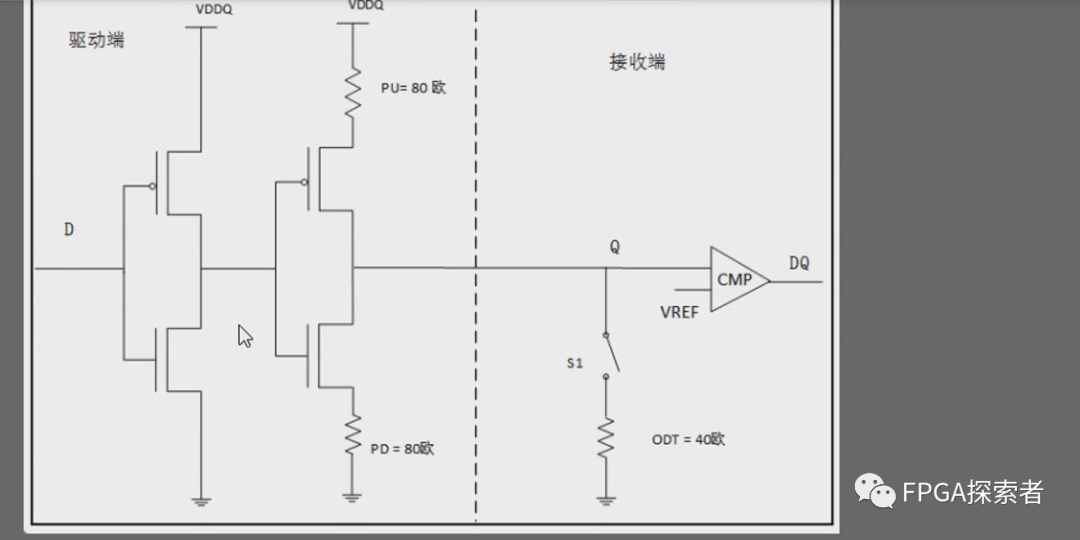

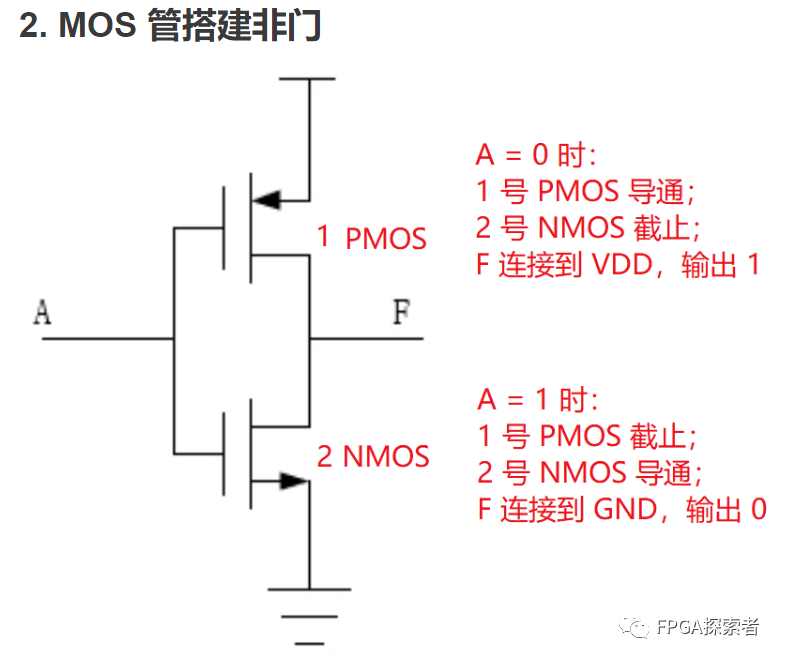

对于图中的表示方法,可以看下图最后两幅图,NMOS和PMOS。

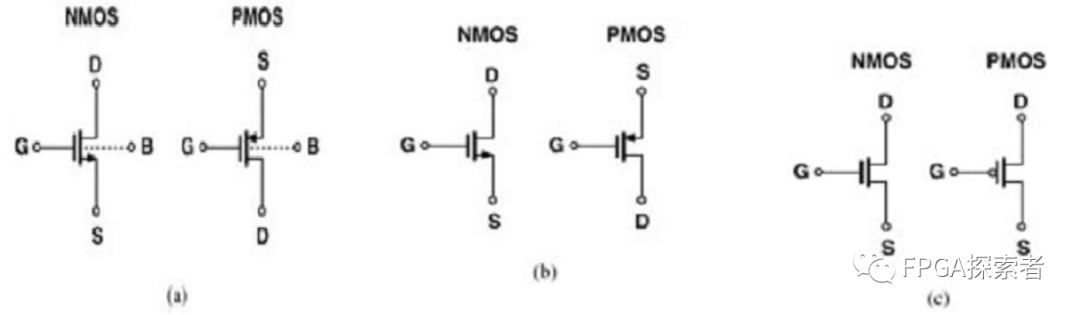

等效电路如下图所示:

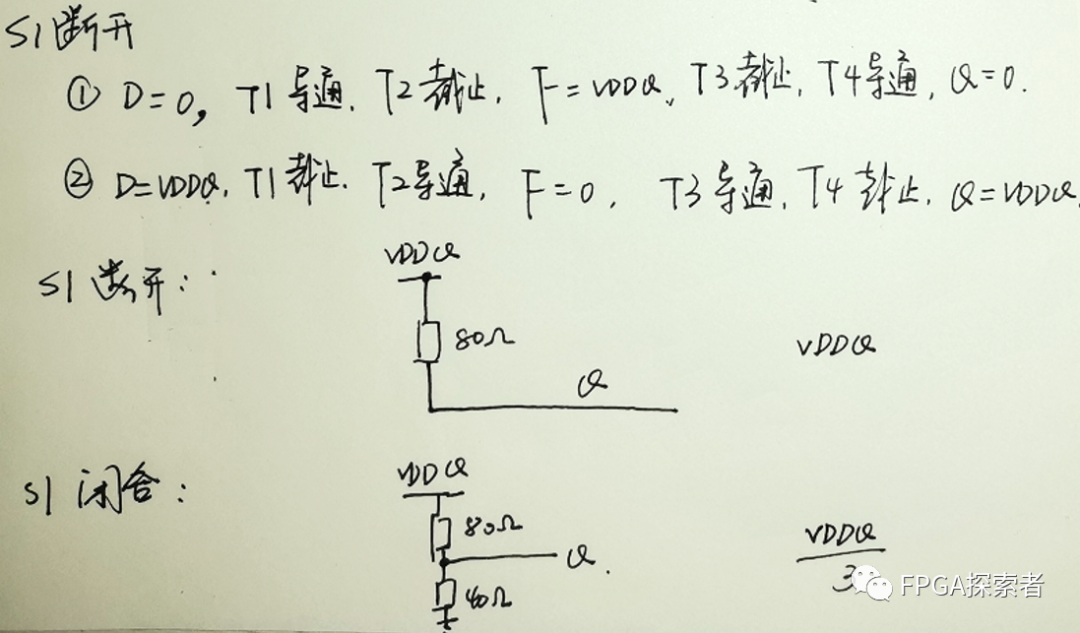

S1断开时,相当于直接经过上拉电阻80欧姆输出;

S1闭合时,有 40 欧姆分压;

【往期精彩】

2022届提前批汇总

2022届FPGA/数字IC交流

最新面经汇总

笔试面试