目录

一、makefile的介绍

- 在linux和unix中,有一个强大的实用程序,叫 make ,可以用它来管理多模块程序的编译和链接,直至生成可执行文件

- make程序需要一个编译规则说明文件,称为 makefile ,makefile文件中描述了整个软件工程的编译规则和各个文件之间的依赖关系。

- makefile就像是一个shell脚本一样,其中可以执行操作系统的命令,它带来的好处就是我们能够实现“自动化编译”,一旦写好,只要一个make命令,整个软件功能就完全自动编译,提高了软件开发的效率

- make是一个命令工具,是一个解释makefile中指令的命令工具,一般来说大多数编译器都有这个命令,使用make可以是重新编译的次数达到最小化

二、makefile的编写

makefile文件的规则可以非常复杂,比C程序还要复杂,初学先了解它的简单用法

vim makefile创建文件

文件名:makefile,内容如下:

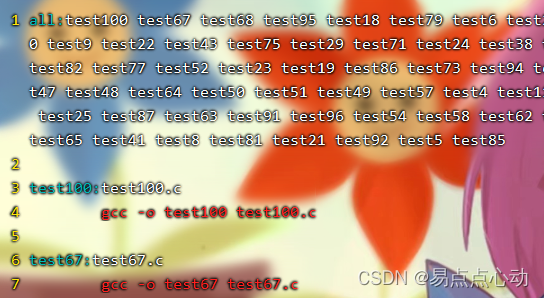

- 第1行 :all: test100 test67 ......

- all: 这是固定的写法

- test100 test67表示需要编译目标程序的清单,中间用空格分隔开,如果清单很长,可以用 \ 换行

- 第3行 : test100:test100.c

- test100:表示需要编译的目标程序。

- 如果要编译目标程序test100,需要依赖源程序test100.c,当test100.c的内容发生了变化,执行 make 的时候就会重新编译 test100

- 第4行:gcc -o test100 test100.c

- 这是一个编译命令,和在操作系统命令行输入的命令一样,但是要注意一个问题,在gcc之前要用 tab 键,看上去像8个空格,实际不是,一定要用tab,空格不行

- 第300行: clean:

- 清除目标文件,清除的命令由第301行之后的脚本来执行

- 第301行:rm -f test67 test68 ......

- 清除目标文件的脚本命令,注意了,rm之前也是一个 tab 键,不是空格

三、make命令

makefile 准备好了,在命令提示符下执行 make 就可以编译 makefile 中 al l参数指定的目标文件

执行make编译目标程序:

因为全部的目标程序都是最新的,所以提示没有目标可以编译

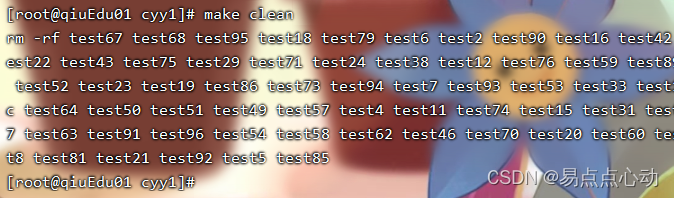

执行make clean,执行清除目标文件的指令

修改 makefile 里面的程序文件,随便改点什么,只要改了就行

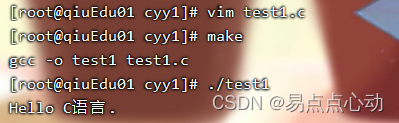

比如我们vim test1.c,打开之后顺便改点什么,加个空格都行

然后再执行 make:

四、makefile文件中的变量

- makefile中,变量就是一个名字,变量的值就是一个文本字符串

- makefile中的目标,依赖,命令或其他地方引用变量时,变量会被它的值替代

举个例子

- 第1行:CC=gcc ,定义变量CC,赋值gcc

- 第2行:FLAG=-g,定义变量FLAG,赋值-g

- 第7行:$(CC) $(FLAG) -o test1 test1.c

- $(CC)和$(FLAG)就是使用变量CC和FLAG的值,类似于C语言的宏定义,替换后的结果是:

- gcc -g -o test1 test1.c

编译效果:

在makefile文件中,使用变量的好处:

- 如果在很多编译指令采用了变量,只要修改变量的值,就相当于修改全部的编译指令

- 把比较长的、公共的编译指令采用变量来表示,可以让makefile更简洁

作者有话要说

- 到这里 Re:C语言 的专栏就已经结束了,这篇专栏从2022-08-07开始写的,到现在已经过去81天,写了将近3个月哈哈。

- 这篇专栏包括C语言90%的基础知识,都是非常精华的内容,后面的话我觉得好用的知识再做补充。

- 如果你认真看完这篇专栏,相信你的C语言水平已经有3成了,基础的话算入门了。接下来我会开始写C++的相关知识,有C的基础去学C++的话会轻松很多的