声明:作者是做嵌入式软件开发的,并非专业的硬件设计人员,笔记内容根据自己的经验和对协议的理解输出,肯定存在有些理解和翻译不到位的地方,有疑问请参考原始规范看

高速数据传输以突发传输(bursts)方式进行。为了帮助接收端做同步,在发送端的data bursts会使用一个前导(leader)序列和一个尾部(trailer)序列进行扩展,这些序列在接收端要能正常去掉,不对实际数据造成影响。因此前导和尾部序列只能在传输线上被看到。

数据传输起始点和结束点都是Stop状态。在突发传输之间的间歇中,Data Lane要保持在状态,除非在Lane上出现了Turnaround或Escape请求。在一次HS Data Burst传输中,Clock Lane要处于High-Speed模式,提供DDR时钟到Slave侧。

Burst Payload Data

一次burst的载荷数据最小长度是1个字节,多于1个字节必须是字节的整数倍。需要注意的是对于长度较短的burst,除去有效载荷数据,Start和End的开销会非常大。PHY并没有明确数据的最大字节数。但在PHY里面,处于HS data burst的时候,并没有自动恢复错误的方法,实际的BER不可能为0。因此对于每种协议来讲,如何考虑最佳的burst长度是非常重要的。

Start-of-Transmission

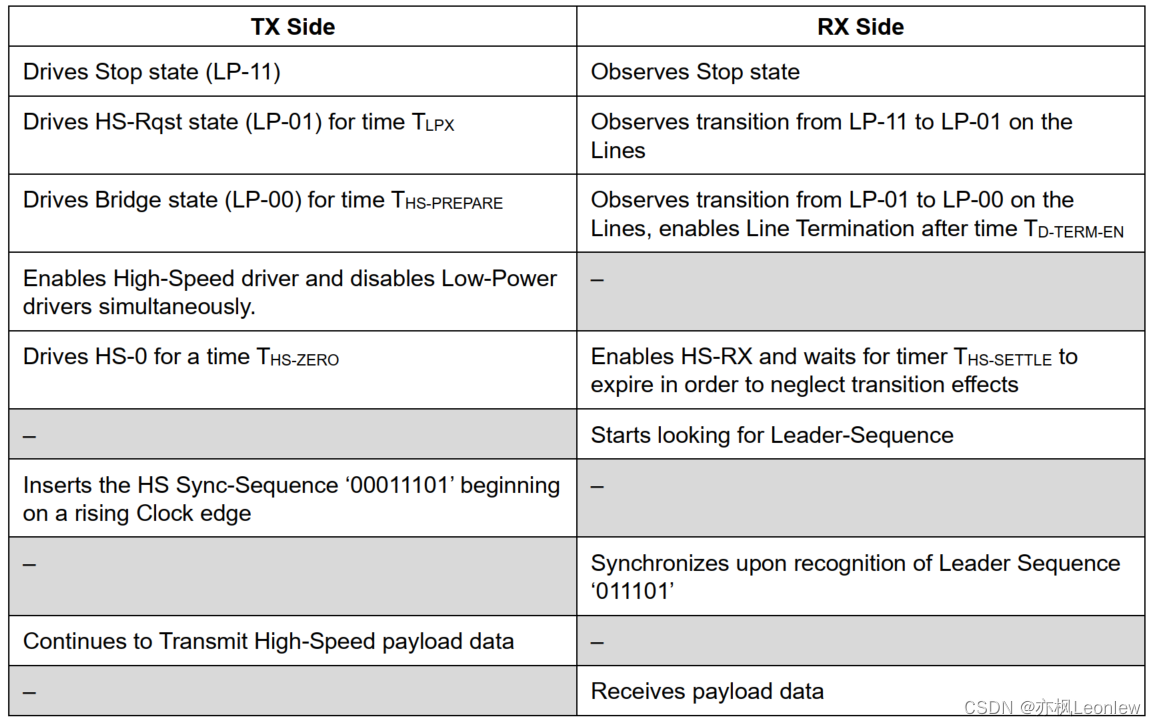

Transmit请求之后,Data Lane退出Stop状态,并且通过一个SoT(Start-of-Transmission)过程来准备High-Speed模式。下面的表格描述了SoT过程中TX和RX侧的事件顺序:

图1 Start-of-Transmission序列

End-of-Transmission

在一次Data Burst结束的时候,Data Lane离开High-Speed Transmission模式,通过一个EoT(End-of-Transmission)过程来进入Stop状态。下表展示了EoT过程中可能发生的事件序列(注意:EoT的处理可以被协议层或D-PHY处理):

图2 End-of-Transmission序列

HS Data Transmission Burst

图3 High-Speed Data Transmission in Bursts

上图展示了在一次Data Burst的传输过程中的事件的序列。从协议上讲,任意一条Lane可以独立地启动和停止传输。但在实际中,对绝大多数应用程序而言,所有Lane会同步启动数据传输,但Lane可能会在不同的时间点上结束,这是因为每条Lane实际传输的字节数可能是不同的。

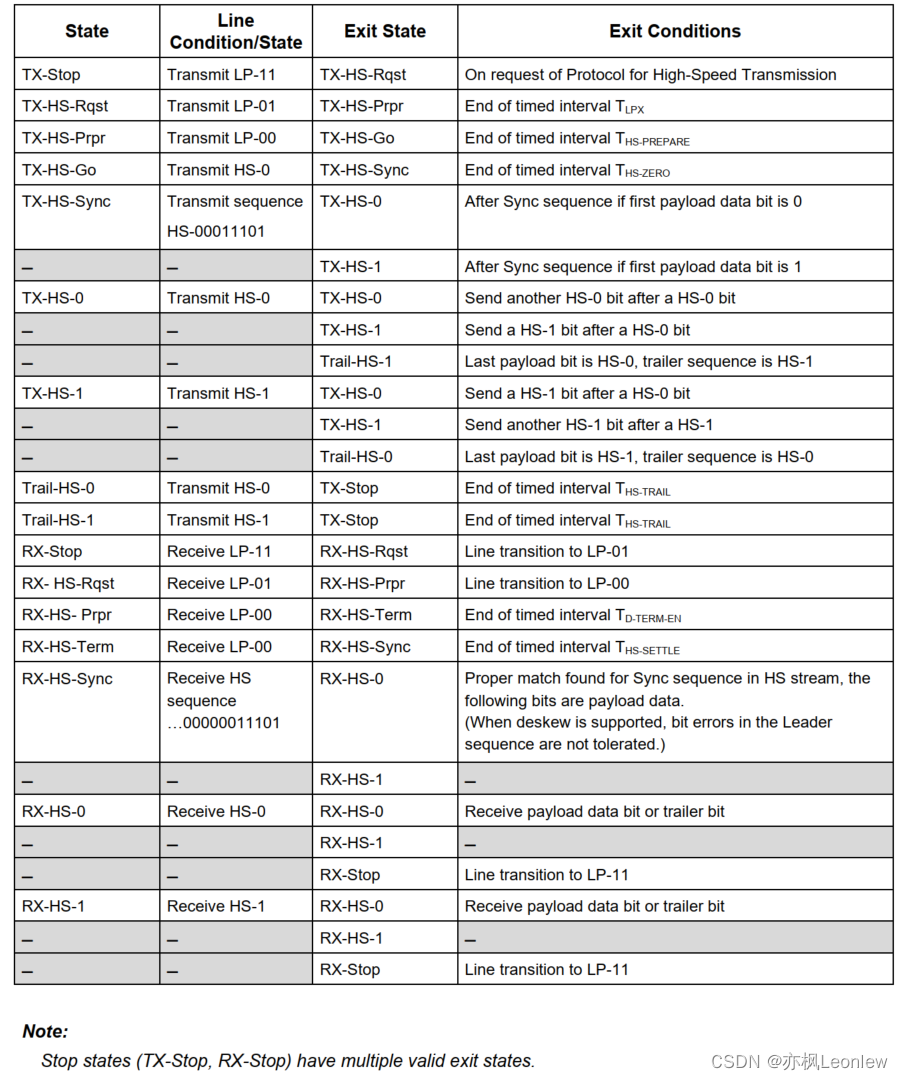

图4 High-Speed Data Transmission的TX和RX状态机示意图

图5 High-Speed Data Transmission状态机描述

ALP模式和HS Transmission Burst

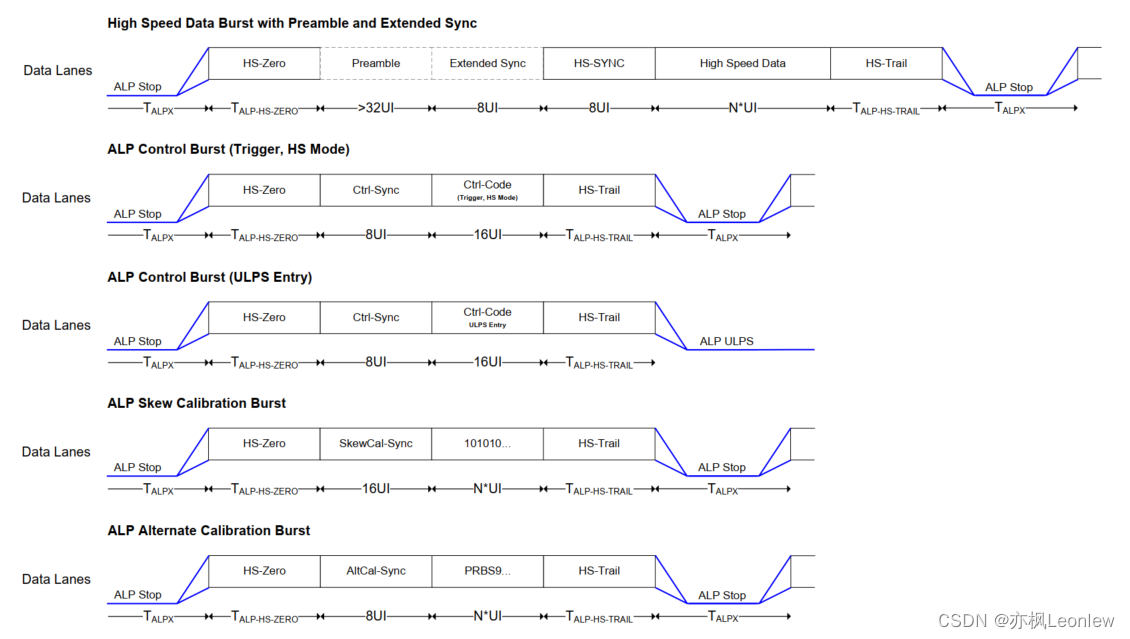

图6 - ALP Mode General Burst Format

上图展示了ALP模式的一般burst格式。Clock和Data Lane初始都在ALP Stop状态。如果处于ALP ULPS状态,则Lane在尝试任何其他通信前,会发起一个初始的状态转换到ALP Stop状态。ALP Stop和ALP ULPS状态本身和LP模式的Stop和ULPS是非常类似的。

发送端会驱动ALP Wake脉冲维持住一段时间来唤醒接收端。这种状态和HS burst起始时的HS-Zero状态类似,并且要持续一个周期。ALP-ED检测到ALP Wake脉冲,差分端接(differential termination)被启用。在唤醒后,根据数据速率,发送端发送1010...前导(Preamble)、Extended-Sync紧跟一个用于Data Burst的HS-Sync,或者紧跟一个用于Control Burst的Control-Sync或Control-Code。任何burst结束的时候,发送端在转换到默认的ALP Stop状态或ALP ULPS状态(如果是ULPS Entry Control Burst)之前,会发送一个长的HS-Trail序列。一个Control Burst的HS-Trail周期中,接收端会识别EoB(End-of-Burst),并且禁用掉差分端接。

ALP Exit Detector是一个差分的接收器,它带有一个偏移的输入阈值电压(offset input threshold voltage),用来检测ALP-00和任意ALP Wake状态之间的差分电平的差值。ALP ULPS状态对比ALP Stop状态来说,接收器能够有更低的功耗,这是因为其需要更长的时间来唤醒。电路的设计者可以选择优化ALP Exit Detector的实现,使用一个带有可配置偏置电压(bias)的低功耗的差分接收器架构,以便在功耗和检测时间上进行权衡。

图7 Examples of High Speed Data and ALP Control Bursts

上图展示了HS Data和ALP Control Bursts的结构。

接收器要支持两种不同的机制来检测EoB(End-of-Burst):

- HS-Trail检测,用于Control和Caliberation Bursts

- Controller辅助的EoB检测,用于HS Data Bursts

对于基于HS-Trail的检测机制,接收器要检测HS-1序列,这个序列持续时间超过了ALP Trail Exit Duration()后会被看做HS-Trail,检测的地方是当前burst结束的时候。

(注意:原文是For the HS-Trail based detection mechanism, a receiver shall detect an HS-1 sequence exceeding the ALP Trail Exit duration TALP-TRAIL-DET as an HS-Trail as the end of the current burst.个人意见,此处第二个as应该是at。这里用as的话我无法理解这个句子想要表达什么意思,当然这个纯属个人理解,请自行看规范原文进行解读。)

这个事件(HS-Trail)会触发HS端(termination)和HS-RX的禁用动作,并且启用ALP-ED来检测下一个Start-of-Burst。

这种基于HS-Trail的检测机制用于以下场景:

- 任意的ALP Control Burst,包括但不限于Triggers、ALP ULPS entry和Fast BTA

- Skew Caliberation Sequence

- Alternate Caliberation Sequence

由于在正常的HS Data Bursts的载荷数据中可能会存在HS-Trail序列,因此定义了控制器辅助EoB检测的机制,用于在HS Data Bursts结束的时候检测EoB。这需要使用了PPI信号RxDetectEobHS的接收端controller去通知PHY说检测到了一个HS Data Burst的结束。控制器(controller)本身拥有所有必要的信息来解析进入的数据包(packets)并且检测它们的边界以及EoB。

控制器辅助EoB的检测机制用于以下场景:

- 任意HS Data Burst

为了确保两种机制有确定的行为(deterministic behavior),也为了保证两种机制间的相似性,控制器要在HS-Trail期间将EoB PPI信号置有效。PPI信号RxDetectEobHS信号应该在HS-Trail周期中尽可能早地被置位,以便让接收器快速进入ALP Stop。但是,由于HS-Trail没有最大时间限制,它能够按照需要被延长来适应控制器里的额外延迟(识别和发出EoB信号到PHY的过程)。

接收器要在burst开始的时候,使用SYNC信息来识别到来的burst的类型,并由此选择合适的end-of-burst检测机制。