一、异常等级

在操作系统中,软件开发被分成不同的模块,每个模块具有不同的访问系统和处理器资源的级别。例:Linux系统中,内核需要对系统资源进行高级别访问,同时会限制应用程序配置系统的能力。AArch64体系结构通过不同的特权级别(privilege level)来实现这种分离,在arm架构上这种特权级别被称为异常级别(exception level),简称EL。

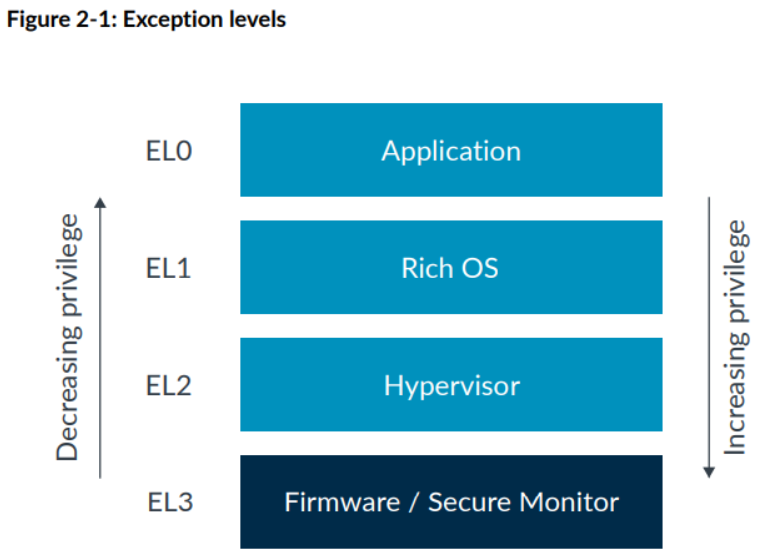

AArch64 Exception levels见下图:

EL0:无特权模式,所有app应用都在EL0。

EL1:是一个特权模式,能够执行一些特权指令,用于运行各类操作系统,在安全模式则是可信OS。

EL2:提供了对虚拟化的支持。

EL3:具有最高管理权限,负责安全监测和安全模式切换。

二、异常类型

ARM架构包括2种异常:同步异常(Synchronous exceptions)和异步异常(Asynchronous exceptions)。

1、同步异常

由正在运行的指令或指令运行的结果,出错造成的异常。同步异常包括:

1.1)Invalid instruction and trap exceptios:无效的指令和陷阱异常。

1.2)Memory access:内存访问

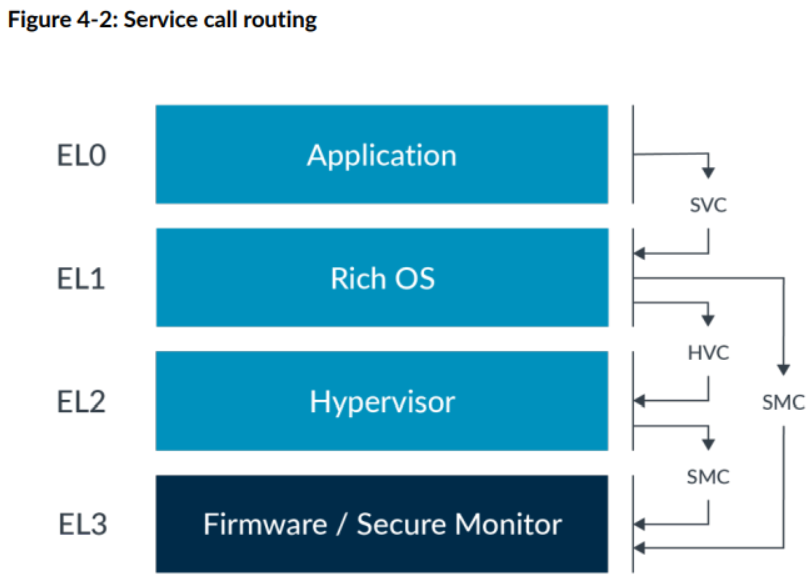

1.3)Exception-generating instructions:例:SVC、HVC和SMC。

1.4)Debug exceptions

1.4.1)Breakpoint Instruction exceptions

1.4.2)Breakpoint exceptions

1.4.3)Watchpoint exceptions

1.4.4)Vector Catch exceptions

1.4.5)Software Step exceptions

2、异步异常

不是由运行的指令造成,可在程序运行中的任意时刻发生。异步异常包括:

2.1)Physical interrupts(例:uart中断)

2.2)IRQ和FIQ

2.3) SError

2.4)Virtual interrupts

2.4.1)vSError,Virtual System Error

2.4.2)vIRQ,Virtual IRQ

2.4.3)vFIQ,Virtual FIQ

三、异常切换

EL0的所有异常(同步和异步异常)都可以将core切换到EL1中。

EL1的所有异步异常、HVC指令都可以将core切换到EL2中。

EL2的所有异步异常、SMC指令都可以将core切换到EL3中。

所有的返回指令都是ERET。

SVC(Supervisor Call):当用户空间通过系统调用陷入到内核空间的时候,则最终会通过SVC指令进入到内核空间。

HVC(Hypervisor Call):在ARMV8-A架构下,Normal World,EL1尝试去访问EL2的时候,则会陷入到虚拟化层,其中是通过HVC指令。

SMC(Secure Monitor Call):用于切换Normal World和Secure World。

四、异常处理流程

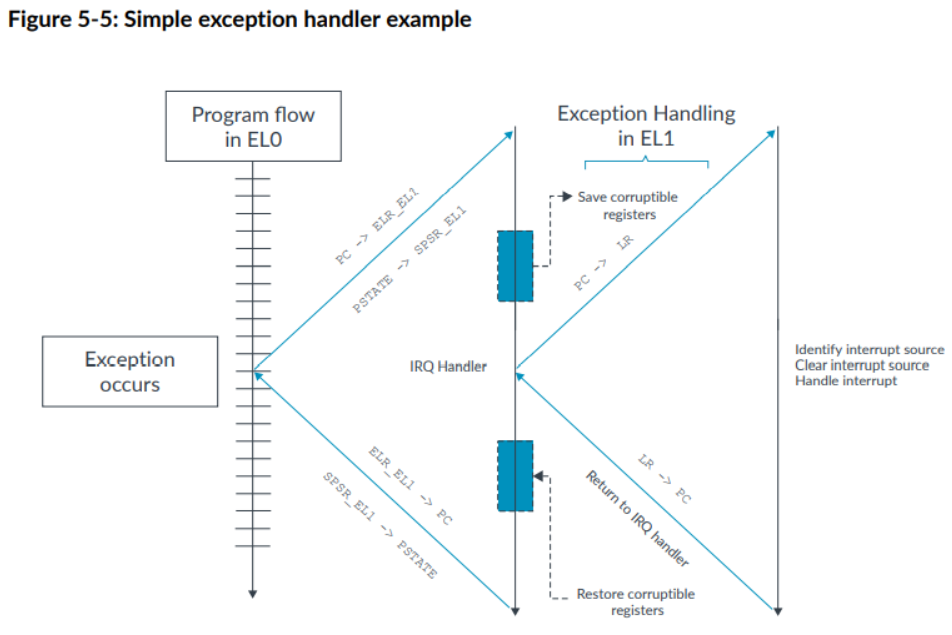

下图介绍了一个简单的异步异常处理流程。

异步异常发生时,操作流程如下:

1)将PSTATE(Process state)保存到SPSR_EL1中。

2)将PC指针保存到ELR_EL1。

3)通过读取虚拟机监控程序配置寄存器HCR_EL2.RW的RW位来确定目标执行状态。。

4)异常级别更改为EL1,跳转到异常向量表里执行。

5)在异常向量表的每个表项,保存一个异常处理函数的跳转函数,跳转到对应的异常处理函数处理异常。

当异常处理程序处理完成后,异常返回:

1)恢复所有寄存器,并执行ERET指令。

2)从ELR_EL1寄存器恢复PC指针。

3)从SPSR_EL1寄存器恢复处理器状态。

参考:

1、learn_the_architecture-aarch64_exception_model.pdf