\\\插播一条:我自己在今年年初录制了一套还比较系统的入门单片机教程,想要的同学找我(禾厶-亻言-手戈)免費的。最近比较闲,带做毕设,带学生参加省级以上比赛///

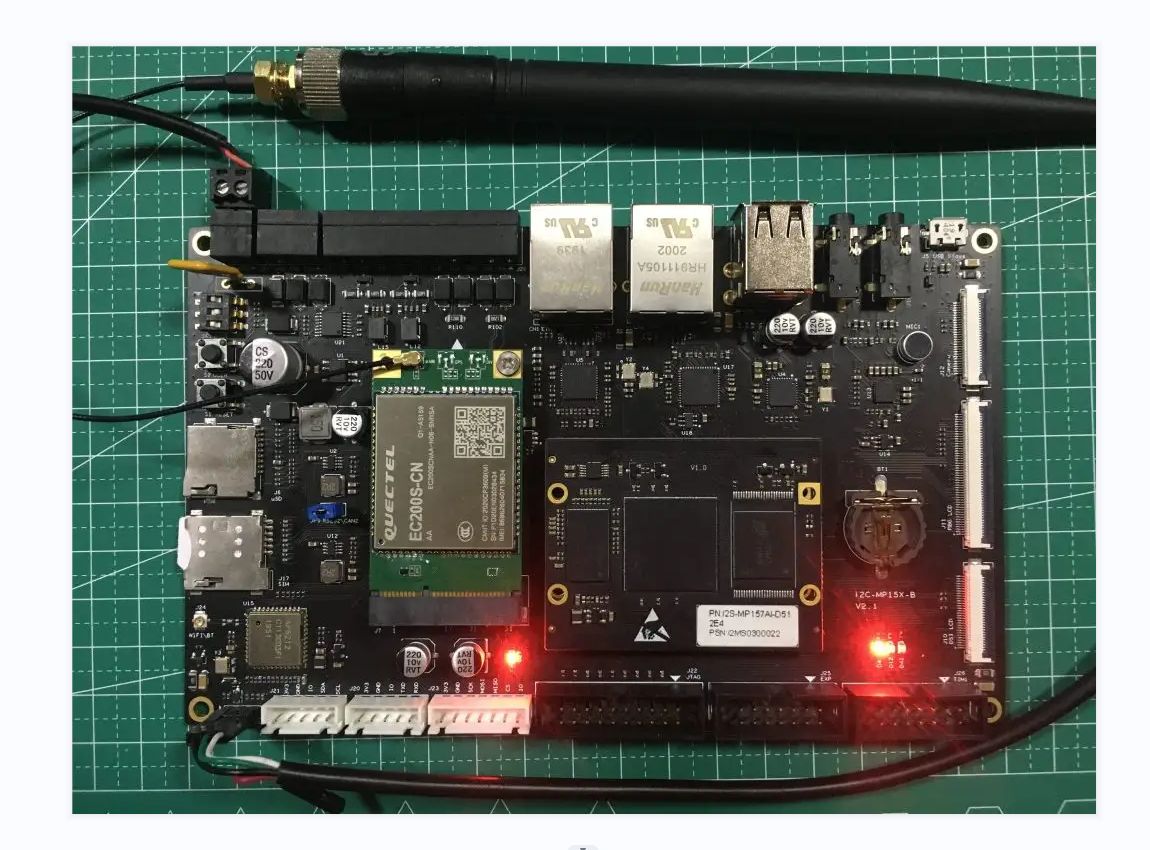

想必玩过单片机或者 FPGA开发板的同鞋对 jtag接口并不陌生。在需要烧录程序的时候,对着板子的接口接“跟”线,完事儿。不过今天想和各位聊聊的问题是,jtag究竟是如何实现的。事先声明,我只是个缝合怪!接下来的内容来自网络+博客+IEEE官方文档+其它。最后我会列出相关参考。

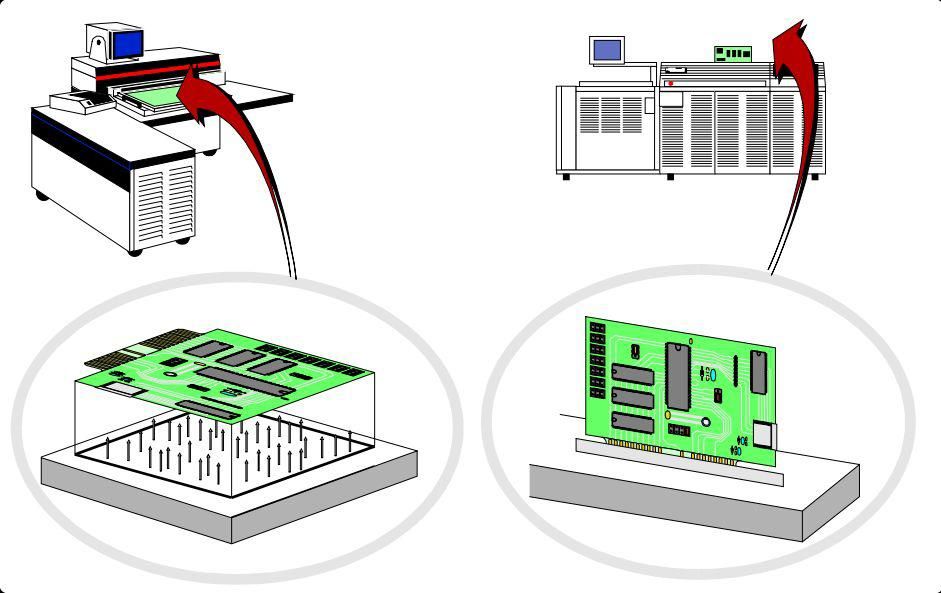

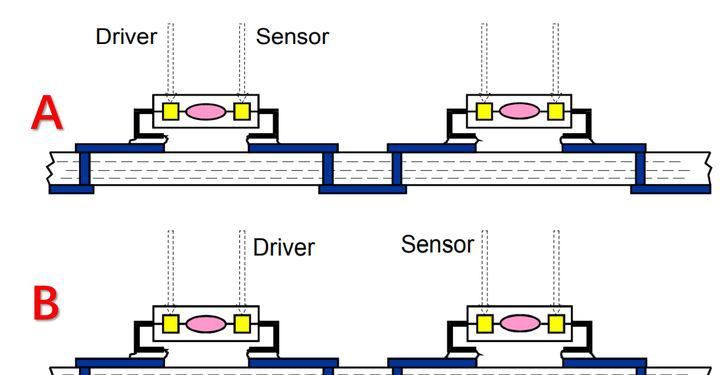

言归正传,Jtag作为一个国际化的标准,目前我们可以用它来做程序烧录,debug,电路检测等操作。在数字电路设计中,大多作为电路故障诊断的一种手段。图1展示了对电路功能的两种检测方案。现假设我们利用 verilog实现了一个性能非常 nice的加法器,吊打各大公司的 IP,然后功能仿真也没有任何问题。但是我们并不确定加工生产(原谅我着拙劣的用词)出来的电路到底是个什么情况?哎,这个时候 jtag就可以发挥作用了。在图1(A)中那个粉红色的单元就是我们写的超级 nice的加法器,左右两侧的黄色单元是其与外部的引脚连线。我通过 jtag在左侧灌入激励(Driver),然后从右侧查看与之对应的响应(Sensor),从而判断这个加法器的实际电路有没有缺陷。图1(B)呢大家可以思考一下,我们后面以这个为例做具体的讲解。

图1简单的功能示意图[1]

图1简单的功能示意图[1]

当然,在具体的实现过程中,也不是我们想检测就可以检测的,不然也不会劳烦IEEE专门搞了一个叫 Joint Test Action Group。你猜的没错,这就是 Jtag的简称了。下面我们将从整体结构依次介绍JTAG。

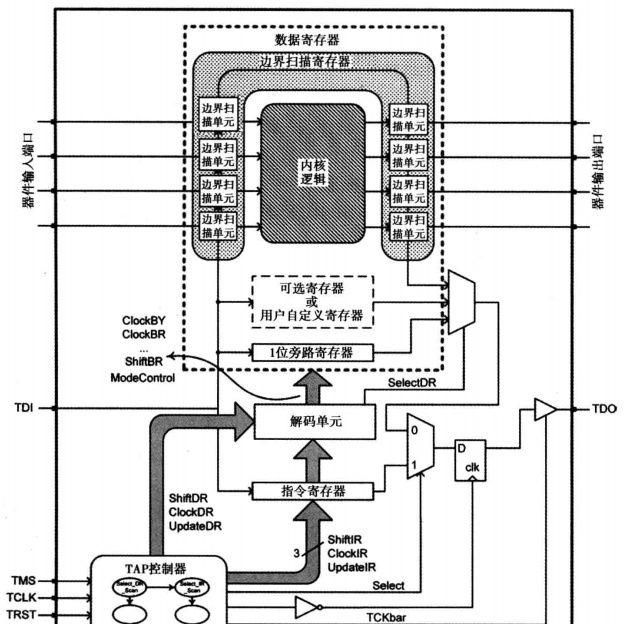

图2展示了一个较完完整的 JTAG整体架构设计。它主要包含了一下几点内容。

.一组关键的控制信号 TMS, TDI, TDO, TCLK。有些结构还包括 TRST(图2中含有这个信号)

.指令寄存器

.数据寄存器,其中包括边界扫描寄存器,旁路寄存器,设备识别寄存器以及其它用户自定义的寄存器

.解码器

.TAP(Test Acess Port)控制器(核心控制组件)

下面就以上五点内容做具体的介绍。

图2 JTAG整体构造设计[2]

图2 JTAG整体构造设计[2]

Part1:一组关键的控制信号TMS,TDI,TDO,TCLK,以及一个可选的复位信号TRST

?TMS:外部输写驱动 JTAG的一个单 bit信号。核心功能是完成对 TAP控制器的状态控制

?TCLK:顾名思义,就是外部给 JTAG的一个时钟信号

?TDI:测试数据输写,用来将串行测试数据和指令移入芯片

?TDO:测试数据输出,联合 TDI的定义,就是将得到的反应给过移出芯片

那啥叫移入芯片和移出芯片?我们前面举了一个加法器的例子。我们就是这么简略粗犷,完成了对一个加法器电路的流片。我们须要完成对加法器电路的检测。那此时这个加法器就是图2所示的内核逻辑。因此,TDI的作用就是通过 TDI端口将激励灌入这个内核逻辑,TDO就是将反应结果从内核逻辑中取出来,方便我们人为的观察和评判数据的正确性。那 TDI和 TDO到底是怎么做到的呢?别急,这局部内容有点杂,劳请读者耐住性子往后看(我写的东西可能的确比较拉跨,多担待)。

Part2:指令寄存器

指令寄存器,就是寄存指令的寄存器。IEEE规范规定该寄存器至少是 2bit。从而实现对4种强制性指令的编码。不设上限,从而指令的条数也就没有上限。当个比方说,我们之前提到 JTAG能够实现烧录程序,debug等等。那 JTAG详细做什么功能用,肯定是我们人为给出了相应的指令控制,然后 JTAG才会执行与指令相匹配的操作。OK,回到指令寄存器上来,图3给出了一个具有指教性的指令寄存器的设计构造(当然你也能够用 verilog写出更妙的电路来)。

联合图4,对于指令寄存器而言,它须要实现两个功能,换句话说,须要拥有两种工作模式:shift(移位)和 holding(保持)。接下来所说的内容须要联合一点 TAP控制器(行文到这里还没有介绍 TAP控制器,但是我认为我这样安排已经算是合理的了)。但是不妨碍对图3指令寄存器的了解。

联合图4,首先介绍shift操作。当处于shift模式时,指令寄存器接管

绿色图标【‟で】liutianwang123

来自 TDI上的数据,并将原本存储的数据从 TDO输出(你可以粗暴的就把他看作一个移位寄存器,当时实际的情况时一组,不单单是一个触发器)。回到图3,要实现移位功能,ShiftIR选中 Sin端的数据作为寄存器A的输入,然后 TDO接收寄存器A的Q端输出作为 TDO的输出。在执行 holding操作时,通过控制 UpdataIR,我们接收来自寄存器B的Q端的数据。

细心的朋友或许会发现,不还有一个输入端口 Din嘛,这个是干哈的呢?打个比方(可能不是很恰当),就是我要通过指令给出一个操作,但是这个指令并不是从 TDI上获取的,而至从固化的逻辑获取的。哎,这个 Din就是和固化逻辑的连线接口。相当于利用 ShiftIR选用 Din的数据存入指令寄存器。

写到这里,可能R选择 A端的低电平 0送入寄存器(明眼人都能看出来)。那为什么要有这两种模式呢?别急,我们后面会有介绍。这里只是先展示一下这个寄存器的结构长什么样子。

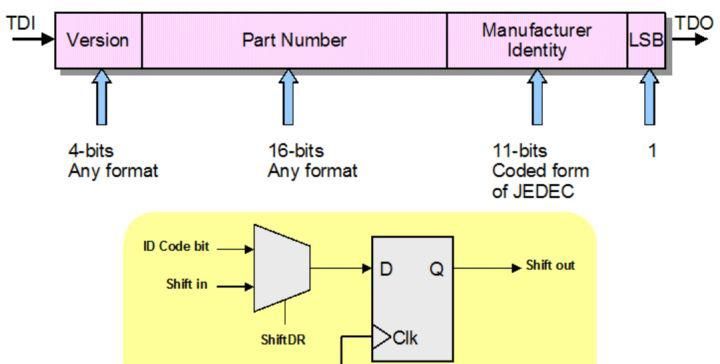

2、设备识别寄存器 Identification Register

图6:设备识别寄存器结构示意图[1]

图6:设备识别寄存器结构示意图[1]

这是IEEE 1149.1中的一个可选寄存器,也就是你在实现一个 JTAG的时候,可以生成这样的寄存器也可以不生成。如果配置这个寄存器,则这个寄存器得是 32bit的,存放设备识别码。该设备识别码可以通过 TDI-TDO这样一条串行链路传输到外部。

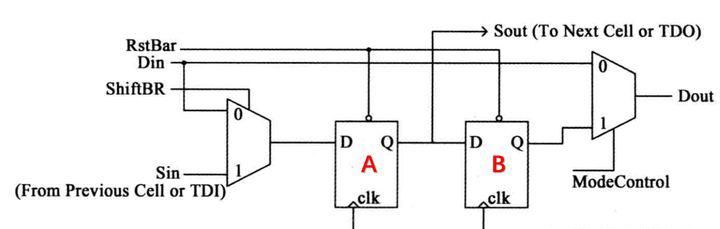

3、边界扫描寄存器

图7:单个边界扫描寄存器结构示意图[2]

图7:单个边界扫描寄存器结构示意图[2]

边界扫描寄存器在 JTAG操作中应该算是最常用的寄存器。它主要有以下几种工作模式

·通常模式:配置 ModeControl信号,直接将Din端信号通过Dout输出

·移位模式:配置 ShiftDR和 ClockBR,将TDI上的信号串行打入寄存器A,并完成串行移位的操作(寄存器组)。

·捕获模式:配置 ShiftDR和 ClockBR,将 Din上对的信号并行打入寄存器A

·更新模式:配置 UpdateBR和 ModeControl信号,对完成移位操作后的信号进行“锁存”,并输出到 Dout上。

那么具体这个寄存器工作在何种模式,是依据当前执行的指令是什么以及 TAP控制器目前是处于什么样的状态决定的。

Part4:TAP控制器

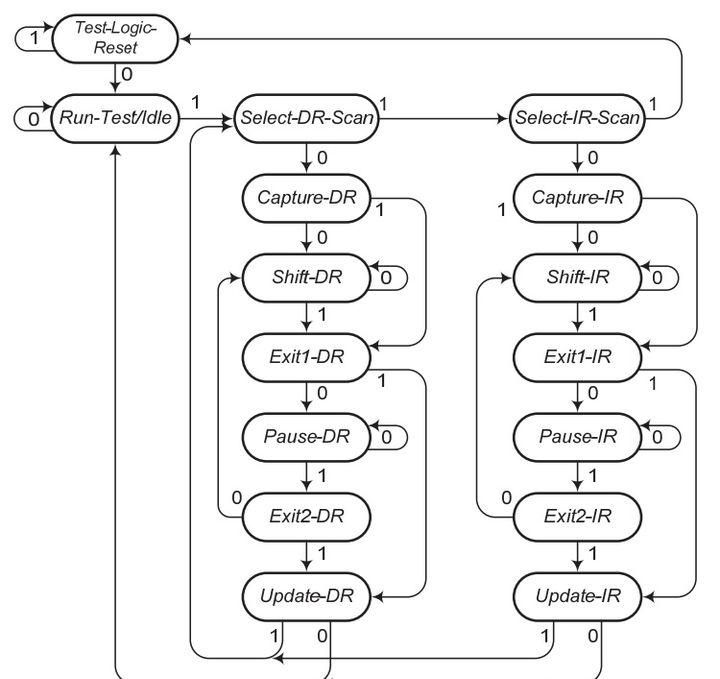

图8:IEEE标准下的TAP控制器结构示意图[3]

图8:IEEE标准下的TAP控制器结构示意图[3]

对,TAP其实是一个拥有16个状态的状态机。该状态机由 TCLK和 TMS信号驱动( TMS信号闪亮登场),完成状态的跳转。从整体结构上看,整个状态机分为两大块,图8右侧的指令Scan和左侧的 Data Scan。Test-Logic-Reset为初始状态和复位状态。在此状态机的任意一个状态,保持 TMS信号至少 5个周期的高电平,状态机会进入复位状态(不信你可以自己试试)。

1、Test-Logic-Reset

状态机的初始状态。在此状态下,IEEE标准指导的是默认加载一个叫做 IDCODE的指令。小插曲:哎,这个指令刚好对应这个前面所说的设备识别寄存器。如果当前的 Jtag没有配置设备识别寄存器,默认加载的是 Bypass指令。

2、Select-DR-Scan和 Select-IR-Scan以及 Run-test/Idle

临时状态,不做具体的操作,详细的各位可以去查IEEE 1149.1标准(文后我会给出链接)。

3、Capture-IR

还能回想起来之前在描述指令寄存器的时候,说过它的工作模式的问题吗?当 TAP控制器处于 Capture-IR状态时,指令寄存器执行捕获的操作,也就是将 Din上的数据并行加载到指令寄存器中来。

4、Capture-DR

虽然数据寄存器有很多,但是就前面所聊到的那些寄存器是不是也都有 Din端口。当 TAP控制器处于这个状态时,对应的数据寄存器则将 Din上对的数据并行加载到寄存器中来。啥叫“对应的寄存器”?这个我们在 Part 5中进行解释。

5、Shift-IR和 Shift-DR

指令寄存器或数据寄存器执行移位的操作

6、Exit1-IR、Exit2-IR、Pause-IR

在执行 JTAG操作时,有的时候测试向量缓存很小,缓存空了但是激励还没给完,需要等待一下,那么这三个状态就发挥作用了。就是一个等待的过程然后进行状态挑战

7、Exit1-DR、Exit2-DR、Pause-DR

同上。只不过这个是防止接收缓存小而导致接收缓存满了的问题(个人理解)。

8、Update-IR和Updata-DR

Updata-IR:指令寄存器完成移位后,对数据进行“锁存更新”,便于输出。(可以看看图3)

Update-DR:数据寄存器完成移位后,对数据进行“锁存更新”,便于输出。(可以看看图7)

接下来我们较为完整的阐述一下整个状态机的处理流程。系统上电后,TAP控制器进入Test-logic-Reset状态。然后依次进入Run-Test/Idle→ SelectDR-Scan→ Select-IR-Scan→ Capture-IR→ Shift-IR→ Exit1-IR→ Updata-IR,最后回到Run-Test/Idle。在Capture-IR下,一个特定的逻辑序列被加载到指令寄存器中;然后 TAP进入Shift-IR状态。在该状态下,受 TCLK时钟控制,一条特定的指令送入移位寄存器并进行移位的操作。在Updata-IR状态下,移位寄存器中的数据(指令)送入更新指令寄存器中。最后回到Run-Test/Idle ,完成指令的加载。

一般而言,指令加载完成后,进行数据Scan的操作。以为起点,依次进入SelectDR-Scan→ Capture-DR→ Shift-DR→ Exit1-DR→ Updata-DR。最后回到Run-Test/Idle。在此过程中,数据寄存器会被配置到 TDI-TDO之间(可以理解为点到点之间的串行连接)。在Capture-DR状态下,TCLK的驱动,芯片管脚上的输出信号会被“捕获”到相应的边界扫描寄存器单元中去。这样,当前的数据寄存器当中就记录了芯片相应管脚上的输出信号。接下来从Capture-DR进入到Shift-DR状态中去。在Shift-DR状态中,由 TCK驱动,在每一个时钟周期内,一位新的数据可以通过 TDI串行输入到数据寄存器当中去,同时,数据寄存器可以通过TDO串行输出一位先前捕获的数据。在经过与数据寄存器长度相同的时钟周期后,就可以完成新信号的输入和捕获数据的输出。接下来通过Exit1-DR状态进入到Update-DR状态。在Update-DR状态中,数据寄存器中的新数据被加载到与数据寄存器的每个寄存器单元相连的芯片管脚上去。最后,回到Run-Test/Idle状态,完成对数据寄存器的访问。

上面的描述,有什么移位寄存器,更新数据寄存器,以及XXXX,可能初看会一头雾水。但是大家思考一下我们之前所说的指令寄存器和数据寄存器它们的工作模式,或许你有新的发现。在Part6中,我们以一个具体的例子进行阐述这个过程。

Part5:指令寄存器和数据寄存器

回到图2,图2中是不是还有一个解码单元。这个解码单元是指令寄存器和数据寄存器的桥梁。当TAP完成指令加载后,也就是现在Jtag知道自己要做什么事了。指令寄存器中存放的指令经过解码单元进行译码,从而选中与指令对应的数据寄存器。比如 Bypass指令则选中旁路寄存器;IDCODE指令选中设备识别寄存器。

Part6:指令和数据的加载过程示例

(1)指令的加载

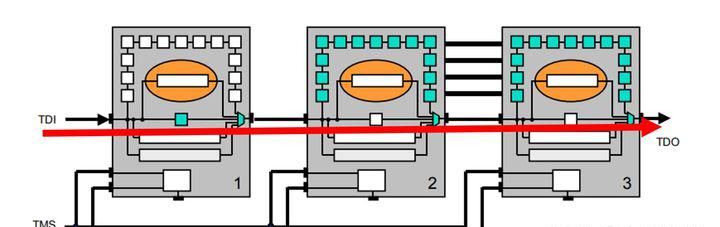

我们现在假设每个Chip上的指令寄存器都是2bit。旁路指令编码为11,采样指令编码为00(我们暂时可以不管这个指令到底是干嘛的)。现在需要将指令送入这三个chip,并让chip1指令旁路操作,而chip2和chip3执行采样操作。当TAP控制器在Shift-IR 状态下时,将指令寄存器配置到TDI-TDO之间(如图9所示的串行连接结构,红色箭头所示)。从左侧TDI上串行灌入指令序列110000,经过6个cycle的移位后,当前chip1的指令寄存器(或者移位寄存器)中为11,chip2和chip3为00。这个时候我们认为移位完成,控制 TMS让状态机进入Updata-IR。这个时候每个chip的指令移位寄存器中的数据送入指令更新寄存器完成指令加载的操作(时刻牢记指令寄存器和数据寄存器的工作模式)。

图9:指令的加载配置示意图[1]

图9:指令的加载配置示意图[1]

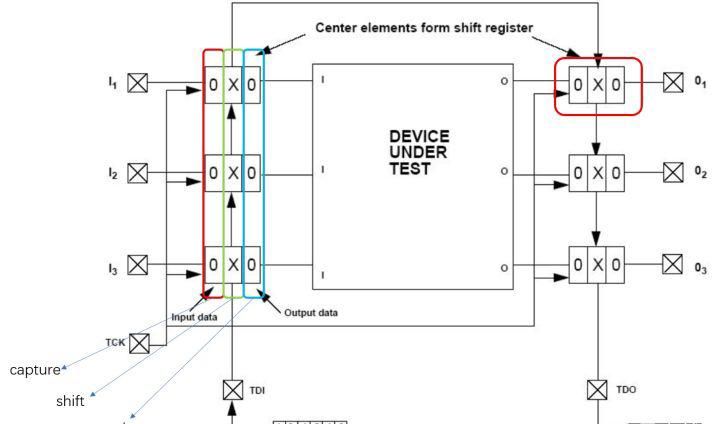

(2)数据加载

终于找到更为直观的图了,解放了!请看图10。图示更为形象的将数据寄存器的工作模式体现了出来。红色的可以理解为给Cupture-DR服务的寄存器,绿色的时给Shift-DR服务的寄存器,蓝色的是给Updata-DR服务的寄存器。

图10:数据寄存器的操作过程[4]

图10:数据寄存器的操作过程[4]

图10中给出的示意图是准备进行数据Scan的操作,此时假设整个扫描链中的寄存器都是未知态X。移位寄存器和TDI-TDO串行连接。现在需要将101010这个序列送入整个边界扫面单元。

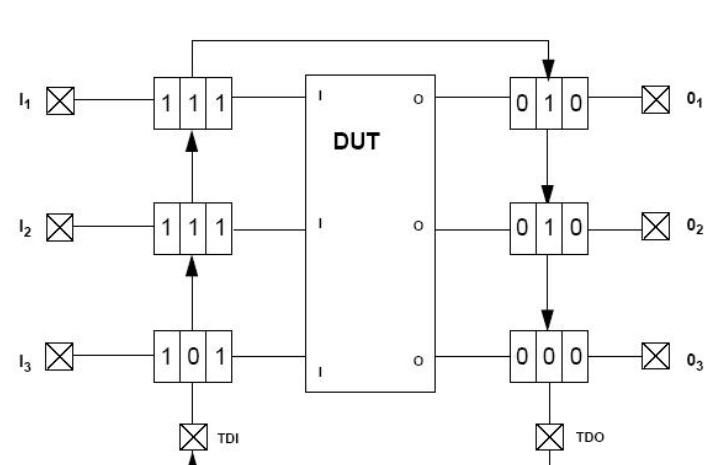

TAP状态机首先进入Capture_DR,在一个 TCLK时钟的驱动下,芯片管脚上的信号状态全部被捕获到相应的边界扫描移位寄存器单元当中去(如图11)。接着进入Shift-DR,这个时候进行串行移位的操作。图2给出了经过两个时钟移位后的示意图(每个时钟一个bit)。经过6个时钟移位后,TAP控制器进入Updata-DR状态,完成状态的更新。而原先在由Capture-DR捕获到的并送入Shift-DR,则通过 TDO输出到了外部。

图11:Capture_DR[4]

图11:Capture_DR[4] 图12:Shift after 2 cycles[4]

图12:Shift after 2 cycles[4] 图13:Updata-DR[4]

图13:Updata-DR[4]

今天先写到这里吧,写不动了。以及关于 Jtag的常见的一些问题一起进行探讨。

对于所写的内容有问题或者表述有错误的地方,还望各路大佬不吝赐教。在此鞠躬表示感谢!