汇总篇:

Xilinx FPGA平台以太网接口(汇总篇)_子墨祭的博客-CSDN博客_fpga实现以太网接口

目录

一、IP核配置

在有了本系列(一)(二)的基础之后,我们开始进入实操。插句题外话,FPGA只是工具,会用就行了,更多的知识在FPGA之外;什么叫会用,直接用IP来搬砖轻轻松松。

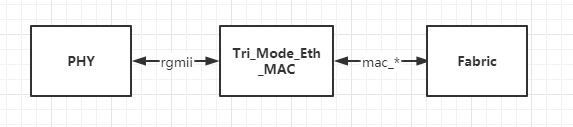

Xilinx为我们提供了一个叫做“Tri-Mode Ethernet MAC”的IP核,三种模式的以太网介质访问控制层器,支持全双工半双工的千兆、百兆、十兆和2.5G的传输速率,支持MII、GMII、RGMII、SGMII和TBI接口。文档为《PG051》。

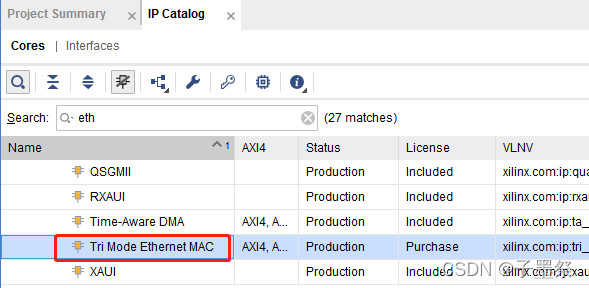

首先输入 ETH 找到三速以太网IP:

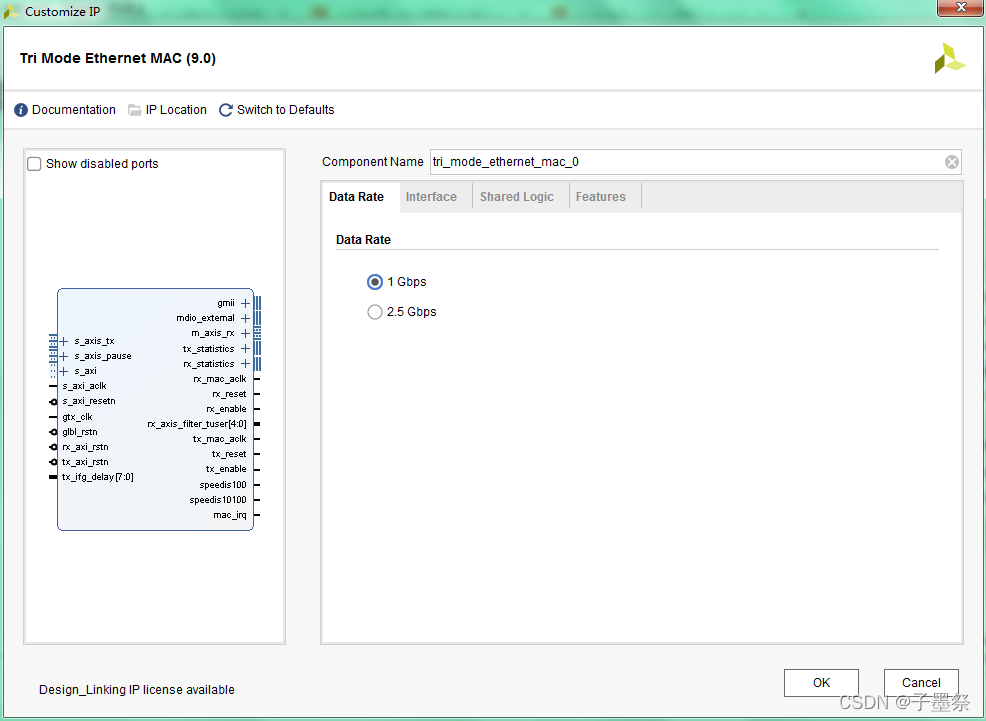

第一页:传输速率

设置最大的通讯速率,1Gb/s支持高达1Gb/s的以太网速度。支持四种类型的物理接口,即GMII,MII,RGMII和内部接口均可用。2.5 Gb / s 只适用于物理接口为“内部”,所有其他类型均被禁用。

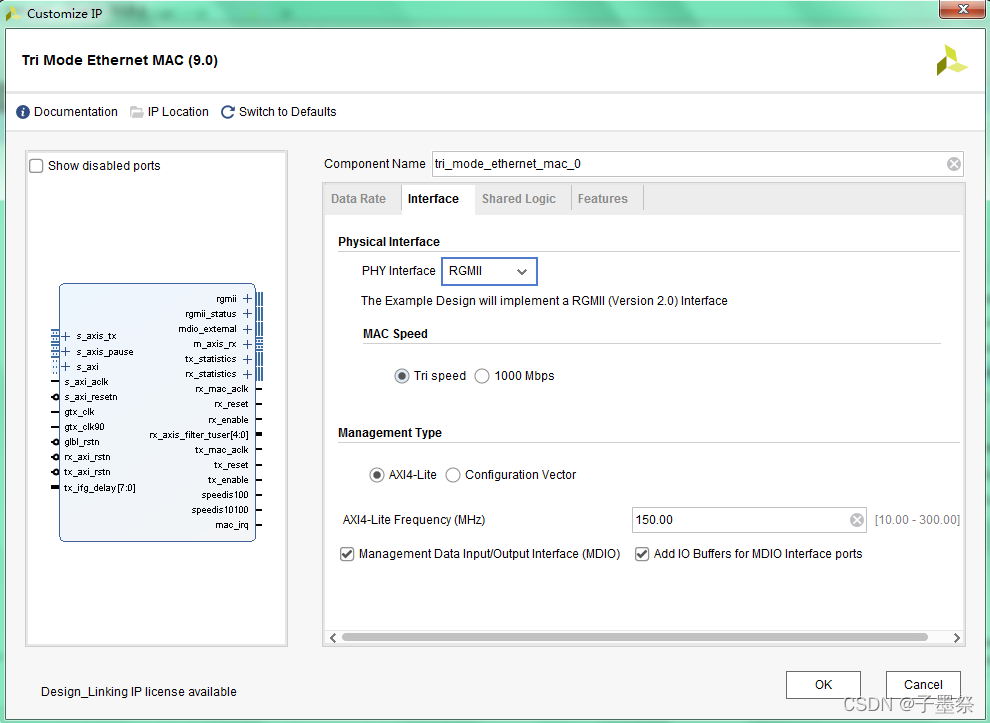

第二页:接口配置

物理接口:

Internal/MII/GMII/RGMII可选,配置与MAC接口的类型,接口类型,可以回顾系列(二)中的MAC层接口说明:

Xilinx - FPGA平台以太网接口(二)系统架构及MAC层接口介绍

- MII支持10 Mb/s和100 Mb / s;

- GMII支持10 Mb/s,100 Mb / s和1Gb/s;

- RGMII是双沿采样,支持10Mb/s,100Mb/s和1Gb/s。

- Internal是生成内核时,没有物理接口可用于连接到内部PHY,例如以太网1G / 2.5G PCS / PMA或SGMII LogiCORE。

我们这里选择RGMII,使用时根据具体情况而定。

PS : RGMII也可以使用原语完成设计(IDDR、ODDR、IDELAYE2、ODELAYE2、IDELAYCTRL)

MAC Speed:

三速以太网IP可支持2.5Gb/s和1Gb/s速度运行,10Mb/s和100Mb/s速度运行以及全三速运行(10Mb/s,100Mb/s和1000Mb/s)。可用于速度支持选择的选择取决于所选的物理接口:

- 当MAC数据速率设置为2.5 Gb / s时,仅内部模式可用。

- 如果MAC数据速率设置为1 Gb / s,并且选择了GMII,RGMII或Internal,则可以选择三速操作和1 Gb / s操作。

- 若MAC数据速率设置为1Gb/s并且选择了MII,则仅10Mb/s和100Mb/s的操作可用。

我们这里选择三速模式,可以通过接口改动传输速率。

管理类型:

选择“ AXI4-Lite”选项以包括用于IP配置的可选管理接口。如果未选择AXI4-Lite管理界面,则AVB选项不可用。默认设置是选择AXI4-Lite管理接口。

启用管理接口后,选择“管理数据输入/输出接口(MDIO)”选项以包括可选的MDIO接口。如果未选择此选项,则生成的内核不具有管理物理层中的对象所需的MDIO逻辑。

如果启用了MDIO,请选择“为MDIO接口端口添加IO缓冲区”选项以为MDIO接口端口插入I / O缓冲区。这将创建双向I / O总线mdio,并为mdc插入输出缓冲区。如果未选择此选项,则将使用mdio_i,mdio_o和mdio_t端口生成内核。

AXI4-Lite频率:

指定AXI4-Lite接口的频率。

第三页:共享逻辑

选择放入example design。

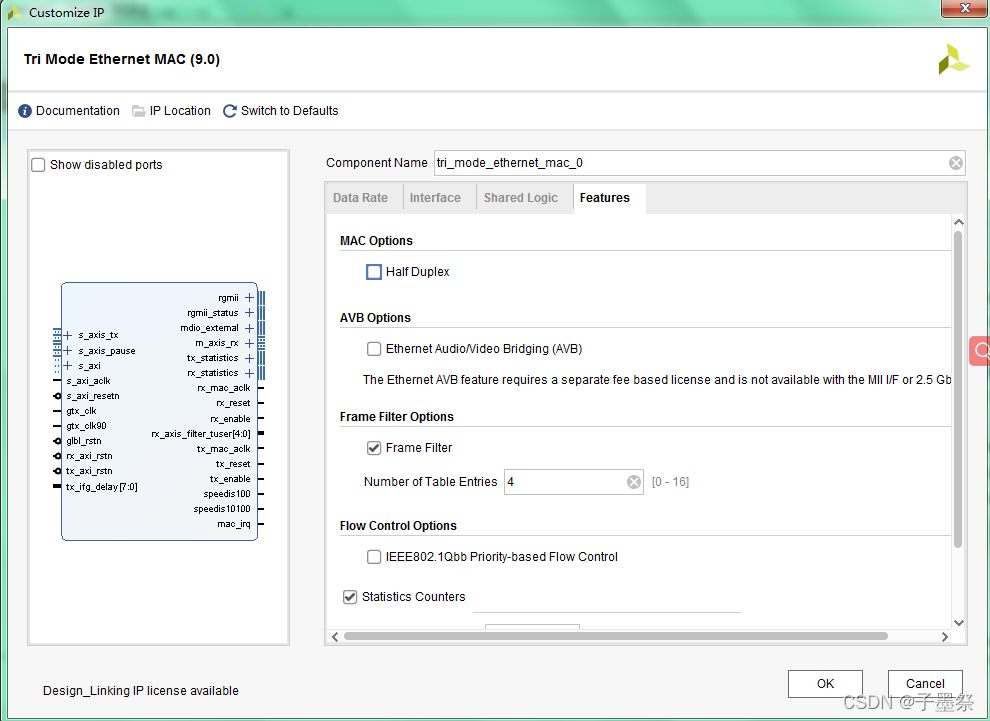

第四页:特性

MAC选项:

选择是否启用半双工逻辑。默认是全双工模式。

AVB选件:

Audio Video Bridging,AVB用于增强以太网的实时音视频性能,同时保持了向后兼容传统以太网。如果选择此选项,则除了三模式以太网MAC license外,还需要收费的以太网AVB端点许可证来启用内核生成。

帧过滤器选项:

可以使用帧过滤器生成内核,从而阻止接收与此MAC不匹配的帧。。

流控:

启用基于优先级的流控支持。一般不用。若勾选,则包括在发送时生成PFC帧并在接收时解释PFC帧的电路。

统计宽度:

使用内置的统计计数器生成内核。统计信息计数器可以是32位或64位宽。

统计复位:

当包括统计计数器时,可以包括逻辑以确保在硬件复位时将计数器清除为零。默认选择。

二、接口介绍

重点关注标色的几部分:

浅绿色:表示接收部分

这是什么色:表示发送部分

蓝色:表示与PHY之间的接口

黄色:表示配置接口

颜色,同时也表示同一时钟域。

PS:而在下一篇example design中,你讲会发现,example design在外围又封装了一层FIFO接口,tx/rx_axis_fifo_*

| gtx_clk |

IN |

1 |

核的全局时钟,1Gbps是125M,2.5Gbps是312.5M |

| gtx_clk_out |

OUT |

1 |

该时钟相对于gtx_clk输入具有0°相移,并用于RGMII数据传输。 |

| gtx_clk90_out |

OUT |

1 |

该时钟相对于gtx_clk输入具有90°相移,用于RGMII发送器时钟转发。 |

| refclk |

IN |

1 |

仅适用于GMII或RGMI,空闲控制需要,200M到300M, 对于UltraScale需要到300至1333M |

| rx_mac_aclk |

Out |

1 |

用于在物理接口上接收数据的时钟,该时钟应用于为物理接口接收电路和RX AXI4-Stream接收电路提供时钟。 312.5MHz对应2.5 Gb/s 125MHz对应1 Gb/s 25MHz对应100 Mb/s 2.5MHz对应10Mb/s |

| rx_reset |

Out |

1 |

高电平有效 RX部分的软复位 |

| rx_axis_mac_tdata |

Out |

8 |

核收到的用户数据 |

| rx_axis_mac_tvalid |

Out |

1 |

rx_axis_mac_tdata的数据有效信号 |

| rx_axis_mac_tlast |

Out |

1 |

rx_axis_mac_tdata端口的控制信号。 表示帧中的最后一个字节。 |

| rx_axis_mac_tuser |

Out |

1 |

rx_axis_mac_tdata的控制信号。 在帧接收结束时置位,表示帧有错误。 |

| rx_axis_filter_tuser |

Out |

X+1 |

每帧滤波器调谐器输出。可用于仅发送特定帧过滤器传递的数据。有关详细信息,请参阅帧过滤器 |

| tx_enable |

Out |

1 |

对于RGMII, 若为1Gbps,则一直高电平; 若为100Mbps,则十个周期中1个周期为高电平 若为10Mbps,则一百个周期中1个周期为高电平 |

| tx_ifg_delay |

IN |

8 |

用于可配置帧间间隙的控制信号 |

| tx_statistics_vector |

Out |

32 |

状态收集统计 |

| tx_statistics_valid |

Out |

1 |

tx_statistics_vector数据的有效信号 |

| tx_mac_aclk |

Out |

1 |

用于在物理接口上传输数据的时钟,该时钟应用于为物理接口发送电路和TX AXI4-Stream发送电路提供时钟。 312.5MHz对应2.5 Gb/s 125MHz对应1 Gb/s 25MHz对应100 Mb/s 2.5MHz对应10Mb/s |

| tx_reset |

Out |

1 |

高有效,发送端模块的复位信号 |

| tx_axis_mac_tdata |

IN |

8 |

要传输的帧数据 |

| tx_axis_mac_tvalid |

IN |

1 |

tx_axis_mac_tdata的数据有效信号,高电平有效 |

| tx_axis_mac_tlast |

IN |

1 |

tx_axis_mac_tdata的最后一个有效数据高电平 |

| tx_axis_mac_tuser |

IN |

1 |

tx_axis_mac_tdata端口的控制信号。表示允许MAC向PHY发送错误的帧中的错误情况,例如FIFO欠载。 |

| tx_axis_mac_tready |

OUT |

1 |

握手信号。当tx_axis_mac_tdata上的当前数据已被接受且tx_axis_mac_tvalid为High时,置位。在10/100 Mb / s时,这用于以正确的速率将数据计量到核心。 |

| pause_req |

IN |

1 |

暂停请求:根据请求,MAC在当前数据包完成时发送暂停帧 |

| pause_val |

IN |

16 |

暂停值:插入到传输的暂停帧的参数字段中。 |

| speedis100 |

OUT |

1 |

当内核以100Mb/s运行时,此输出有效。它来自MAC速度配置寄存器的位[13:12]。如果不存在可选的管理接口,则这是从配置向量位[13:12]派生的。 |

| speedis10100 |

OUT |

1 |

当内核以10 Mb / s或100 Mb / s运行时,此输出有效。它来自MAC速度配置寄存器的位[13:12]。如果管理接口不存在,则从配置向量位[13:12]导出 |

| rgmii_txd |

OUT |

4 |

传输数据到PHY,与PHY接口数据 |

| rgmii_tx_ctl |

OUT |

1 |

到PHY的控制信号 |

| rgmii_txc |

OUT |

1 |

到PHY的时钟信号 |

| rgmii_rxd |

IN |

4 |

接收PHY的数据 |

| rgmii_rx_ctl |

IN |

1 |

来自PHY的控制信号 |

| rgmii_rxc |

IN |

1 |

来自PHY的时钟 |

| inband_link_status |

OUT |

1 |

来自PHY的链路状态 |

| inband_clock_speed |

OUT |

2 |

来自PHY的链路速度,这个是PHY硬件配置的 |

| mdio |

INOUT |

1 |

用于与PHY配置和状态通信的数据信号。若未使用则绑定高。输出数据信号,用于与PHY配置和状态进行通信 |

| mdc |

OUT |

1 |

MDIO管理时钟:使用可选的管理接口时,根据提供的配置数据从s_axi_aclk派生。 |

三、补充说明

对上面接口的进一步说明。

下一篇,我们将继续Example Design的介绍,重点查看仿真内容。