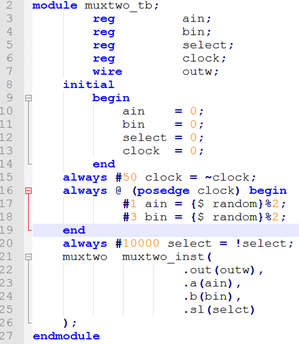

首先应该明白testBench是什么?它是用来描述变化的测试信号。testbench是做什么的?它是对电路模块(无论是行为的或者说结构的)进行动态的全面测试。通过观察被测试的模块的输出信号是否符合要求。

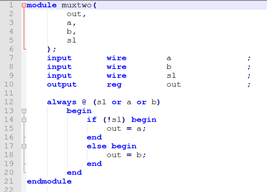

其实对于初学者而言,当然你觉得自己很牛,都应该把逻辑当成一个黑盒子。设计人员需要给黑盒子中输入一些信号,观察输出的结果是否达到我们预期的目标。就简单而言。以二选一选择器为例:

从仿真逻辑可以看出:#1 ain;#3 bin

这句话的理解很重要。当ain 延迟1ns后,bin开始延迟,bin的延迟要比ain晚上3ns。

始终记住一点,就是bin 信号的产生要比ain 信号的产生晚上3ns

仿真主要看的是波形的变化。Testbench就是激励文件,让真个逻辑在黑盒子里面工作起来。通过设置的一些参数,可以得到变化的结果。从而验证逻辑的正确与否。其实,这个东西主要在于领悟,以及自己的不断尝试。只有真正明白了才会觉得很有意思。