转载:https://zhuanlan.zhihu.com/p/296540021

尊重别人的知识产权就是尊重自己的人格!就如同这篇文章的作者所说:“对生活的热爱,来源自内心深处的善良”

SystemVerilog中多维数组

看了system verilog这本书,但是理解不深刻,所以在这里和大家一起讨论一下!做一个便于理解和记忆的总结。

1、多维数组的声明

以二维数组为例,类比矩阵,高维度称之为行(也就是X轴),低维度称之为列(可以理解为Y轴)。

//8行4列

int a[0:7][0:3];

int b[8][4];

int [7:0][3:0] c;

int [8][4] d;

刚开始学的时候会有疑问,什么时候声明用[7:0],何时要用[0:7]?

若矩阵名为a,则写在其右边的用[0:7],左侧则为[7:0]。

2、维度与$size()

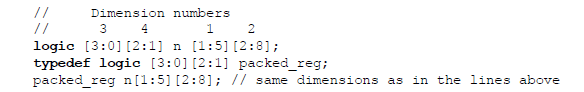

先附上SV的IEEE标准文档中的一段代码:

可见,对于unpacked类型数组n,声明时写在数组名“n”右侧的维度等级高于左侧的维度等级。在同一侧中,位于更左侧"[ ]"中的等级要高。

因此,

int a[0:7][0:3];//高等级为[0:7],低等级为[0:3]

int [3:0] unpacked_a [0:7];//高等级为[0:7],低等级为[3:0]

而$size()函数可以选择需要计算的维度,例如

$size(a,1);//数组高维度是几?答案8

$size(a,2);//数组低维度是几?答案4

$size(a);//答案8,默认为高维

总结

欢迎大家的评论和支持!我会继续努力!在PTYHON的奇幻世界,在人性的弱点,与大家不见不散!