一、同步时序逻辑分析

1、概述

(1)、时序逻辑电路特点

电路任一时刻的输出状态不仅取决于当时的输入信号,而且还取决于电路原来的状态,即与以前的输入有关

(2)、时序逻辑电路结构

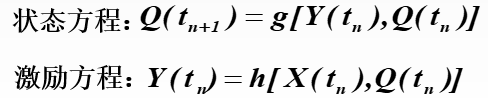

①、米里型时序电路:输出与输入及状态有关

②、摩尔型时序电路:输出只与状态有关

2、电路类型判断

判断是米里型还是摩尔型

(1)、米里型状态转移表和状态转移图

(2)、摩尔型状态转移表和状态转移图

3、同步时序逻辑电路分析步骤

①、确定输入、输出信号

②、列出激励方程、输出方程、状态方程

③、写出状态转换表

④、画出状态转换图

⑤、分析逻辑功能

二、同步时序逻辑设计

设计步骤

①、作原始状态表/图

②、状态表化简

③、状态分配(状态编码)

④、作激励函数和输出函数(确定触发器类型)

⑤、画逻辑图

1、建立原始状态表

原则:状态可多但不能遗漏

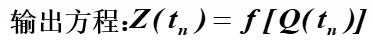

例:三位二进制可逆计数器

2、状态表化简

(1)、目的:减少触发器个数

(2)、合并条件:

①

②

③

(3)、状态等价条件

①、状态的输出Z完全相等,次态也相等

②、状态的输出Z完全相等,次态对与现态对交错

③、状态的输出Z完全相等,次态循环

3、状态分配

(1)、方法

①、一对一法

每个状态对应一个触发器

②、计数器法

给状态进行编码,状态分配

4、画逻辑图

(1)、MDS图

(2)、条件综合

5、作激励函数和输出函数

(1)、一对一法:

采用D触发器:

(2)、计数器法

①

采用D触发器

②

次态卡诺图及输出卡诺图

采用D触发器