目录

一.工程创建及属性设置

1.启动QuartusII软件

安装QuartusII软件后,在桌面或者程序中启动QuartusII软件。

2.打开新工程向导

启动软件后,选择“File”菜单的“New Project Wizard”选项,打开新建工程向导,如图所示:

在新建工程向导的“介绍”页面中,单击“Next”按钮进入下一页,如图所示:

3.设置工程属性

如图所示,在新建工程向导的第一页对工程工作目录、工程名称以及顶层模块名称进行设置,如图所示:

点击Next,出现如图所示的界面:

Empty projet:空项目;Project template:项目模板。这个可以根据自己的实际情况进行选择,一般选择空项目。

4.添加设计文件

在新建工程向导的第二页选择位工程添加设计文件,如图所示:

如果还没有编写好代码文件可以先不用添加文件,直接点击Next选项,如果已经编写好了相关的代码文件,可以将其文件添加进来,根据实际情况进行选择。

5.选择FPGA器件

在新建工程向导的第三页,为工程配置相应的器件和参数,如图所示:选取的器件型号将在完全编译时将工程设计映射到对应的器件逻辑资源上。

点击Next,如图所示:

可以选择设计输入/综合以及仿真、时序分析的工具,可以根据具体的情况进行选择。点击Next之后就可以查看创建工程的一些信息,如图所示:

6.完成工程创建

配置完器件属性之后,点击finish完成工程的创建。如图所示:

选择软件左侧的工程浏览器,可以管理已添加的文件,如图所示:

二.设计输入

1.添加设计文件

如果在创建工程时没有为工程添加设计文件,可以选择“Project”菜单的“Add/Remove Files in Project”选项,为工程添加设计文件。如图所示:

同时,如果没有文件,可以选择自己编写,点击“file”选项下的“New”,如图所示:

弹出如下对话框,选择需要添加的文件。

2.配置器件属性

同样的,如果在创建工程时没有为工程配置器件型号及属性,可以在工程浏览器的工程实体图标上单击右键,选择“Device”选项,为工程配置器件属性,如图所示:

若在建立工程时已经配置好,则可以单击“Device & Pin Options...”按钮,进一步设置器件的相关属性,如图所示:

选择“Unused Pins”选项卡,将不使用的管脚配置为三态,如图所示:

3.分析工程

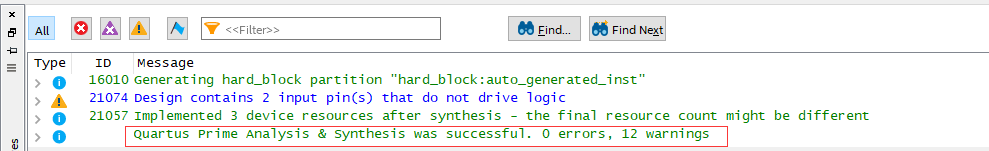

编写设计输入文件之后,首先要进行工程分析,目的是为了检查设计输入的语法。单击![]() “Start Analysis & Synthesis”按钮分析工程,如图所示:

“Start Analysis & Synthesis”按钮分析工程,如图所示:

三.约束设计

1.管脚分配

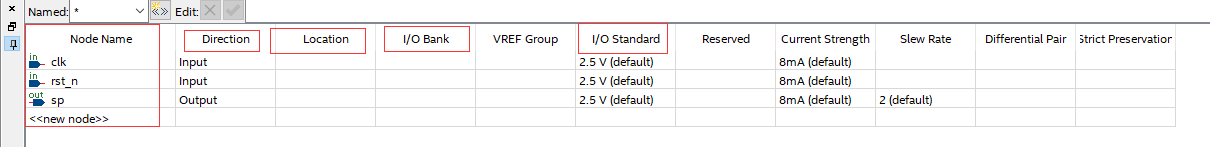

管脚分配的作用在于将设计输入文件的端口与实际的器件进行映射,实现设计输入模块端口在实际器件管脚上的实例化。在QuartusII软件中可以在管脚分配窗口中对管脚的分配进行设置,如图所示:

通过工具栏中的快捷按钮可以帮助用户快速的进行管脚分配,如图所示:

![]()

通过管脚分配主窗口中的管脚信息可以看到管脚的I/O种类、管脚的序号、Bank所在的位置、I/O使用的电压标准等,如图所示:

2.其它约束

除了对工程的管脚进行约束外,QuartusII软件还允许用户对其它的一些约束进行设置,假如面积约束、速度约束、时钟约束、资源约束等。这些约束都属于较为严格的工程设置。

四.编译工程

1.完全编译

有了完整的设计输入、完整的约束条件后,就可以对工程进行完全编译了,如图所示:

若在编译过程中出现错误提示,用户可以在信息栏中查看错误信息,修改所有存在的错误后重新编译,直到能够无错误的完成编译。

2.编译报告

QuartusII编译结束后,为用户提供一个完整而详细的编译报告。通过该报告,用户可以查看工程使用资源的情况及系统可以达到的性能。

五.功能仿真

1.选择仿真文件

选择QuartusII软件“File”菜单的“New”选项,打开新建其它文件对话框,选择新建波形图文件,如图所示:

2.添加观察信号

用户可以通过双击波形窗口中的空白区域为工程添加需要观察的信号,如图所示:

在打开的插入节点或总线对话框中,打开“Node Finder...”(节点查找器),如图所示。通过节点查找器,用户可以方便的选择需要观察的信号。

选择Filter:“Pin:all”,然后点击list列出所用输入/输出端口,如图所示:

选中所有信号,单击![]() 按钮,将选中信号加入到观察目标窗口中,如图所示:

按钮,将选中信号加入到观察目标窗口中,如图所示:

3.设置仿真时间最小间隔

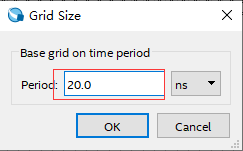

考虑到硬件环境提供的时钟频率(假设是50MHz),即时钟的周期为20ns,设置“Grid Size”为20ns。选择“Edit”菜单中的“Grid Size”选项进行设置,如图所示:

4.设置仿真时间长度

选择“Edit”菜单中的“End Time”选项,设置仿真时间长度为1ms,如图所示:

5.添加激励信号

选中clk信号,单击![]() 时钟按钮,将该信号设置为时钟波形,周期为20ns,如图所示。此信号代表了系统时钟。

时钟按钮,将该信号设置为时钟波形,周期为20ns,如图所示。此信号代表了系统时钟。

选中rst_n信号,单击![]() 高电平按钮,将该信号设置为1。此信号代表了复位信号。添加激励信号后,选中保存文件,此时的波形如图所示:

高电平按钮,将该信号设置为1。此信号代表了复位信号。添加激励信号后,选中保存文件,此时的波形如图所示:

6.生成功能仿真网表

点击“Tools”菜单的![]() 按钮,如图所示,进行功能仿真。

按钮,如图所示,进行功能仿真。

六.时序仿真

功能仿真后,如果波形没有问题,开始做时序仿真,检查波形延时对设计是否有影响。点击![]() 出现错误:

出现错误:

Run the Fitter, followed by the Timing Analyzer, before running the EDA Netlist Writer

解决办法是:

(1)首先点击Processing->Start->Start Fitter,如图所示:

等待边编译完成之后进行下一步。

(2)点击Processing->Start->Start Timing Analyzer,如图所示:

等待编译完成进行下一步。

(3)点击Simulation->Run Timing Simulation,运行时序仿真即可。

七.下载程序

仿真验证结束以后,用户就可以将工程下载到实际的开发板中进行验证了。选择Tools->Programmer选项或者点击快捷![]() 按钮打开下载界面,如图所示:

按钮打开下载界面,如图所示:

首先单击“Hardware Setup”按钮,选择下载电缆,然后选择下载模式JTAG(在线调试)模式或者AS(固化值EPCS配置芯片)模式,并选择对应的下载文件。连接好下载电缆之后,选中Program/Configure即可下载。

待续。。。。。。