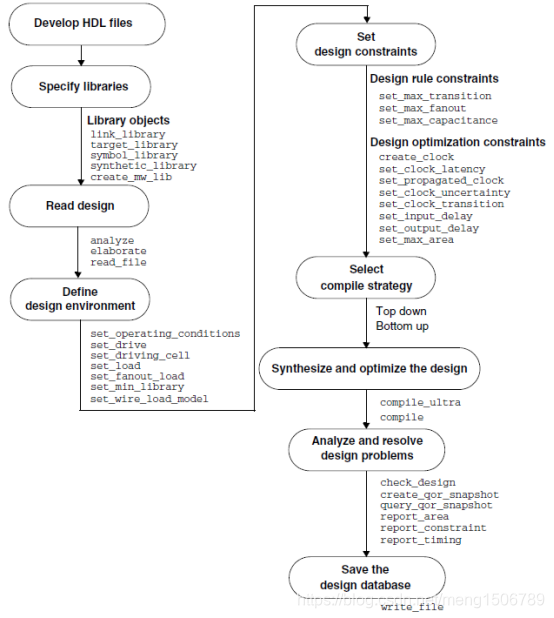

DC基本操作流程

1.建立目录及文件

[IC@IC lab1]$ ls -a

. .. common_setup.tcl dc_setup.tcl mapped rtl scripts .synopsys_dc.setup unmapped work

[IC@IC lab1]$ ls ./rtl

top.v

[IC@IC lab1]$ ls ./scripts

top.con

[IC@IC lab1]$ ls ./unmapped

[IC@IC lab1]$ ls ./mapped

[IC@IC lab1]$

目录内容简介:

/rtl 存放verilog设计文件 *.v

/script 存放约束文件 *.con

/unmapped 存放map之前的文件(目前是空目录)

/mapped 存放map之后的文件(目前是空目录)

.synopsys_dc.setup 在DC启动时自动source运行此文件的内容

common_setup.tcl 将User-defined 目录路径和文件路径存为变量

dc_setup.tcl 实现逻辑库和物理库的设置

(查找DC安装目录中包含的库文件:)

[IC@IC lab1]$ cd /opt/Synopsys/Synplify2015/

[IC@IC Synplify2015]$ pwd

/opt/Synopsys/Synplify2015

[IC@IC Synplify2015]$ find -name "*.db"

./auxx/syn/lc/corrlib_recipes/dummy.db

./doc/syn/ccsc/ccsc_examples/iq/ram/rams.db

./doc/syn/ccsc/ccsc_examples/iq/ram/ram.db

./doc/syn/ccsc/ccsc_examples/mem_control/ram/rams.db

./doc/syn/ccsc/ccsc_examples/mem_control/ram/ram.db

./doc/syn/examples/fsm/proc2.db

./doc/syn/examples/fsm/proc4.db

./doc/syn/examples/fsm/proc3.db

./doc/syn/examples/bc_view/verilog/db/example.db

./doc/syn/examples/bc_view/vhdl/db/example.db

./doc/syn/interfaces/cadence/tutorial/part2/top.pre.db

./doc/syn/interfaces/cadence/tutorial/LIB/class.db

./doc/syn/interfaces/valid/tutorial/part2/top.pre.db

./doc/syn/interfaces/viewlogic/tutorial/part2/top.pre.db

./doc/syn/interfaces/mentor/tutorial/part2/top.pre.db

./doc/syn/dv_tutorial/risc_design-flse-path/libs/core_typ.db

./doc/syn/dv_tutorial/risc_design/libs/core_typ.db

./doc/syn/dv_tutorial/risc_design-mult-clk/libs/core_typ.db

./doc/syn/tutorial/db/HOURS_FILTER.db

./doc/syn/tutorial/db/MUX.db

./doc/syn/tutorial/db/TOP.db

./doc/syn/tutorial/db/TIME_STATE_MACHINE.db

./doc/syn/tutorial/db/ALARM_BLOCK.db

./doc/syn/tutorial/db/ALARM_SM_2.db

./doc/syn/tutorial/db/ALARM_STATE_MACHINE.db

./doc/syn/tutorial/db/CONVERTOR_CKT.db

./doc/syn/tutorial/db/TIME_BLOCK.db

./doc/syn/tutorial/db/TIME_COUNTER.db

./doc/syn/tutorial/db/COMPARATOR.db

./doc/syn/tutorial/db/ALARM_COUNTER.db

./libraries/syn/nonlinear.db

./libraries/syn/lsi_lsc15.db

./libraries/syn/lsi_10k.db

./libraries/syn/lsi_7k.db

./libraries/syn/power_sample.db

./libraries/syn/tc6a_cbamc.db

./libraries/syn/class.db

./libraries/syn/power2_sample.db

./libraries/syn/lsi_9k.db

./libraries/syn/gtech.db

./libraries/syn/and_or.db

./libraries/syn/tc6a_cbacore.db

./libraries/syn/vhdlmacro.db

./libraries/syn/class_fpga.db

[IC@IC Synplify2015]$

2.文件内容介绍

(1)common_setup.tcl文件

############################################################################

# User-defined varibles for logical library setup in dc_setup.tcl

############################################################################

set ADDITIONAL_SEARCH_PATH "../ref/libs/mw_lib/sc/LM ./rtl ./scripts" ;

# Directories containing logic libraries, logical design and script files.

set TARGET_LIBRARY_FILES sc_max.db ; # Logical technology library file

set SYMBOL_LIBRARY_FILES sc.sdb ; # Symbol library file

############################################################################

# User-defined varibles for physical library setup in dc_setup.tcl

############################################################################

set MW_DESIGN_LIB TOP_LIB ; # User-defined Milkyway design library name

set MW_REFERENCE_LIB_DIRS ../ref/libs/mw_lib/sc ; # Milkyway reference libraries

set TECH_FILE ../ref/libs/tech/cb13_6m.tf ; # Milkyway technology

set TLUPLUS_MAX_FILE ../ref/libs/tlup/cb13_6m_max.tluplus ; # Max TLUPlus file

set MAP_FILE ../ref/libs/tlup/cb13_6m.map ; # Mapping file for TLUplus

echo "\ncommon_setup.tcl run to end...\n"

common_setup.tcl文件定义了库的名字和名称,上面是逻辑库,下面物理库。

5行:定义库的搜索路径,当找不到库时,从这个路径中寻找

8行:定义target library使用的库(注意,只是定义一个变量)

10行:定义图形库变量

15行:定义顶层设计库的变量名称

17行:定义milkyway(参考)库(的位置)

19行:定义工艺库(的位置)

21行:定义寄生参数库(的位置)

23行:定义工艺库和寄生参数库的映射关系库(的位置)

(2)dc_setup.tcl文件

################################################################

# Logical Library Settings

################################################################

set_app_var search_path "$search_path $ADDITIONAL_SEARCH_PATH"

set_app_var target_library $TARGET_LIBRARY_FILES

set_app_var link_library "* $target_library"

set_app_var symbol_library $SYMBOL_LIBRARY_FILES

################################################################

# Physical Library Settings

################################################################

set_app_var mw_reference_library $MW_REFERENCE_LIB_DIRS

set_app_var mw_design_library $MW_DESIGN_LIB

create_mw_lib -technology $TECH_FILE \

-mw_reference_library $mw_reference_library \

$mw_design_library

open_mw_lib $mw_design_library

set_tlu_plus_files -max_tluplus $TLUPLUS_MAX_FILE \

-tech2itf_map $MAP_FILE

echo "\ndc_setup.tcl run to end...\n"

dc_setup.tcl文件就是指定库了,而不是单单地定义了,set_app_var是定义DC内部变量,这个命令相比set来说,会检查设置名称拼写是否正确。

4行~7行:指定搜索路径个各种库的路径和名称

13行:指定milkyway(参考)库的名称

14行:指定当前设计的库的名称

16行:创建milkyway库,格式如图上面,需要工艺库、参考库、当前设计库

19行:打开当前的设计库

20行:加载寄生参数(库)

各种库的解释:

Link library 和 target library 统称为 technology library(即工艺库,习惯称之为综合库),technology library 由半导体制造商提供,包含相关 cell 的信息及设计约束标准,其中:

Target library: 在门级优化及映射的时候提供生成网表的 cell,即DC 用于创建实际电路的库,由晶圆厂提供。

Link library: 提供设计网表中的 cell,可以跟target_library使用同一个库,但是 DC 不用 link library中的 cell 来综合设计。当 DC 读入设计时,它自动读入由 link library 变量指定的库。当连接设计时,DC 先搜寻其内存中已经有的库,然后在搜寻由 link library 指定的库。

注:当读入的文件是门级网表时,需要把 link library 指向生成该门级网表的库文件,否则 DC 因不知道网表中门单元电路的功能而报错。关于工艺库里面的具体内容,后面会专门进行说明。

Symbol library 提供 Design Vision GUI 中设计实现的图形符号,如果你使用脚本模式而不使用 GUI,此库可不指定 Symbol library。

Synthetic library即为 Designware library ,名字上翻译是综合库,但却常称之为IP库,而不是直译。特殊的 Designware library 是需要授权的(比如使用多级流水线的乘法器),默认的标准 Designware 由 DC 软件商提供,无需指定。

Create mw lib :主要使用DC的物理综合的时候,需要生成物理库

(3).synopsys_dc.setup文件

运行上面两个脚本,并打印当前的配置

source common_setup.tcl

source dc_setup.tcl

# Verify Setting

echo "\n====================================="

echo "\nLibrary Settings:"

echo "search_path: $search_path"

echo "link_library: $link_library"

echo "target_library: $target_library"

echo "symbol_library: $symbol_library"

echo "mw_reference_library: $mw_reference_library"

echo "mw_design_library: $mw_design_library"

echo "\n====================================="

echo "\n.synopsys_dc.setup run to end...\n"

(4)./rtl/top.v文件

`timescale 1ns / 1ps

module Adder(

input clk,

input rst_n,

input [7:0] a,

input [7:0] b,

output reg [8:0] p

);

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

p <= 0;

else

p <= a + b;

end

endmodule

(5)./scripts/top.con文件

(运行可能会报错,这里仅提供一个参考模板)

set lib_name cb13fs120_tsmc_max

current_design Adder

# Reset all constraints

reset_design

# Create clock object and set uncertainty

create_clock -period 2 [get_ports clk]

set_clock_uncertainty 0.2 [get_clocks clk]

# Set constraints on input ports

suppress_message UID-401

set_driving_cell -library $lib_name -lib_cell sdcfq1 [remove_from_collection [all_inputs] [get_ports clk]]

set_input_delay 0.1 -max -clock clk [remove_from_collection [all_inputs] [get_ports clk]]

set_input_delay 1.2 -max -clock clk [get_ports a_in]

# Set constraints on output ports

set_output_delay 1 -max -clock clk [all_outputs]

set_load [expr [load_of $lib_name/an02d0/A1] * 15] [all_outputs]

5行的reset_design 是剔除之前所有的约束,防止影响下面的约束。

3.运行DC

[IC@IC lab1]$ dc_shell -topo

Design Compiler Graphical

DC Ultra (TM)

DFTMAX (TM)

Power Compiler (TM)

DesignWare (R)

DC Expert (TM)

Design Vision (TM)

HDL Compiler (TM)

VHDL Compiler (TM)

DFT Compiler

Design Compiler(R)

Version K-2015.06 for linux64 - May 28, 2015

Copyright (c) 1988 - 2015 Synopsys, Inc.

This software and the associated documentation are proprietary to Synopsys,

Inc. This software may only be used in accordance with the terms and conditions

of a written license agreement with Synopsys, Inc. All other use, reproduction,

or distribution of this software is strictly prohibited.

Initializing...

Starting shell in Topographical mode...

common_setup.tcl run to end...

Error: Technology file '../ref/libs/tech/cb13_6m.tf' does not exist. (MWUI-005)

Error: Cannot open library TOP_LIB for write. (MW-006)

Error: File '../ref/libs/tlup/cb13_6m_max.tluplus' does not exist or it is unreadable. (RCEX-070)

dc_setup.tcl run to end...

=====================================

Library Settings:

search_path: . /opt/Synopsys/Synplify2015/libraries/syn /opt/Synopsys/Synplify2015/minpower/syn /opt/Synopsys/Synplify2015/dw/syn_ver /opt/Synopsys/Synplify2015/dw/sim_ver /opt/Foundary_Library/TSMC90/aci/sc-x/synopsys ../ref/libs/mw_lib/sc/LM ./rtl ./scripts

link_library: * sc_max.db

target_library: sc_max.db

symbol_library: sc.sdb

mw_reference_library: ../ref/libs/mw_lib/sc

mw_design_library: TOP_LIB

=====================================

.synopsys_dc.setup run to end...

Initializing gui preferences from file /home/IC/.synopsys_dv_prefs.tcl

dc_shell-topo>

可以看到在运行dc_setup.tcl时出现了Error,这是因为我们暂时没有这些库文件,无法正确加载。

可以在dc_shell> 中运行以下两个命令:

check_library # 检查逻辑库和物理库的一致性,检查可能不会通过,结果不影响综合的话,可以忽略

checktluplus_files # 检查寄生参数文件和工艺库文件的一致性:(物理综合的时候需要检查),通过的话会有三个passed

4.读入设计和查看设计

read_file -format verilog ./rtl/top.v # 读入设计

current_design # 查看当前设计

current_design TOP # 设置当前设计为TOP,要综合哪个模块,就把哪个模块设置为当前设计

link # Link设计,查看当前要综合的设计是否缺少子模块,返回值是1,说明子模块完整

write -hierarchy -f ddc -out unmapped/top.ddc # 以ddc的格式保存未映射的设计,保存在unmapped文件夹中

list_designs # 查看内存中的设计,带*的设计为当前设计

list_libs # 查看内存中的库

5.约束设计

source ./scripts/top.con

6.综合设计

compile_ultra # 这是在拓扑模式下进行综合的命令

# 以下是综合后的检查(检查不通过的需要优化,这里只作为一般流程,没有进行优化)

report_qor > qor.report # 生成report信息并保存在qor.report文件中

report_constraint -all # 查看是否违规

report_timing # 查看时序报告

report_area # 查看面积情况

# 保存综合后的设计,保存在mapped文件夹

write -format verilog -hier -output ./mapped/top.gv

write -hierarchy -format ddc -output ./mapped/top.ddc

7.总结