一个完备的嵌入式系统硬件架构有哪几部分构成?

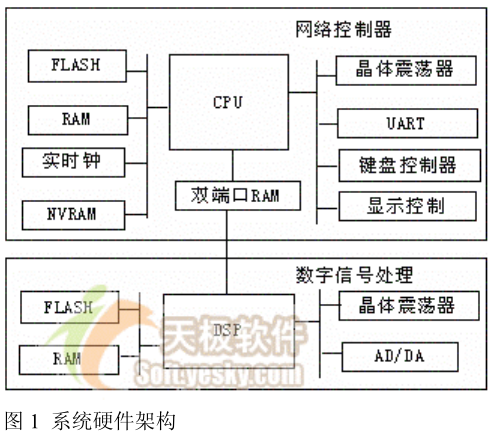

图 1 给出了本文的讨论所基于的硬件平台,实际上,这也是大多数嵌入式系统的硬件平台。它包括两部分:

(1) 以通用处理器为中心的协议处理模块,用于网络控制协议的处理;

(2) 以数字信号处理器(DSP)为中心的信号处理模块,用于调制、解调和数/模信号转换。

本文的讨论主要围绕以通用处理器为中心的协议处理模块进行,因为它更多地牵涉到具体的 C 语言编程技巧。而 DSP 编程则重点关注具体的数字信号处理算法,主要涉及通信领域的知识,不是本文的讨论重点。着眼于讨论普遍的嵌入式系统 C 编程技巧,系统的协议处理模块没有选择特别的 CPU,而是选择了众所周知的 CPU 芯片--80186,每一位学习过《微机原理》的读者都应该对此芯片有一个基本的认识,且对其指令集比较熟悉。80186 的字长是 16 位,可以寻址到的内存空间为 1MB,只有实地址模式。C 语言编译生成的指针为 32 位(双字),高 16 位为段地址,低 16 位为段内编译,一段最多 64KB。

图 1 给出了本文的讨论所基于的硬件平台,实际上,这也是大多数嵌入式系统的硬件平台。它包括两部分:

(1) 以通用处理器为中心的协议处理模块,用于网络控制协议的处理;

(2) 以数字信号处理器(DSP)为中心的信号处理模块,用于调制、解调和数/模信号转换。

本文的讨论主要围绕以通用处理器为中心的协议处理模块进行,因为它更多地牵涉到具体的 C 语言编程技巧。而 DSP 编程则重点关注具体的数字信号处理算法,主要涉及通信领域的知识,不是本文的讨论重点。着眼于讨论普遍的嵌入式系统 C 编程技巧,系统的协议处理模块没有选择特别的 CPU,而是选择了众所周知的 CPU 芯片--80186,每一位学习过《微机原理》的读者都应该对此芯片有一个基本的认识,且对其指令集比较熟悉。80186 的字长是 16 位,可以寻址到的内存空间为 1MB,只有实地址模式。C 语言编译生成的指针为 32 位(双字),高 16 位为段地址,低 16 位为段内编译,一段最多 64KB。

下面是各模块的功能介绍:

(1)协议处理模块中的 FLASH 和 RAM 几乎是每个嵌入式系统的必备设备,前者用于存储程序,后者则是程序运行时指令及数据的存放位置。系统所选择的 FLASH 和 RAM 的位宽都为 16 位,与 CPU 一致。

(2)NVRAM(非易失去性 RAM)具有掉电不丢失数据的特性,可以用于保存系统的设置信息,譬如网络协议参数等。在系统掉电或重新启动后,仍然可以读取先前的设置信息。其位宽为 8 位,比 CPU 字长小。文章特意选择一个与 CPU 字长不一致的存储芯片,为后文中一节的讨论创造条件。

(3)UART 则完成 CPU 并行数据传输与 RS-232 串行数据传输的转换,它可以在接收到[1~MAX_BUFFER]字节后向 CPU 提出中断,MAX_BUFFER 为 UART 芯片存储接收到字节的最大缓冲区。

(4)键盘控制器和显示控制器则完成系统人机界面的控制。以上提供的是一个较完备的嵌入式系统硬件架构,实际的系统可能包含更少的外设。之所以选择一个完备的系统,是为了后文更全面的讨论嵌入式系统 C 语言编程技巧的方方面面,所有设备都会成为后文的分析目标。