在计算机的微体系结构中,没有一般通用的设计方式。所以,这里用JVM ( java虚拟机,Java Virtual Machine)

指令系统层的子集作为例子。

使用微体系结构Mic-1。

1.

微程序中的有一组变量,称之为计算机的

状态

(state),所有的函数都可以访问这些变量。比如:程序计数器(PC)就是状态的一部分,它将指示下一个要执行的函数。在每条指令执行过程中,PC都会指向下一条要执行的指令。

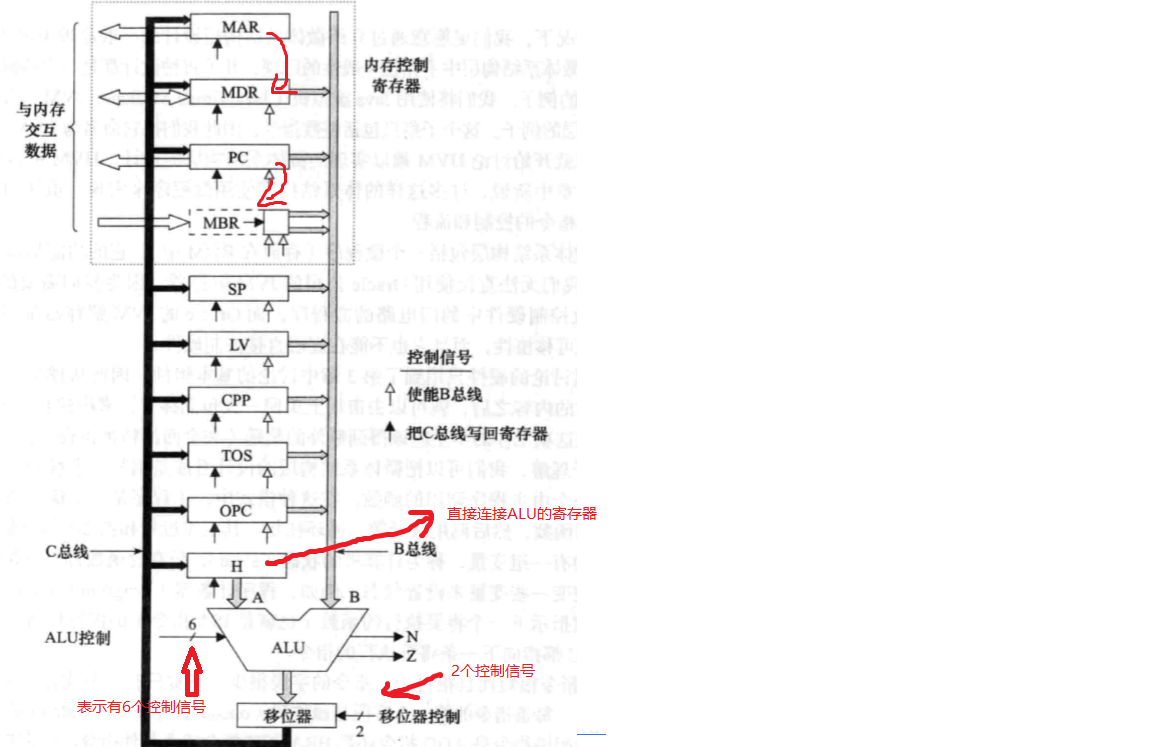

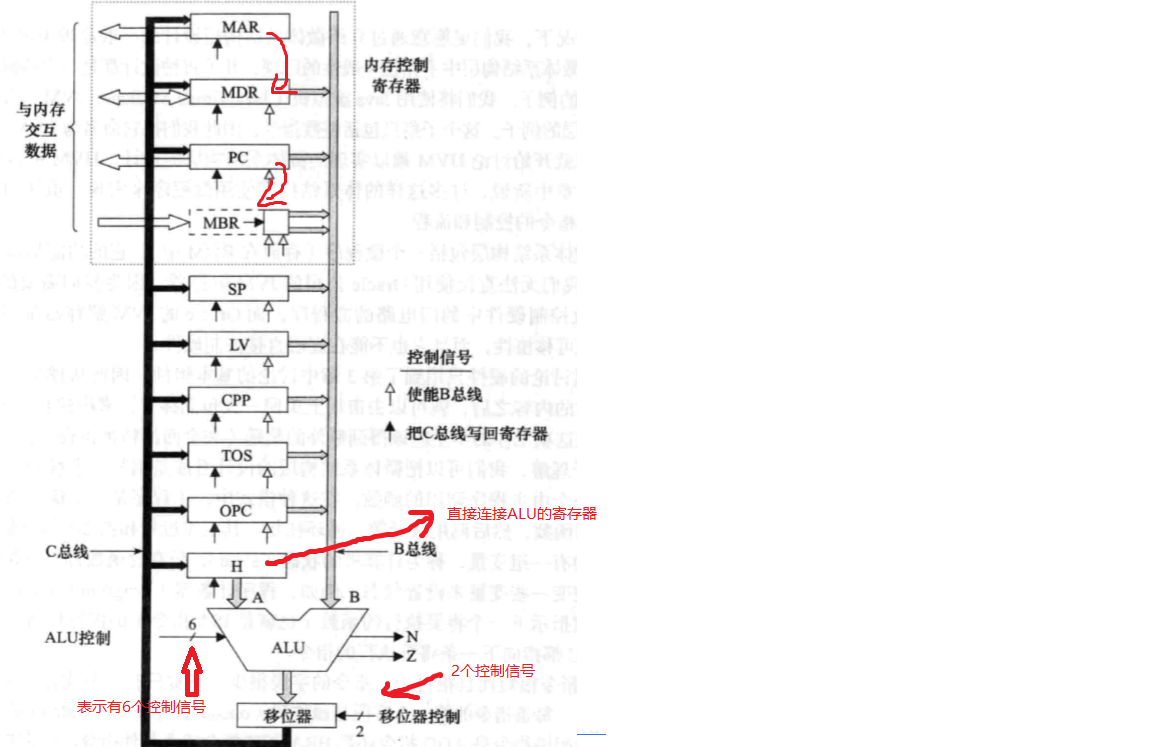

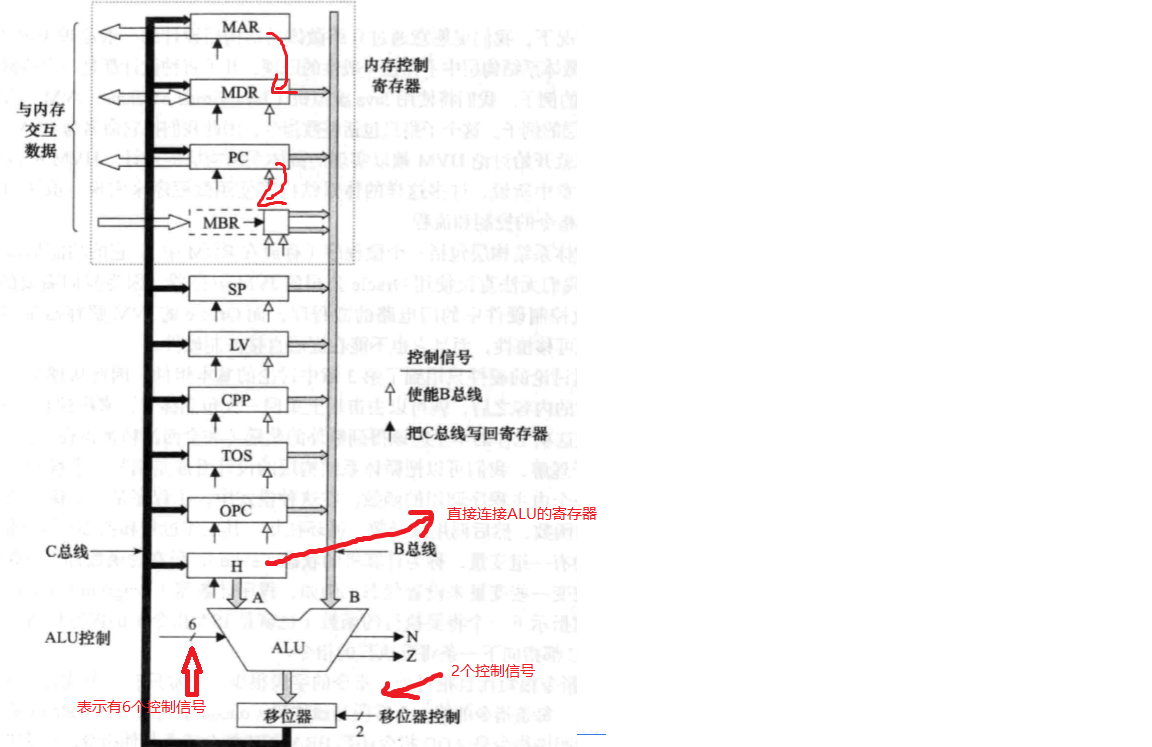

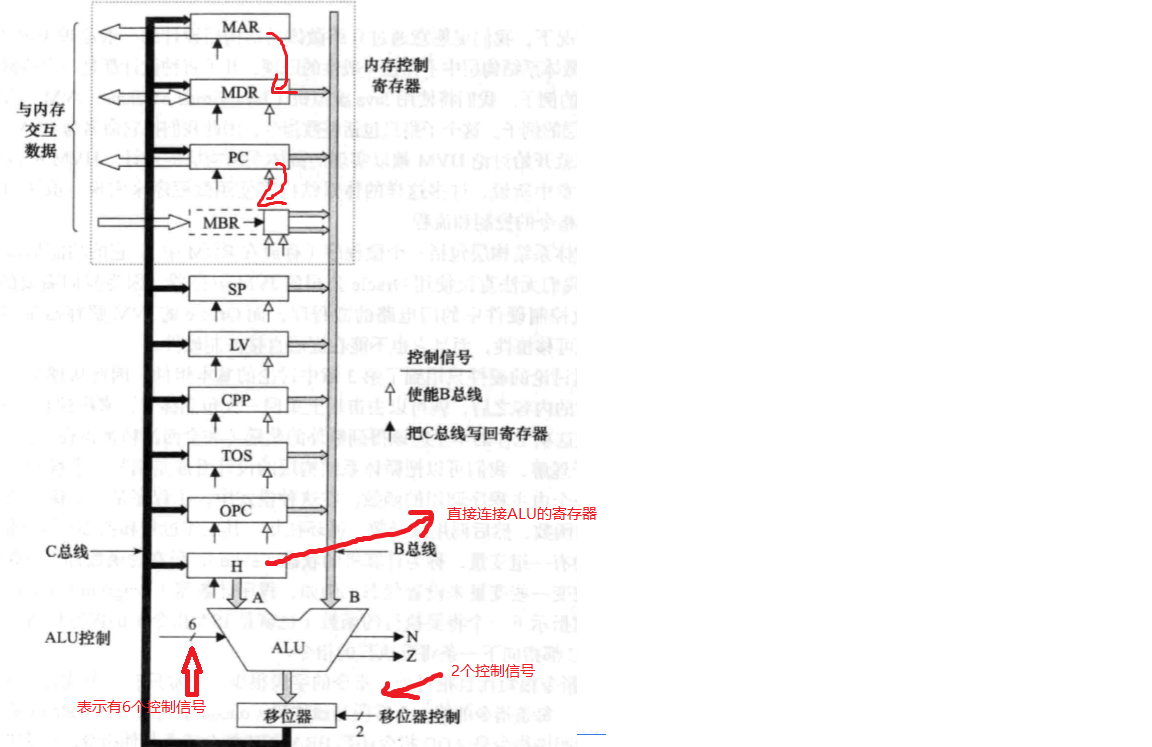

2.数据通路

①如图所示的是CPU的一部分,叫做数据通路。

②大多数寄存器可以通过B总线传送其内容,而ALU通过C总线将内容输出到寄存器中。A总线将内容从寄存器H输出到ALU中。

③图中的ALU由6位控制信号决定。分别是决定ALU操作的F0和F1,输入A和B的ENA和ENB,转换左输入的INVA,最低位进位的INC。这几种控制信号的不同搭配,来实现以下功能↓

④ALU的两个输出:左输入(A)、右输入(B)。左输入连接寄存器H,右输入连接总线B。

⑤这些寄存器下方的黑箭头表示用C总线写入寄存器的控制信号,白箭头表示把寄存器内容写入B总线的控制信号。

3.数据通路的时序

通过计算机的主振始终,得到每个周期开始时候的短脉冲。

总结起来分为四个步骤:

①在脉冲的下沿,驱动各个门电路的信号开始简历,建立时间有限且已知,记作

△w。

②然后,需要传送数据的寄存器被选中,开始驱动B总线,等到数值稳定,需要时间△X。

③ALU在一段时间内进行计算,所需时间为△y。

④得出的结果将沿着C总线传送到寄存器,在时钟信号的脉冲上升之前完成,所需时间△z。

*:△z之后的时间片是为系统误差预留的空间。因为时序有可能不那么精确。

*:这是个子周期都是有隐含的边界的。

*:这仅仅是一个数据通路的周期,内存访问的周期与此不同。

4.内存操作

①CPU通过两种不同的方式和内存通讯:32位按字寻址的端口、8位按字节寻址的端口。

②32位的端口是由MAR和MDR控制的。

③8位端口是由PC控制的,它把字节存入MBR的低8位。且这个端口只能读不能写。

④由于寻址的方式不同,所给的寄存器不同,操作将不同。如:将2放入PC中,加上使能信号,然后执行读内存的第二个字节的值,存放在MBR的低8位中。而将2放入MAR中,加上使能信号,可执行读内存的字节8~11(即第2个字),再放入MDR中。

这两者的区别是他们的功能所决定的。

5.微指令

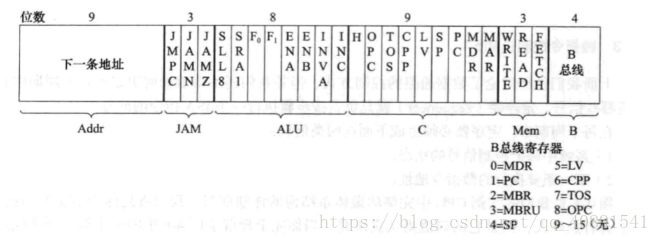

①在图中的数据通路之中。我们一共需要29个控制信号。分为5组。

9个用于将C总线的数据写入寄存器的控制信号

9个输出到B总线的寄存器的势能信号

8个控制ALU和移位器功能的信号

2个通过MAR/MDR指示内存读写的信号

1个通过PC/MBR指示内存取数的信号

②通过这29个信号的值,便可以定义一个数据通路的周期的操作。

③我们通过9+4+8+2+1=24个控制信号来控制数据通路,而这24只控制了一个周期的数据通路。控制信号的第二部分就需要决定下一个周期的操作。

④图中的格式包括24位控制信号和2个附加字段:NEXT_ADDRESS和JAM。总共分为6组,然后给出组名相应解释如下。

Addr:下一条可能执行的微指令的地址

JAM:决定如何选择下一条微指令

ALU:ALU和移位器的操作

C:选择C总线的数据将要写入的寄存器

Mem:内存操作

B:选择B总线的数据来源

*:这是可用的一种微指令格式,来控制数据总线的一个周期。

6.定序器(sequencer)

①定序器用于负责按照步骤执行一条ISA指令的部件。

②在每个周期,定序器需要生成下面两类信息:

a.系统中每个控制信号的状态

b.下一条要执行的微指令地址

7.微体系结构Mic-1

①这张图虽然看起来复杂,但值得认真研究来懂得微指令体系。图中整体分为两个半部分:左面的数据通路和右面的控制部分。其中,数据通路在上上上上张图已经讨论过了。

②最大块的灰色方框是控制存储器,只用于保存微指令而非ISA指令。包括512个字,每个字一条36位的微指令。

③主存中的命令是按照其地址顺序执行的(除非遇到跳转命令),而微指令是链式存储(即每条微指令都明确之处它的下一条微指令)。

④控制存储器的 内存数据寄存器 称为

微指令寄存器(MicroInstruction Register,MIR )

,在图中的右边有出现,它的功能是保存当前的微指令,这条微指令将驱动控制信号来操作数据通路。

⑤控制存储器中保存的 Addr信号组 和 J信号组(用于JAM),控制下一个微指令地址的选择。

⑥把ALU的状态保存在N和Z中可以保证计算MPC时使用正确而且稳定的值。

⑦对照着“数据通路的时序”那图,操作顺序如下:

1)从MPC所指的控制存储器位置读出微指令加载至MIR。对应时间

△w。

2)一旦微指令在MIR中简历,各个不同信号就开始在数据通路中传送了,某个或某些寄存器就把值放在B总线上,对应△X。

3)在△y中,ALU、N、Z 和 移位器的工作都在这一段时间内完成 且 输出都稳定了。

4)在△z中,移位器的输出通过C中线倒带寄存器。

*:最后,每条下一条微指令的地址都是在上一条微指令的后面已经指出了的。

*:在MIR加载稳定了之后,下条微指令的地址计算就开始了。首先,9位的NEXT_ADDRESS字段拷贝到MPC中。拷贝同时检查JAM字段,如果值为000,则什么都不做。而不为000,则在拷贝完成后,MPC就指向下一条微指令。

⑧看微指令图:

*:Addr就是NEXT_ADDRESS,所说的都是下一条地址。

1)如果JAM中,所有字段都是0,则不做任何事。下一条将要执行的微指令的地址就是当前微指令的NEXT_ADDRESS字段中的9位数。

2)如果JAM中,JAMN为1,则N触发器将和MPC最高位执行或操作。

3)如果JAM中,JAMZ为1,则Z触发器将和MPC最高位执行或操作。

4)如果JAM中,JAMZ和JAMN都为1,则N、Z和MPC最高位都进行或操作。这个过程用逻辑表达式为:

(MPC中就是存储的NEXT_ADDRESS字段)

*:使用N、Z触发器是因为在时钟的上升沿之后(这时时钟处于高电平),B总线不再被驱动,ALU的输出可能不正确。因此把ALU的状态保存在N和Z 可以保证计算MPC时使用正确而且稳定的值。

5)如果JAM中,第3位JMPC为1,那么MBR中的8位将和当前微指令的NEXT_ADDRESS字段的低8位按位进行或操作。计算结果送入MPC。

6)如果JAM中,JMPC为0,那么直接将NEXT_ADDRESS送给MPC。

7)如果NEXT_ADDRESS的最高位已经是1,那么使用JAMN和JAMZ没有意义。

*:这种把MBR和NEXT_ADDRESS相或的操作 适用于 有效的实现 跳转(jump)。典型的用法是这样的,MBR包涵一个操作码,这样使用JMPC就可以根据操作码选择下一条要执行的微指令。

写在最后:当然,图中的有一些东西我们没有解释。比如:SP、LV等等,这些我们这里暂时理解成普通寄存器。之后我们会更加详细地讨论的。