为了解决在多线程场景下,对共享变量的安全访问问题,CPU使用了两种方式:

(1)总线加锁的方式,退化成串行工作,工作效率低下。

(2)缓存一致性协议的方式(CPU中数据的最小存储单元是缓存行。MESI:是指缓存行中的数据的四种不同状态。M-修改,E-互斥,S-共享,I-无效)。

总线嗅探机制:CPU1在从主内存中读取完X之后,会把该数据存在CPU1的缓存行中,同时,也会时刻去嗅探总线上关于该数据的状态。

这个状态,也就是其他缓存行对该数据的读写状态。

(1)如果有多个CPU准备同步数据到主内存中时,这个时候需要去做裁决

(2)

【是顺序性,不保证连贯性】

CPU Cache概述

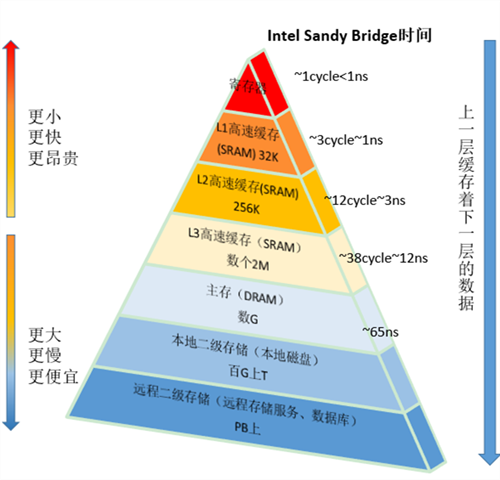

随着CPU的频率不断提升,而内存的访问速度却没有质的突破,为了弥补访问内存的速度慢,充分发挥CPU的计算资源,提高CPU整体吞吐量,在CPU与内存之间引入了一级Cache。随着热点数据体积越来越大,一级Cache L1已经不满足发展的要求,引入了二级Cache L2,三级Cache L3。(注:若无特别说明,本文的Cache指CPU Cache,高速缓存)CPU Cache在存储器层次结构中的示意如下图:

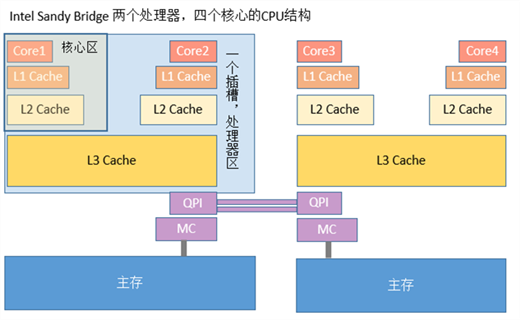

计算机早已进入多核时代,软件也越来越多的支持多核运行。一个处理器对应一个物理插槽,多处理器间通过QPI总线相连。一个处理器包含多个核,一个处理器间的多核共享L3 Cache。一个核包含寄存器、L1 Cache、L2 Cache,下图是Intel Sandy Bridge CPU架构,一个典型的NUMA多处理器结构:

作为程序员,需要理解计算机存储器层次结构,它对应用程序的性能有巨大的影响。如果需要的程序是在CPU寄存器中的,指令执行时1个周期内就能访问到他们。如果在CPU Cache中,需要1~30个周期;如果在主存中,需要50~200个周期;在磁盘上,大概需要几千万个周期。充分利用它的结构和机制,可以有效的提高程序的性能。

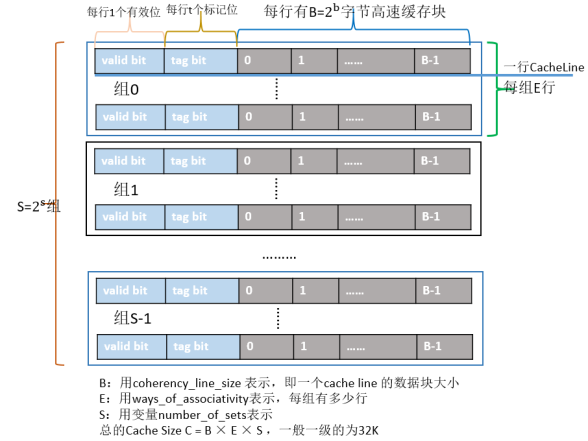

以我们常见的X86芯片为例,Cache的结构下图所示:整个Cache被分为S个组,每个组是又由E行个最小的存储单元——Cache Line所组成,而一个Cache Line中有B(B=64)个字节用来存储数据,即每个Cache Line能存储64个字节的数据,每个Cache Line又额外包含一个有效位(valid bit)、t个标记位(tag bit),其中valid bit用来表示该缓存行是否有效;tag bit用来协助寻址,唯一标识存储在CacheLine中的块;而Cache Line里的64个字节其实是对应内存地址中的数据拷贝。根据Cache的结构题,我们可以推算出每一级Cache的大小为B×E×S。

那么如何查看自己电脑CPU的Cache信息呢?