文章目录

中断断尾

当多个中断同时被触发,优先级高的中断中断响应完成后不需要进行运行环境的恢复,而是直接进行优先级次高的中断,全部中断执行完成后,再恢复运行环境。具有中断断尾功能,可以省去两次堆栈的操作。

SWD调试接口

SWD只需要使用芯片两根引脚(SWDIO SWCLK)就可以实现对内核芯片的在线仿真与调试,使用SWD可以向芯片flash存储器固化程序,而且具有指令跟踪执行的功能。

有几个优点:

- SWD在高速模式下更加可靠,在大数据量的情况下,JTAG下载程序可能会失败,但是SWD发生的几率会小很多,基本使用JTAG的仿真模式情况下可以直接使用SWD模式。

- GPIO口恰好缺一个的时候,我们可以使用SWD仿真,这种模式支持更少的引脚。

- 在板子规划设计时,推荐使用SWD模式,需要引脚少,需要的PCB空间就小。

JTAG调试接口

JTAG(Joint Test Action Group,联合测试行动小组)是一种国际标准测试协议(IEEE 1149.1兼容),主要用于芯片内部测试。现在多数的高级器件都支持JTAG协议,如ARM、DSP、FPGA器件等。标准的JTAG接口是4线:TMS、 TCK、TDI、TDO,分别为模式选择、时钟、数据输入和数据输出线。 相关JTAG引脚的定义为:

- TMS:测试模式选择,TMS用来设置JTAG接口处于某种特定的测试模式;

- TCK:测试时钟输入;

- TDI:测试数据输入,数据通过TDI引脚输入JTAG接口;

- TDO:测试数据输出,数据通过TDO引 脚从JTAG接口输出;

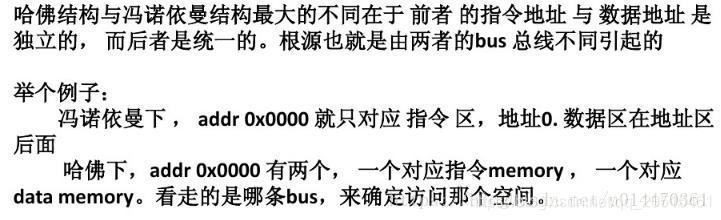

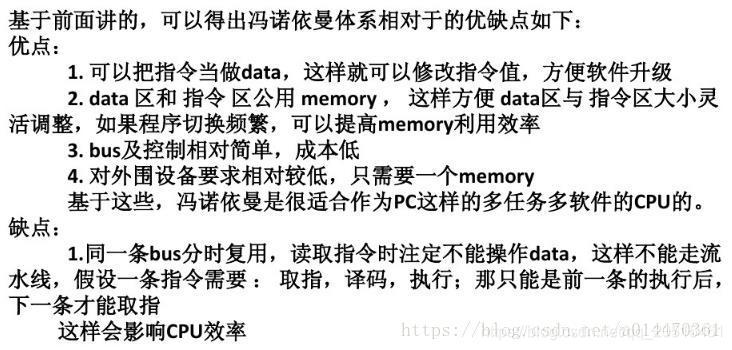

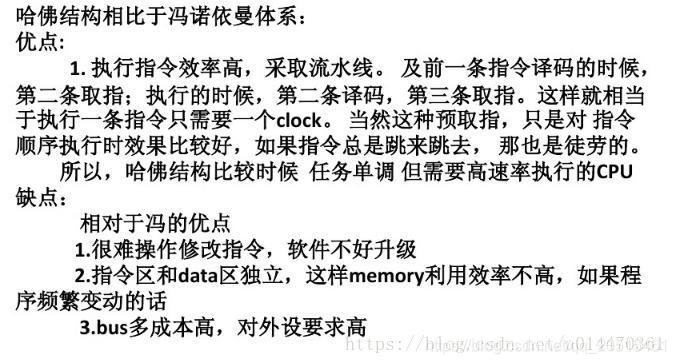

哈佛结构和冯诺依曼结构

哈佛结构是为了高速数据处理而采用的,因为可以同时读取指令和数据(分开存储的)。大大提高了数据吞吐率,缺点是结构复杂。通用微机指令和数据是混合存储的,结构上简单,成本低。假设是哈佛结构:你就得在电脑安装两块硬盘,一块装程序,一块装数据,内存装两根,一根储存指令,一根存储数据……

是什么结构要看总线结构的。51单片机虽然数据指令存储区是分开的,但总线是分时复用的,所以顶多算改进型的哈佛结构。ARM7 ARM9虽然是哈佛结构,但是之前的版本也还是冯·诺依曼结构。早期的X86能迅速占有市场,一条很重要的原因,正是靠了冯·诺依曼这种实现简单,成本低的总线结构。处理器虽然外部总线上看是诺依曼结构的,但是由于内部CACHE的存在,因此实际上内部来看已经算是改进型哈佛结构的了。

冯诺依曼结构组成:运算器、控制器、存储器、输入设备、输出设备

RAM 写回模式(write back)

具有RAM写回模式的区域,又称为快速RAM区,当内核向RAM写入数据时,不是直接将数据写入RAM,而是写入更快速的缓存中,当缓存写满或者总线空闲时,将缓存中的数据自动写入到RAM区域。因此,写回特性的RAM中的数据有可能与其缓存中的数据不同,当数据较少时,数据将保存在缓存中,而不用写入RAM。

片上RAM(SRAM)一般是写回特性的缓存机制

RAM 写通模式(write through)

当内核向RAM区域写入数据时,通过缓存直接将数据写入到ram区域。写通特性下RAM中数据和缓存中数据是相同的。

字地址半字地址

字地址:地址最低两位为0,如0x0000 0000,0x0000 0004,0x0000 0008;

半字地址:地址最低位为0,如0x0000 0000,0x0000 0002,0x0000 0004;

字地址都是半字地址

大端模式小端模式

小端模式下:数据字的高字节存储在字地址的高端,数据字的低字节存储在字地址的低端;

大端模式:数据字的高字节存储在字地址的低端,数据字的低字节存储在字地址的高端;

大端模式是保序的,每个字节内的位的顺序保持从高到低不变

服务器一般是大端模式

进程模式和手柄模式

ARM指令集与Thumb指令集

由于Thumb指令在某些特殊情况下可能比ARM指令更有效,所以它在很多方面得到了广泛的应用。但是Thumb知识ARM指令集的一个子集,它不能独立组成一个应用系统,所以在很多情况下应用程序需要二者的混合编程,这就必然存在ARM与Thumb状态之间函数调用的问题。

ARM/Thumb之间的状态切换是通过一条专用的转移交换指令BX来实现的。BX指令以通用寄存器位操作数,通过拷贝Rn到PC来实现4GB空间范围内的一个绝对跳转。BX利用Rn寄存器中目的地址值的最后一位来判断跳转后的状态。当最后一位为0时,表示转移到ARM状态;当最后一位为1时,表示转移到Thumb状态。