(参考:https://mp.weixin.qq.com/s/XznSbJBlAdZvtAIpyzajAA)

一、formality简介

在现在的数字集成电路设计流程中,有很多步骤都需要进行验证。随着数字集成电路的规模、复杂度,以及在验证过程中需要的仿真矢量的不断增加,用传统的仿真器进行验证越来越成为整个设计过程中的瓶颈之所在。

所谓形式验证,就是通过比较两个设计在逻辑功能上是否等同的方法来验证电路的功能。这种方法的优点在于它不仅提高了验证的速度,可以在相当大的程度上缩短数字设计的周期,而且更重要的是,它摆脱了工艺的约束和仿真testbench的不完全性,更加全面地检查了电路的功能。

Formality是Synopsys的形式验证工具,你可以用它来比较一个修改后的设计(如ECO)和它原来的版本,或者一个RTL级的设计和它的门级网表,再或者综合后的门级网表和做完布局布线及优化之后的门级网表在功耗上是否一致。

二、formality验证流程

- 启动方式

formality有两种启动方式:图形用户界面GUI和命令行界面。

GUI界面启动命令:formality;

命令行启动命令:fm_shell;

- 接下来的步骤以GUI界面为例。

打开终端,输入formality命令后回车,打开软件的GUI界面,如下图所示:

软件的验证流程按照软件上的顺序依次执行,下面分别介绍。

0. Guidance

- Reference

- Implementation

- Setup

- Match

- Verify

- Debug

1)Guidance

其中0.Guidance用来选择DC在进行逻辑综合时产生的.svf文件,该文件记录了DC在逻辑综合时所做的一些优化。

选择“Guidance”进行添加即可。添加完成后点击“Load Files”即可在右侧的Currently Loaded窗口中看到该文件,下侧的log一栏显示“1”即表示设置成功,上方0.Guidance上也会显示一个绿色的小对勾,如下图所示。

注意:如果设计非常小,并在网表中并未做什么优化,可以不用执行该操作。

2)Reference

设置Reference design,点击formality图形界面的“1.Reference”按钮,可以看到有3个步骤需要依次执行,如下图所示。分别是:1.Read Design File ,2.Read DB Libraries ,3.Set Top Design。

a. Read Design File

首先需要读取自己设计的RTL级的Verilog文件。点击“1.Read Design File”之后选择 “Verilog”按钮,出现添加Verilog文件的对话框。选中所有的rtl级文件,点击Open按钮,打开Verilog源代码。如下图所示:

如果RTL代码中用到了某些Design Ware库中的一些IP,还需要设置搜索目录,如果没有用到的话可以跳过该步。

设置搜索目录,点击option按钮,出现Set Verilog Read Option对话框,如下图所示。选择Variable,在DesingWare root directory (hdlin_dwroot)出输入选择DC的软件安装目录,设置完成后点击OK按钮。

之后点击点击“Load Files”完成添加rtl级文件。

之后点击点击“Load Files”完成添加rtl级文件。

b. Read DB Libraries

如果RTL代码中例化了一些IO或者Macro,或者还直接例化了标准单元库中的Tie high/low Cells,那么需要读取它们的DB文件。由于本设计中直接例化了标准单元库中的Cells并且含有IO,所以需要读取标准单元库和IO的.db文件。

点击“2.Read DB Libraries” 后选择“DB”按钮,选取IO的.db格式文件和标准单元库的.db文件,点击open打开,之后点击Load Files。

c. Set Top Design

点击“3.Set Top Design”按钮,设置Reference中的顶层设计,本实例中的顶层文件是top.v。

在1.Choose a library中选择WORK;

在2.Choose a design中选择top(顶层设计的模块名);

在3.Set and link the top design中点击Set Top,指定顶层设计,设置完成后在1.Reference按钮上出现绿色的对号符。

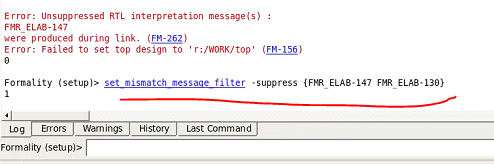

注意:设置top文件过程中可能会遇到报以下错误:

参考论坛(http://bbs.eetop.cn/thread-867168-1-1.html?_dsign=084d94be),在下侧输入框加入下述语句:(意思是对这些问题只报warning, 不作为错误处理),重新设置top即可设置成功。

set_mismatch_message_filter -suppress {FMR_ELAB-147 FMR_ELAB-130}

3) Implementation

点击“2.Implement”按钮,设置Implementation Design,可以看到也是有3个步骤需要依次执行,如下图所示。分别是:1.Read Design File ,2.Read DB Libraries ,3.Set Top Design。

a. Read Design File

在“1.Read Design Files”中点击Verilog,出现Add verilog files对话框,选择DC综合导出的verilog网表文件top.mapped.v,如下图所示。 之后点击“Load Files”加载网表文件。

b. Read DB Libraries

点击“2.Read DB Libraries”,这里添加门级网表中用到的相关.db文件,由于本设计所需所有.db文件在之前已经读入过了,所以可以跳过该步。

c. Set Top Design

点击“3.Set Top Design”按钮,设置Reference中的顶层设计:

在1.Choose a library中选择WORK;

在2.Choose a design中选择top(顶层设计的模块名);

在3.Set and link the top design中点击Set Top,指定顶层设计,设置完成后在“2.Implementation”按钮上出现绿色的对号符。

4) Setup

设置环境,在这一步主要是设置常量,比如对应一些增加了SCAN扫描链和JTAG链的设计,需要设置一些常量,使这些SCAN和JTAG等功能禁止。如果设计中采用了门控时钟技术,也需要进行一些相应的设置。

由于本实例的综合中没有添加SCAN和JTAG链,且设计中没有采用门控时钟技术,故可以省略这一步。

5) Match

检查reference design和Implemention design的比较点是否匹配:

点击“4.Match”按钮,选择“Run Matching”按钮,进行匹配检查。

出现下图所示结果:没有不匹配的比较点,可以进入下一步。

6) Verify

前面的Reference和Implementation环境都已搭建好,下面可以验证RTL级代码和门级网表功能是否一致。

选择“5.Verify”按钮,进行形式验证,如下图所示:

验证结束,结果出现“Verification succeeded!”的对话框,如下图所示,这说明两种功能一致。到此,完成形式验证。

7) Debug

如果验证失败,系统直接进入Debug工作区。在Failing Points的报告工作区里显示两设计的出不一致的比较点,在Failing Points的报告工作区内点击鼠标右键,选择Show All Cone Size,在Size栏里显示每个compar point所包含的cell的数目。一般调试是从cell数目最小的compare point开始。选择Reference中的cell数目最小的compare point,点击鼠标右键,选择菜单中的view Logic Cones,出现Logic Cones View窗口。在这个新窗口里显示的是reference design 和Imeplemention design的原理图,可以在这个原理图中进行Debug。