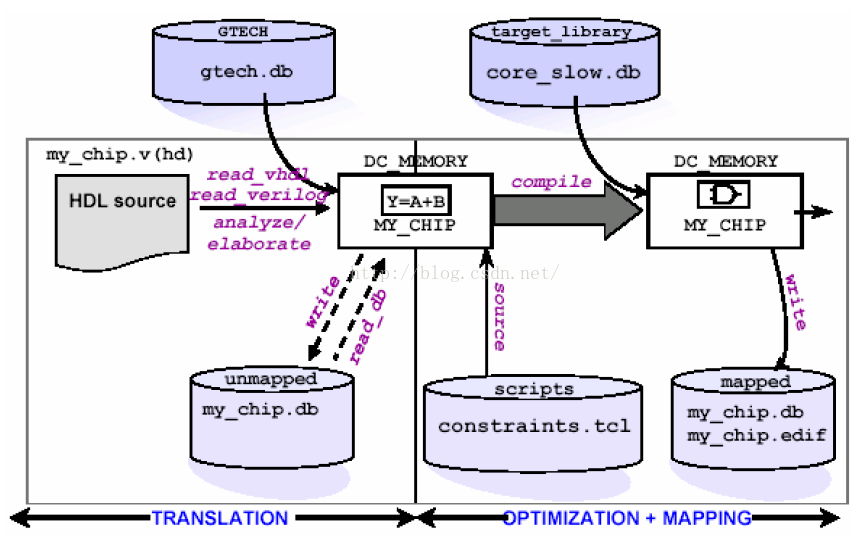

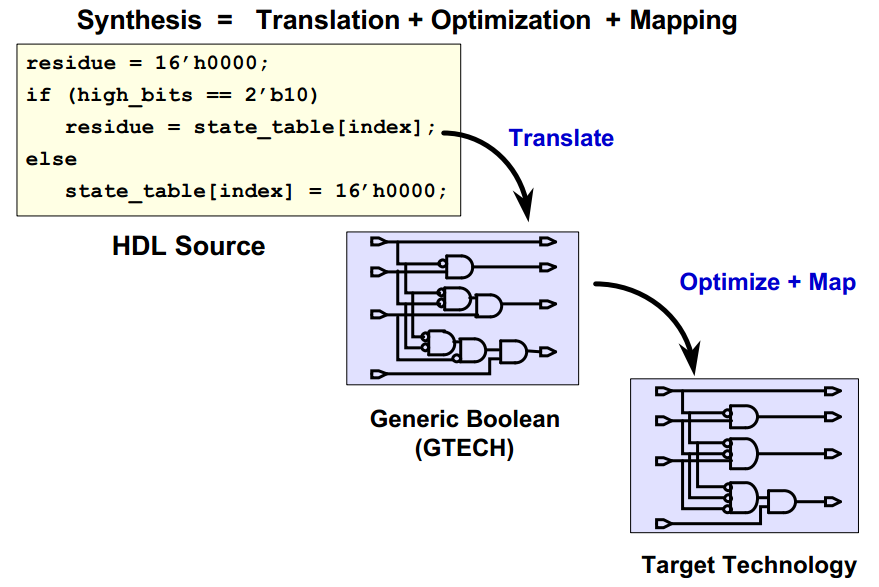

综合分为三个部分:Synthesis= Translate + Mapping + Optimization。

1、 Translate 是将 HDL转化为GTECH库元件组成的逻辑电路,这步通过read_verilog进行(verilog代码),verilog代码被读入后,将会被自动translate。GTECH是独立于工艺库的通用元件库。这个时候可以用write -output ./unmapped/design.db输出unmapped的二进制文件。

2、 Mapping 是将GTECH映射到某一指定的工艺库,此网表包含了工艺参数。

3、 Optimization 是将网表按设计者的约束进行优化。

后两步通过加约束后使用compile命令完成。完成optimization之后可以通过

write -format verilog -hierarchy -output./p_syn_sim/design.v

写成verilog格式的网表,这是map后的结果。如果输出的是顶层模块,所有模块的module都会输出到同一个文件中。顶层模块一般在最后。

1 what is synthesis?

综合是将一种思想转化为一种可制造的设备,以实现一种预期的功能。

2 level of abstraction

3 synthesis in this workshop

4 library

Sysnopsys提供了一个例子,在下面的位置:

$synopsys/doc/syn/guidelines

首先,可以在.synopsys_dc.setup里面设置库的位置和一些环境变量。里面包括所使用库的位置,DC涉及到几个库文件:

1、 工艺库(target_library):工艺库是综合后电路网表要最终映射到的库,读入的HDL代码首先由synopsys自带的GTECH库转换成Design Compiler内部交换的格式,然后经过映射到工艺库和优化生成门级网表。工艺库是由Foundary提供的,一般是.db的格式。这种格式是DC认识的一种内部文件格式,不能由文本方式打开。.db格式可以由文本格式的.lib转化过来,他们包含的信息是一致的。

2、 链接库(link_library):link_library设置模块或者单元电路的引用,对于所有DC可能用到的库,我们都需要在link_library中指定,其中也包括要用到的IP。此处还要将search_path加进来,这样才能找到.db文件,否则只会搜索当前目录。

3、 符号库 (symbol_library):symbol_library是定义了单元电路显示的Schematic的库。用户如果想启动design_analyzer或design_vision来查看、分析电路时需要设置symbol_library。符号库的后缀是.sdb,加入没有设置,DC会用默认的符号库取代。

4、 综合库(synthetic_library):在初始化DC的时候,不需要设置标准的DesignWare库standard.sldb用于实现Verilog描述的运算符,对于扩展的DesignWare,需要在synthetic_library中设置,同时需要在link_library中设置相应的库以使得在链接的时候DC可以搜索到相应运算符的实现。

5 the steps of synthesis

综合策略:

Top-down 方式的层次化编译策略有这样三个步骤:

1. 读入整个设计。

2. 处理多次引用的模块;基于设计要求在顶层加约束条件以及定义属性。

3. 编译。

Bottom-up有下面七个步骤:

1. 独立编译子模块,用估计的驱动和负载。用一个缺省的脚本文件来估计驱动和负载。

2. 将整个编译好的设计读入。

3. 对一个子模块用characterize命令来获得端口信息。

4. 用write_script来将这些传递过来的信息保存下来。

5. 清除内存,将前面得到传递信息的子模块调入并且用保存下来的脚本文件重新编译。为了这些描述信息能够应用,需要将db格式的文件读入。

6. 将这个新编译的子模块和其余的子模块全部再次调入DC。

7. 选择另外一个子模块,重复3~7步,直到所有的子模块都重新编译过了。