基于学习和总结一下

cortex-m3支持的thumb-2指令集;

1 指令格式

本文介绍的主要是ARM汇编器的基本语法,这与GCC汇编器的语法有所不同,整体编译的流程如下所示;

2 汇编基础

一般汇编语言的整体语言如下所示;

指令 操作数1, 操作数2, ... ;注释

...表示后面还可以有多个操作数;

例如:

MOV R0, #123 ;给将立即数移入到R0寄存器

需要注意的地方:

- 指令前需要加一个空格;

- 操作数中间使用

,隔开; - 注释之前可以加

;

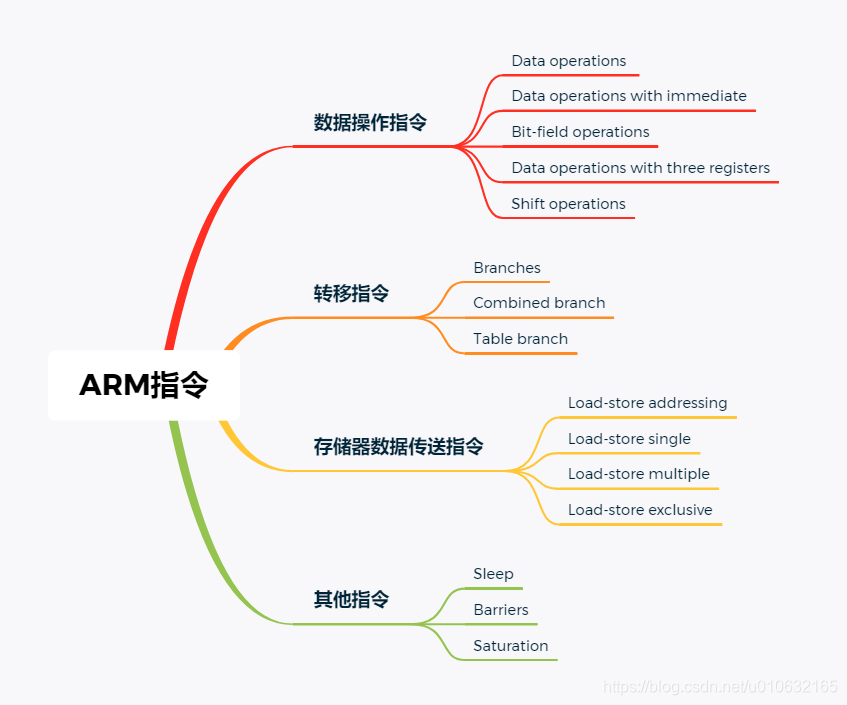

3 指令汇总

| 指令类型 | 指令宽度 | 指令 |

|---|---|---|

Data operations |

16 | ADC, ADD, AND, ASR, BIC, CMN, CMP, CPY, EOR, LSL, LSR, MOV, MUL, MVN,NEG, ORR, ROR, SBC, SUB, TST, REV, REVH, REVSH, SXTB, SXTH, UXTB, and UXTH. |

Branches |

16 | B, B, BL, BX, and BLX. Note, no BLX with immediate. |

Load-store single |

16 | LDR, LDRB, LDRH, LDRSB, LDRSH, STR, STRB, STRH. |

Load-store multiple |

16 | LDMIA, POP, PUSH, and STMIA. |

Exception generating |

16 | BKPT stops in debug if debug enabled, fault if debug disabled. SVC faults to the SVCall handler. |

Data operations with immediate |

32 | ADC{S}. ADD{S}, CMN, RSB{S}, SBC{S}, SUB{S}, CMP, AND{S}, TST, BIC{S}, EOR{S}, TEQ, ORR{S}, MOV{S}, ORN{S}, and MVN{S}. |

Data operations with large immediate |

32 | MOVW, MOVT, ADDW, and SUBW. MOVW and MOVT have a 16-bit immediate. This means they can replace literal loads from memory. ADDW and SUBW have a 12-bit immediate. This means they can replace many from memory literal loads. |

Bit-field operations |

32 | BFI, BFC, UBFX, and SBFX. These are bitwise operations enabling control of position and size in bits. These both support C/C++ bit fields, in structs, in addition to many compare and some AND/OR assignment expressions. |

Data operations with three registers |

32 | ADC{S}. ADD{S}, CMN, RSB{S}, SBC{S}, SUB{S}, CMP, AND{S}, TST, BIC{S},EOR{S}, TEQ, ORR{S}, MOV{S}, ORN{S}, and MVN{S}. No PKxxx instructions. |

Shift operations |

32 | ASR{S}, LSL{S}, LSR{S}, RRX {S}, and ROR {S}. |

Miscellaneous |

32 | REV, REVH, REVSH, RBIT, CLZ, SXTB, SXTH, UXTB, and UXTH.Extension instructions same as corresponding v6 16-bit instructions. |

Table branch |

32 | TBB and TBH table branches for switch/case use. These are LDR with shifts and then branch. |

Multiply |

32 | MUL, MLA, and MLS. |

Multiply with 64-bit result |

32 | UMULL, SMULL, UMLAL, and SMLAL |

Load-store single |

32 | LDR, LDRB, LDRSB, LDRH, LDRSH, STR, STRB, STRH, and T variants. PLD and PLI are both hints and so act as a NOP. |

Load-store multiple |

32 | STM, LDM, LDRD, and STRD. |

Load-store exclusive |

32 | LDREX, STREX, LDREXB, LDREXH, STREXB, STREXH, CLREX. Fault if no local monitor. This is IMP DEF. LDREXD and STREXD are not included in this profile. |

Branches |

32 | B, BL, and B. No BLX (1) because always changes state. No BXJ. |

System |

32 | MSR(2) and MRS(2) replace MSR/MRS but also do more. These access the other stacks and also the status registers. CPSIE/CPSID 32-bit forms are not supported. No RFE or SRS. |

System |

16 | CPSIE and CPSID are quick versions of MSR(2) instructions and use the standard Thumb-2 encodings, but only permit use of i and f and not a. |

Extended32 |

32 | NOP (all forms), Coprocessor (MCR, MCR2, MCRR, MRC, MRC2, and MRRC), and YIELD (hinted NOP). Note, no MRS(1), MSR(1), or SUBS (PC return link). |

Combined branch |

16 | CBZ and CBNZ (Compare and Branch if register is Zero or Non-Zero). |

Extended |

16 | IT and NOP. This includes YIELD. |

Divide |

32 | SDIV and UDIV. 32/32 divides both signed and unsigned with 32-bit quotient result, no remainder, it can be derived by subtraction. Early out is permitted. |

Sleep |

16,32 | WFI, WFE, and SEV are in the class of hinted NOP instructions that control sleep behavior. |

Barriers |

32 | ISB, DSB, and DMB are barrier instructions that ensure certain actions have taken place before the next instruction is executed. |

Saturation |

32 | SSAT and USAT perform saturation on a register. They perform the following: Normalize the value using shift test for overflow from a selected bit position, the Q value. Set the xPSR Q bit if so, saturate the value if overflow detected. Saturation refers to the largest unsigned value or the largest/smallest signed value for the size selected. |

4 总结

本文简单汇总了一下ARM汇编器的thumb-2指令集,列举了可能会出现的指令,以及指令的分类。