1、CPU=运算器+控制器,对应图灵机的“读写头”,但是图灵机的读写头可以自动取纸带上数据、做运算、存结果。而冯氏结构中进行改进,就是读程序、翻译程序、执行程序。其中读程序和执行程序对应于“自动”;执行程序对应于取数据、做运算、存结果。

2、CPU可抽象成:功能寄存器+运算单元

3、功能寄存器:指令寄存器、程序计数器(下一个指令)、其他功能寄存器

4、运算单元:算术运算、逻辑运算

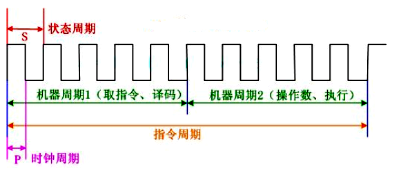

5、机器指令周期/机器周期T:取指令-翻译指令-执行指令的一个周期所花费的时间,即执行一条指令所需要的时间。

6、主频F:每秒钟能完成多少的机器周期数F=1/T。

7、时钟周期/震荡周期/节拍周期:为时钟晶振频率的倒数,即时钟晶振的周期。是计算机中最小的时间单位

8、指令周期:取出并完成一条指令所需要的时间,由若干个机器周期组成,分为单周期指令、双周期指令、多周期指令(如转移、乘法)。

9、状态周期:状态周期是CPU从一个状态转换到另一状态所需要的时间。简单地说每个状态周期分为两个震荡周期(时钟周期)

10、机器周期一般包括6个状态周期,12个时钟周期。如c51。

11、

12、机器语言与机器指令:

a、机器指令:被编程二进制码,存储在存储器中的一条条指令

b、机器语言:由机器指令构成,指挥机器工作的程序语言

指令集:一台机器指令的总集合

13、指令类型:

a、算数/逻辑运算类(基本运算):算术运算和逻辑操作

b、数据传输类(不做任何运算):将数据从一个地方复制到里另一个地方

c、程序控制类(用运算结果修改程序计数器):控制程序执行顺序

这里体现了计算机只会做“取数据、做算术/逻辑运算、存中间运算结果”

14、RISC与CISC

a、RISC:精简指令集计算机,包含最少的指令集,电路简单,速度快,如ARM是一种32位的精简指令集,去除某些不常用的指令而采用软件函数的方式解决(如乘法,用一个函数实现)。

b、CISC:复杂指令集计算机,包含多功能、复杂指令集,程序效率高。

c、STC是8位的单片机,核是51属于CISC指令集。同样的X86属于CISC指令集

d、计算机指令集与计算机能力:在基本指令之外,加入额外的指令,不会改变计算机的能力(逻辑能力,能干什么),但可能影响计算机的复杂程度和性能。是不是和我们设计一个界面中按钮多少一样?

e、计算机的差别在CPU,即运算器和控制器上

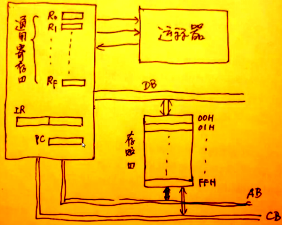

15、一个8bit模型计算机(老师自己设计的):

a、系统结构:

①、16个通用寄存器:地址:0,1,2,…,F(8bit)

②、两个特殊功能寄存器:PC(8bit)、IR(16bit)

③、256个存储单元:地址:00,01,02,…,FF(8bit)

b、指令集:有12条指令,每条16bit

16、程序的执行:

a、控制程序执行的两个特殊功能寄存器:

①、程序计数器PC:存放下一条机器指令的地址

②、指令寄存器IR:存放正在执行的机器指令

b、指令周期:

①、取指:按PC的地址取一条指令(两个单元)->IR,同时,PC<-PC+2(两个单元要+2)

②、解码:控制器翻译IR中机器指令含义

③、执行:执行IR中指令所指的动作

17、计算机语言:告诉计算机做事的一种形式化表达规范,按抽象级分类是:

a、二进制码的机器语言

b、助记符的汇编语言

c、过程包装后的C语言、BASIC、PASCAL

d、行为包装后的面向对象C++、JAVA、PYTHON

18、计算机程序:按照语言规范,告诉计算机做事

19、二进制数与数字电路:

a、门电路:可以完成二进制数的算数和逻辑运算(组合电路)

b、触发器电路:可以完成二进制数的存储(时序电路)

20、数与编码:定义数与一个集合之间的映射关系

a、十进制:正数负数浮点数

b、二进制:原码、反码、补码

c、其他:格雷码、海明码

d、注意:编码转换、运算方法、编码特点、字长、数据表示范围、截断问题、溢出问题

21、文本的二进制:ASCII(8bit)与utf-8(16bit)

22、图像的二进制:位图文件(.BMP)中,图像被看成像素点的集合,每一个像素点被看成RGB的组合

23、图像、视频压缩文件(JPG、GIF、MP4)数量达,不利于存储与传输,通过无损或有损压缩(根据数据特征、视觉效果、运动特点)保存。

24、声音的二进制:离散采样得到数据化的波形,只要离散的间隔足够小,就可以拟合出十分近似的波形。

25、总线:

a、计算机总线:各功能部件间用于传输数据的公共通信干线(功能部件:如CPU内部寄存器、各种存储器、各类输入/输出)

b、总线标准:定义并达成一致的总线,包括物理、电气等方面定义

c、经典计算机总线:ISA(16位,5MB/S,16MB空间)

d、总线主要性能:

①、数据宽度

②、寻找空间

③、时钟速度

④、数据传输率

e、提高总线的宽度可以提高计算机性能,相当于一次传输多了,但是会对寄存器有较高的要求,以及对数据协议有要求,出错的可能性更大

f、分时(把总线频率提高)可以提高性能,相当于速度变快了,但是分时是有上限的,这是因为波的性质决定的,即频率不可与电信号的传输速率相接近

g、总线包括:

①、DB数据总线(传输数据)

②、AB地址总线(传输源和目标单元地址)

③、CB控制总线(源与目标传输方式、状态、访问时序控制)

h、OC集电极开路输出方式:采用上拉电阻,与逻辑(输出低电平时阻抗低),总线速度与上拉电阻值成反比,速度受限,但硬件容错安全。只要没有一个传低电平则恒为高电平。

i、三态门输出方式:输出受“输出使能OE”信号控制,输出信号低阻抗,总线速度高,但硬件容错差。

j、总线冲突:两个或两个以上源同时输出时,总线数据发生冲突。

嵌入式(十五):机器周期&指令周期&状态周期&时钟周期&指令&总线

猜你喜欢

转载自blog.csdn.net/qq_40851744/article/details/106426430

今日推荐

周排行