数据传送类指令

常用的有以下几个:

MOV MOVC MOVX

XCH XCHD SWAP

PUSH POP

1.内部 RAM 的数据传送指令

这类指令的源操作数和目的操作数地址都在单片机内部,它可以是片内 RAM 的地址,也可以用特殊功能寄存器 SFR 的符号。按照寻址方式来分,内部 RAM 的数据传送指令可以分为立即型、直接型、寄存器型和寄存器间址型等 4 类。

//(1)立即型传送指令(共 5 条)

//这类指令的源操作数是立即数。

MOV A , #data ;(A) ← data

MOV Rn ,#data ;(Rn) ← data

MOV @Ri,#data ;((Ri)) ← data

MOV direct,#data ;(direct) ← data

MOV DPTR,#data16 ;(DPTR) ← data16

//(2)直接型传送指令(共 5 条)

//直接型传送指令中不论是源操作数还是目的操作数,其中至少有一个是直接地址。

MOV A ,direct ;(A) ← (direct)

MOV direct ,A ;(direct) ← (A)

MOV Rn,direct ;(Rn) ← (direct)

MOV @Ri,direct ;((Ri)) ← (direct)

MOV direct2,direct1 ;(direct2) ← (direct1)

//(3)寄存器寻址型传送指令(共 3 条)

MOV A , Rn ;A ← (Rn)

MOV Rn , A ;Rn ← (A)

MOV direct , Rn ;direct ← (Rn)

//(4)寄存器间址型传送指令(共 3 条)

MOV A ,@Ri ;(A) ← ((Ri))

MOV @Ri ,A ;((Ri)) ← (A)

MOV direct ,@Ri ;(direct) ← ((Ri))

2.片外 RAM 的数据传送指令

对片外 RAM 单元只能使用寄存器间接寻址的方法实现与累加器 A 之间的数据传送。片外 RAM 数据传送指令有 4 条。

MOVX A ,@DPTR ;(A) ← ((DPTR))

MOVX @DPTR ,A ;((DPTR)) ← (A)

MOVX A ,@Ri ;(A) ← ((Ri))

MOVX @Ri , A ;(Ri)) ← (A)

这里需要注意:

(1)上述 4 条指令采用了不同的间址寄存器,前两条采用 DPTR 作间址寄存器,因DPTR 为 16 位地址指针,所以这两条指令可以寻址外部 RAM 的整个 64KB 空间。DPTR 所包含的 16 位地址信息由 P0 口传送低 8 位地址信息,P2 口传送高 8 位地址信息,该 16 地址所寻址的片外 RAM 单元的数据经过 P0 口输入到累加器 A,P0 口作分时复用的总线。后两条采用 R0,R1 作 8 位地址指针,寻址范围只限于片外 RAM 的低于 256 个单元。此时 P2 口仍可以用作通用 I/O 口。

(2)片外 RAM 数据传送指令的助记符采用 MOVX,与片内 RAM 数据传送指令 MOV不一样。MCS-51 对片内 RAM 和片外 RAM 独立编址,因而采用不同的指令访问。

(3)片外 RAM 单元只能与累加器 A 之间进行数据传送,当片外 RAM 数据读入累加器时,P3.7 引脚上输出 RD 读选通信号。当累加器 A 数据传送至片外 RAM 时,P3.6 引脚上输出 WR 写选通信号。

(4)MCS-51 系统中没有设置访问外设的 I/O 指令,且片外扩展的 I/O 端口与片外 RAM是统一编址的,因此对片外 I/O 端口的访问也使用此 4 条指令。

3.程序存储器 ROM 取数据指令

这组指令只有两条,完成从程序存储器 ROM 中读入数据,传送至累加器 A。这两条指令常用于查表操作,故又称之为查表指令。

MOVC A , @A+DPTR ;(A) ← ((A)+(DPTR))

MOVC A , @A+PC ;(A) ← ((A)+(PC))

(1)这两条指令都是一字节指令,采用了基址寄存器加变址寄存器间接寻址方式。

(2)对于第 1 条指令,由于采用 16 位 DPTR 作基址寄存器,DPTR 可任意赋值。因此这条指令的寻址范围是整个 ROM 的 64KB 空间。对于第 2 条指令,采用程序计数器 PC 作为基址寄存器,因此,只能读出以当前 MOVC 指令为起始的 256 个地址单元之内的某一单元。

(3)查表时,对于 MOVC A,@A+DPTR 指令,首先要将查表的第 n 项数据作为偏移量送累加器 A;然后将表首地址送 DPTR;最后执行该指令即可。

对于 MOVC A,@A+PC 指令,首先将表中的 n 项作为变址值送累加器 A;然后将查表指令的下一条指令地址与表首地址之差和 A 中的内容相加作为偏移量;最后执行该指令即可。

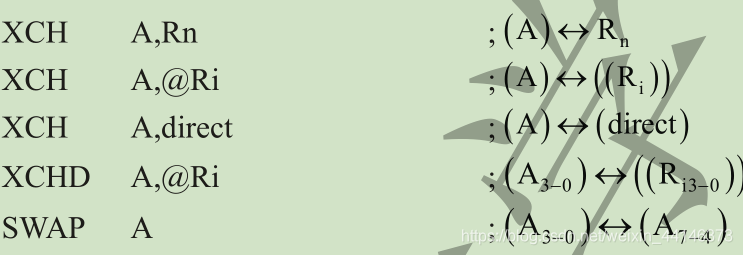

4.数据交换指令

数据交换指令共有 5 条,完成累加器 A 和内部 RAM 单元之间的字节或半字节交换。

(1)这组指令的前 3 条为全字节交换指令,其功能是将 A 的内容与源操作数所指出的单

元中的数据互相交换。

(2)第 4 条指令是半字节交换指令,将 A 内容的低 4 位与 Ri 所指示的片内 RAM 单元中内容的低 4 位数据互相交换,各自的高 4 位不变。

(3)SWAP A 指令是将 A 中内容的高、低 4 位数据互相交换。

5.堆栈操作指令

堆栈操作指令共 2 条,所以是压栈指令和弹出指令:

PUSH direct ;(SP) ← (SP)+1 , ((SP)) ← (direct)

POP direct ;(direct) ← ((SP)),(SP) ← (SP)-1

(1)PUSH 指令的功能是先将堆栈指针 SP 的内容加 1,然后将直接寻址单元中的数压入到 SP 所指示的单元中去。

(2)POP 指令的功能是先将堆栈指针 SP 所指示的单元的内容弹出传送到直接寻址之中去,然后将 SP 的内容减 1,仍指向栈顶。

(3)使用堆栈时,一般需重新设定 SP 的初始值。系统上电或复位时,SP 的初始值为07H,而 07H~1FH 正好是 CPU 工作寄存器区,程序中需要使用堆栈时,先应给 SP 设置另一初始值。一般 SP 的值可设在 1FH 或再大一些的片内 RAM 单元中,但应注意不要超出堆栈的深度。

算术运算类指令

MCS-51 的算术运算指令共有 24 条,8 种助记符,包括了加、减、乘、除等各种运算。全部指令都是 8 位数运算。算术运算类指令用到的助记符为:ADD、ADDC、SUBB、INC、DEC、DA、MUL 和 DIV 8 种。

1.加法指令

加法指令共有 4 条,其被加数都是累加器 A,相加结果也存放在累加器 A 中。

ADD A ,Rn ;(A) ← (A)+(Rn)

ADD A ,direct ;(A) ← (A)+(direct)

ADD A ,@Ri ;(A) ← (A)+((Ri))

ADD A ,#data ;(A) ← (A)+data

这 4 条指令使得累加器 A 可以和内部 RAM 的任何一个单元内容进行相加,也可以和一个 8 位立即数相加,相加的结果存放在 A 中,无论是哪一条加法指令,参加运算的都是两个8 位二进制数。对使用者而言,这些 8 位二进制数可以当作无符号数(0~255),也可以当作带符号数,即补码形式(-128~+127)。例对一个二进制数11010011,用户可将它认为是无符号数 211(10),也可以认为是带符号数(-45(10)。

单片机在做加法运算时,按以下规则进行:

(1)两数相加后位 7 有进位输出,则程序状态寄存器 PSW 中进位标志位 CY 置 1,否则清零。

(2)两数相加后位 3 向位 4 有进位输出,则 PSW 中辅助进位标志位(半进位标志位)AC 置 1,否则清零。

(3)两数相加后,如果位 7 有进位输出而位 6 没有,或者位 6 有进位输出而位 7 没有,

则 PSW 中溢出标志位 OV 置 1,否则清零。溢出的表达式 OV=D6CYμ ⊕ D7CY;D6CY 为位

6 向位 7 的进位,D7CY 为位 7 向 CY 的进位。

(4)两数相加后,累加器 A 中有奇数个 1,则 PSW 中奇偶校验标志位 P 置 1,否则清零。

(5)两数相加时,操作数直接相加,无须任何变换。

即相加后的和为 10 111 011,存入 A 累加器,(A)=10 111 011,若认为是无符号数相加,则 (A)=(187)(10),若认为是带符号数相加,则 (A)=(-69)(10)。但带符号数相加的结果只有当PSW 中溢出标志位 OV=0 时,结果才是正确的。

2.带进位加法指令

带进位加法指令也共有 4 条,其被加数都是累加器 A,相加结果也要存放在累加器 A 中。

ADDC A , Rn ;(A) ← (A)+(Rn)+(CY)

ADDC A , direct ;(A) ← (A)+(direct)+(CY)

ADDC A , @Ri ;(A) ← (A)+((Ri))+(CY)

ADDC A , #data ;(A) ← (A)+data+(CY)

带进位的 4 条加法指令的操作,除了指令中所规定的两个操作数相加之外,还要加上进位标志位 CY 的值。这里所指的 CY 的值是指令开始执行前的进位标志值,而不是相加过程中产生的进位标志值。运算结果对 PSW 中相关位的影响和上述的 4 条不带进位的加法指令相同。带进位加法指令主要用于多字节二进制数的加法运算中。

3.加 1 指令

加 1 指令共 5 条,是对指定单元的内容加 1 的操作。

INC A ;(A) ← (A)+1

INC Rn ;(Rn) ← (Rn)+1

INC direct ;(direct) ← (direct)+1

INC @Ri ;(Ri) ← ((Ri))+1

INC DPTR ;(DPTR) ← (DPTR)+1

加 1 指令又称为增量(Increase)指令。前 4 条指令是对一字节单元的内容加 1,最后一条指令是给 16 位 DPTR 寄存器内容加 1。第一条指令的操作将影响 PSW 中奇偶标志位 P,其余 4 条指令均不影响各标志位。

4.减法指令

带借位的减法指令有 4 条,与带进位加法指令类似,其被减数和结果都存放在累加器A 中。

SUBB A , Rn ;A ← (A)-(Rn)-(CY)

SUBB A , direct ;A ← (A)-(direct)-(CY)

SUBB A , #data ;A ← (A)-data-(CY)

SUBB A , @Ri ;A ← A-((Ri))-CY

带借位的减法指令是累加器 A 中的操作数减去源地址所指示的操作数和指令执行前的CY 值,并把结果保留在累加器 A 中。单片机在做减法运算时按以下规则进行。

(1)两数相减,若位 7 在减法时有借位,则 CY 置 1,否则 CY 为 0。

(2)两数相减,若位 3 向位 4 有借位,则 PSW 中 AC 置 1,否则 AC 为 0。

(3)两数相减,若位 7 有借位而位 6 无借位,或者位 7 无借位而位 6 有借位,则 PSW中 OV 置 1,否则清零。

(4)两数相减,若结果 A 中有奇数个 1,则 PSW 中 P 置 1,否则 P 为 0。

(5)两数相减,操作数直接相减,并取得借位 CY 的值。同样可以把减法运算看作是无符号数(0~255)相减,也可以看作是带符号数(补码形式 -128~+127)的相减,但带符号数相减的结果只有当溢出标出 OV=0 时才能保证结果是正确的。

(6)减法指令只有一组带借位的减法指令,而没有不带借位的减法指令。需要时可在减法之前先用指令使 CY=0,然后再相减。

5.减 1 指令

减 1 指令共有 4 条,完成对指定单元内容减 1 的操作。

DEC A ;(A) ← (A)-1

DEC Rn ;(Rn) ← (Rn)-1

DEC direct ;(direct) ← (direct)-1

DEC @Ri ;((Ri)) ← ((Ri))-1

与加 1 指令一样,减 1 指令不影响程序状态字 PSW 各位的状态,但累加器 A 减 1 可以影响奇偶检验 P 标志。

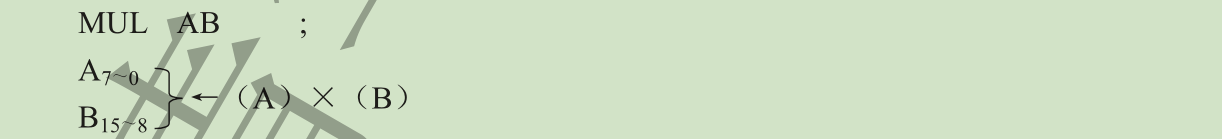

6.乘法指令

乘法指令只有 1 条,完成 2 个 8 位无符号整数的乘法。乘法指令是一字节指令,但执行时需 4 个机器周期。

参加乘法运算的两个操作数分别存放在累加器 A 和寄存器 B 中,两个 8 位无符号数相乘结果为 16 位无符号数,它的高 8 位存放于寄存器 B 中,而它的低 8 位存放在累加器 A 中。指令执行后将对 PSW 中 CY,OV 和 P 3 个标志产生影响:CY 一定被清除,CY=0;P 仍由累加器 A 中 1 的奇偶性确定;OV 标志用来表示积的大小,若相乘后有效积为 8 位,则 B 中高 8 位。积为 0,此时 OV=0,若相乘后积超过 255,此时积的高 8 位存放在寄存器 B 中,此时 OV=1。

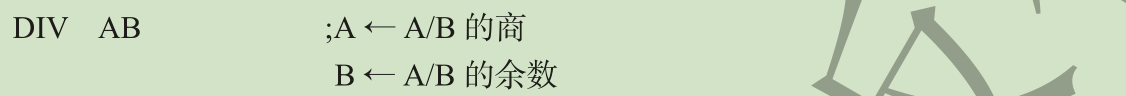

7.除法指令

除法指令也只有 1 条,也是一字节指令,执行时需 4 个机器周期。

参加除法运算的两个操作数也是无符号数,被除数置于累加器 A 中,除数置于寄存器 B中。相除之后,商数存放在累加器 A 中,余数存放在寄存器 B 中。除法指令也影响 PSW 中CY,OV 和 P 标志。相除之后 CY 一定为 0,溢出标志 OV 也为 0,只有当除数为 0 时,A和 B 中的内容为不确定值,此时 OV=1,说明除法溢出,无意义,奇偶标志 P 仍按一般规则确定。

8.十进制调整指令

在计算机中十进制数字 0~9 一般可用压缩型 BCD 码表示,但两个压缩型的 BCD 码按二进制规则相加运算后,必须经十进制调整指令调整后,才能得到压缩型 BCD 码的和的正确值。十进制调整指令只有一条。

DA A ; 若 (AC)=1 或 (A 3-0 ) > 9,则 (A) ←(A)+ 06H

//若 (CY)=1 或 (A 7-4 )>9,则 (A) ← (A)+60H。

将两个压缩型 BCD 码按二进制运算规则相加和存放于累加器 A 中,本指令即跟在 ADD或 ADDC 指令后,将相加后存放在累加器 A 中的结果进行十进制调整,才能正确完成十进制加法运算功能。该指令的操作规则为:

若累加器 A 中的低 4 位数值大于 9 或者第 3 位向第 4 位产生进位(即辅助进位标志AC=1),则需将 A 中低 4 位内容加 6 以作调整,产生低 4 位正确的 BCD 码。

若累加器 A 中的高 4 位数值大于 9 或进位 CY=1,则高 4 位需加 6 以作调整,产生高 4位正确的 BCD 码。

执行 DA A 指令后,CPU 根据累加器 A 的原始数值和 PSW 的状态,由硬件自动对累加器 A 进行加 06H、60H 或 66H 的操作。

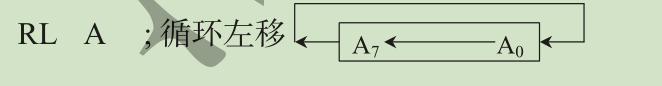

逻辑运算类指令

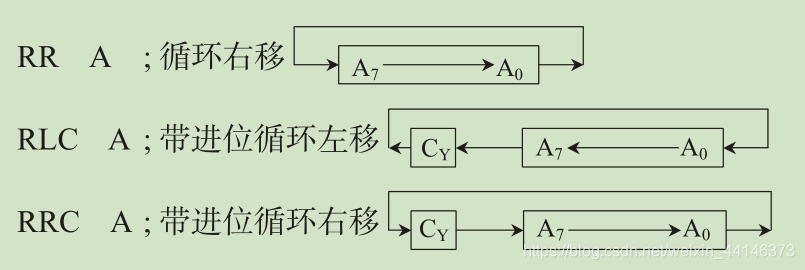

MCS-51 共有 24 条逻辑运算类指令,完成与、或、异或、取反以及移位等操作,逻辑运算都是按位进行的。这些指令执行时一般不影响程序状态寄存器 PSW 中各位状态,仅当目的操作数为 A 时,会对奇偶标志位 P 有影响,带进位的移位指令也会影响 CY 位。逻辑运算类指令用到的 9 种助记符为 ANL、ORL、XRL、RL、RLC、RR、RRC、CLR 和 CPL。

1.逻辑“与”运算

逻辑“与”指令共有 6 条:

ANL A,Rn ;(A) ← (A) ∧ (Rn)

ANL A,direct ;(A) ← (A) ∧ (direct)

ANL A,@Ri ;(A) ← (A) ∧ ((Ri))

ANL A,#data ;(A) ← (A) ∧ data

ANL direct,A ;(direct) ← (direct) ∧ (A)

ANL direct,#data ;(direct) ← (direct) ∧ data

前 4 条指令以累加器 A 为目的操作数,后两条以直接地址单元为目的操作数,这样可对内部 RAM 的任一单元及各个特殊功能寄存器 SFR 内容按需进行变换。如将某一个字节中某几个变为 0,而其余位不变。

2.逻辑“或”运算

共有 6 条逻辑“或”运算指令:

ORL A,Rn ;(A) ← (A) ∨ (Rn)

ORL A,direct ;(A) ← (A) ∨ (direct)

ORL A,@Ri ;(A) ← (A) ∨ ((Ri))

ORL A,#data ;(A) ← (A) ∨ data

ORL direct,A ;(direct) ← (direct) ∨ (A)

ORL direct,#data ;(direct) ← (direct) ∨ (data)

与、或运算结合在一起,将更便于对 RAM 单元,特别是对 SFR 内容进行变换。

3.逻辑“异或”运算

有 6 条“异或”指令

XRL A,Rn ;(A) ← (A) ⊕ (Rn)

XRL A,direct ;(A) ← (A) ⊕ (direct)

XRL A,@Ri ;(A) ← (A) ⊕ ((Ri))

XRL A,#data ;(A) ← (A) ⊕ data

XRL direct,A ;(direct) ← (direct) ⊕ (A)

XRL direct,#data ;(direct) ← (direct) ⊕ data

4.累加器清零和取反指令

//累加器清零和取反指令 2 条:

CLR A ;(A) ← 0

CPL A ; ( A) <-A非

这两种指令都是单字节单周期指令,比用数据传送或者异或指令对累加器 A 清零或取反更为快捷、直观。

5.移位指令

控制转移类指令

MCS-51 指令系统的控制转移类指令共有 17 条,主要功能是控制程序转移到新的 PC 地址上。这类指令用到的助记符有 10 种:ACALL、AJMP、LCALL、LJMP、SJMP、JMP、JZ、

JNZ、CJNE 和 DJNZ。

1.无条件转移指令

这类指令是当程序执行到该指令时,无条件转移到该指令所提供的地址,指令执行后均不影响标志位。

(1)长转移指令

LJMP addr16 ;(PC) ← addr16

这条指令把 16 位地址传送给程序计数器 PC,实现程序的无条件的转移。因为操作码提供了 16 位地址,所以可在 64K 字节程序存储器范围内跳转。该指令为 3 字节指令,第二、三字节地址码分别装入 PC 的高 8 位和低 8 位。

(2)绝对转移指令

AJMP addr11 ;(PC) ← (PC)+2, (PC10~0) ← addr11

本指令是双字节双周期指令。执行这条指令后,先将 PC 的内容加 2,使 PC 指向本绝对转移指令的下一条指令,然后将 addr11 送入 PC 的低 11 位,PC 的高 5 位保持不变,从而形

成新的 PC 值,实现程序的转移。本指令的转移范围为与本指令下一条指令地址位于同一个2KB 页面,也即转移的目标地址高 5 位地址 PC15~PC11 是不允许发生变化的。

(3)相对转移指令(短转移指令)

SJMP rel ;(PC) ← (PC)+2, (PC) ← (PC)+rel

该指令为双字节,指令中的相对地址 rel 是一个带符号位的 8 位地址偏移量,以下一条指令第 1 字节的地址 PC+2 为基值,地址偏移量范围为 -128~+127。负数表示反向转移,正数表示正向转移。

(4)变址寻址转移指令

JMP @A+DPTR ;(PC) ← (A)+(DPTR)

该指令也是一条无条件转移指令。转移地址是以 16 位数据指针 DPTR 为基地址,以累加器 A 中内容作地址的偏移量两者进行无符号数相加,形成目标转移地址送入程序计数器PC,实现程序的分支转移。这条指令可代替众多的判别跳转指令,具有散转功能,又称之为散转指令。

通常基地址是一张转移指令表的起始地址,累加器 A 中数值为偏移量

2.条件转移指令

条件转移指令共有 8 条,它是指当某种条件满足时,转移才进行,否则程序将顺序执行。MCS-51 中的所有条件转移指令都只采用相对寻址方式来指示转移的目的地址。目的地址在以下一条指令的起始地址范围为中心的 -128~+127 共 256 个字节。

(1)累加器判零条件转移指令

JZ rel ;(A)=0, (PC) ← (PC)+2+rel

; (A) ≠ 0, (PC) ← (PC)+2

JNZ rel ; (A) ≠ 0, (PC) ← (PC)+2+rel

; (A)=0, (PC) ← (PC)+2

看A是否为0

(2)比较条件转移指令

比较条件转移指令共有 4 条,它们的功能是把两个操作数相比较,若两者不相等则转移,否则按顺序执行。

CJNE A,#data,rel ;(PC) ← (PC)+3

若 (A)> data, 则 (PC) ← (PC)+rel, 且 (CY) ← 0;

若 (A)< data, 则 (PC) ← (PC)+rel, 且 (CY) ← 1;

若 (A)= data, 则顺序执行程序 , 且 (CY) ← 0。

CJNE A,direct, rel ;(PC) ← (PC)+3

若 (A)>(direct), 则 (PC) ← (PC)+rel, 且 (CY) ← 0;

若 (A)<(direct), 则 (PC) ← (PC)+rel, 且 (CY) ← 1;

若 (A)=(direct), 则顺序执行程序 , 且 (CY) ← 0。

CJNE Rn,#data,rel ;(PC) ← (PC)+3

若 (Rn)>data, 则 (PC) ← (PC)+rel, 且 (CY) ← 0;

若 (Rn)<data, 则 (PC) ← (PC)+rel, 且 (CY) ← 1;

若 (Rn)=data, 则顺序执行程序 , 且 (CY) ← 0。

CJNE @Ri,#data,rel ;(PC) ← (PC)+3

若 ((Ri))>data, 则 (PC) ← (PC)+rel, 且 (CY) ← 0;

若 ((Ri))<data, 则 (PC) ← (PC)+rel, 且 (CY) ← 1;

若 ((Ri))=data, 则 (PC) ← (PC)+rel, 且 (CY) ← 0。

(3)减 1 条件转移指令

DJNZ Rn, rel ;(PC) ← (PC)+2,(Rn) ← (Rn)-1

若 (Rn) ≠ 0, 则 (PC) ← (PC)+rel;

若 (Rn)=0, 则程序向下按顺序执行。

DJNZ direct,rel ;(PC) ← (PC)+3, (direct) ← (direct)-1

若 (direct) ≠ 0, 则 (PC) ← (PC)+rel;

若 (direct)=0, 则程序向下按顺序执行。

这组指令的操作是先将源操作数减 1,并将结果送回源操作数中保存。若减 1 以后操作数不为 0,则转移到指定地址单元运行,若减 1 以后结果为 0,程序向下按顺序运行。

这组指令对构成循环程序十分有用,可以指定给任何一个工作寄存器或者内部 RAM 单元为计数器,事先对计数器赋以初值以后,就可以利用上述指令,若对计数器减 1 后不为 0就循环操作,由此构成循环程序。

3.子程序调用及返回指令

(1)子程序调用指令

① 长调用指令

LCALL addr16 ;(1)(PC) ← (PC)+3, PC 内容加 3(本指令长度)。

(2)PC 内容压入堆栈:

(SP) ← (SP)+1, ((SP)) ← (PC7~0)

(SP) ← (SP)+1, ((SP)) ← (PC15~8)

(3)PC ← addr16,将调用的 16 位子程序地址送入 PC。

LCALL 指令指示了 16 位目标地址,以调用 64KB 范围内所指定的子程序。执行该指令时,首先(PC)+ 3 送回 PC,它是下一条指令,即断点的地址。然后把这断点地址分两次压入堆栈;先压入 PC7~0 低位字节,后压入 PC15~8 高位字节。堆栈指针 SP 每次加 1,共 2 次 SP+2 指向栈顶。接着将 16 位目标地址 addr16 送入 PC,使程序转向目标地址 addr16去执行被调用的子程序。

② 绝对调用指令

本指令为双字节指令,也称之为短调用指令,提供 11 位的目标地址。

ACALL addr11 ; (1)(PC) ← (PC)+2,PC 内容加 2(本指令长度)。

(2)PC 内容压入堆栈:

(SP) ← (SP)+1, ((SP)) ← (PC7~0)

(SP) ← (SP)+1, ((SP)) ← (PC15~8)

(3)(PC10~0) ← addr11,将 11 位目标地址 addr11 送入 PC 的低11 位,而 PC15~11 位不变,形成新的目标地址。

(2)返回指令

返回指令共两条:

子程序返回指令 RET;(PC15~8) ← ((SP)), (SP) ← (SP)-1

(PC7~0) ← ((SP)), (SP) ← (SP)-1

中断返回指令 RETI;(PC15~8) ← ((SP)), (SP) ← (SP)-1

(PC7~0) ← ((SP)), (SP) ← (SP)-1

这两条指令都放在子程序或中断服务程序的最后一条,功能都是从堆栈中取出以前压入的 16 位断点地址送回 PC,从而完成了程序的返回。而 RETI 指令除此之外,还要清除中断响应时被置位的优先状态触发器,开放较低级中断和恢复中断逻辑。

4.空操作指令

NOP ;(PC) ← (PC)+1

空操作指令是单字节指令,CPU 不作任何操作,可产生一个机器周期的延时,程序设计中也可作备用。

布尔变量操作类指令

MCS-51 具有较强的布尔变量处理能力,它在硬件上设置了一个独立的位处理机(即布尔处理器),它把 PSW 中进位标志位 CY 作为位处理机相应的累加器 C。而内部 RAM 单元中可位寻址区中的各位和特殊功能寄存器 SFR 中可位寻址的寄存器中的各位是位处理机的存储空间。

位操作的指令共有 17 条,所用的助记符有 MOV、CLR、CPL、SETB、ANL、ORL、JC、JNC、JB、JNB 和 JBC 共 11 种。

1.位传送指令

位传送指令有两条:

MOV C,bit ;(CY) ← (bit)

MOV bit, C ;(bit) ← (CY)

为便于书写,指令中 CY 直接写作 C。两个可寻址位之间没有直接的传送指令,要完成这种传送,则以通过 CY 作为中间媒介来进行。

2.位置位 / 复位指令

位置位 / 复位指令共有 4 条,它对位地址所指定的各位和进位标志 CY 进行置位或复位的操作。

(1)位置位指令

SETB C ;(CY) ← 1

SETB bit ;(bit) ← 1

(2)位复位指令

CLR C ;(CY) ← 0

CLR bit ;(bit) ← 0

3.位运算指令

位的运算都是逻辑运算,有“与”“或”“非”3 种运算。进行“与”“或”运算时,以位累加器 CY 为目的操作数,位地址的内容为源操作数,逻辑运算的结果送回 CY。“非”运算对每个位地址内容取反。

位运算指令共有 6 条:

ANL C,bit ;(CY) ← (CY) ∧ (bit)

ANL C,/bit ;(CY) ← (CY) ∧ ( bit非)

ORL C,bit ;(CY) ← (CY) ∨ (bit)

ORL C,/bit ;(CY) ← (CY) ∨ (bit非)

CPL C ;(CY) ← ( CY非)

CPL bit ;(bit) ← (bit非)

4.位控制转移指令

位控制转移共 5 条,它们都是条件转移指令,它们以 CY 或位地址 bit 的内容作为转移的判断条件。

(1)以 CY 内容为条件的转移指令

JC rel ; CY=1,则 (PC) ← (PC)+2+rel

CY=0,则 (PC) ← (PC)+2

JNC rel ; CY=0,则 (PC) ← (PC)+2+rel

CY=1,则 (PC) ← (PC)+2

(2)以位地址内容为条件的转移指令

JB bit,rel ; (bit)=1,则 (PC) ← (PC)+3+ rel

(bit) =0,则 (PC) ← (PC)+3

JNB bit,rel ; (bit)=0,则 (PC) ← (PC)+3+ rel

(bit) =1,则 (PC) ← (PC)+3

JBC bit,rel ; (bit)=1,则 (PC) ← (PC)+3+ rel 且 (bit) ← 0

(bit) =0,则 (PC) ← (PC)+3

JBC 指令与 JB 指令类似,在转移条件满足时,JBC 指令还将 bit 位地址内容清零。