版权声明:本文为转载文章,遵循 CC 4.0 BY-SA 版权协议。

原文链接:https://blog.csdn.net/qq_34975667/article/details/85163545

最近,FPGA刚刚入门,写了个分频电路,点亮几个LED灯,testbench方面已经没有问题了。准备下载开发板(xilinx kc705),发现时钟输入和普通的不太一样,折腾了一段时间

xilinx kc705 时钟输入电路

这个电路是差分时钟输出,我想肯定有办法将差分信号转为单端信号,就去查阅了一下资料,

IBUFDS、IBUFGDS和OBUFDS都是差分信号缓冲器,用于不同电平接口之间的缓冲和转换。

IBUFDS 是差分输入的时候用;

OBUFDS 是差分输出的时候用;

IBUFGDS 则是时钟信号专用的输入缓冲器。

更多参考 https://blog.csdn.net/github_33678609/article/details/53789063

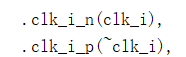

然后我就实例化一个差分信号缓冲器

并在testbench进行仿真,差分信号可以用下面方式仿真

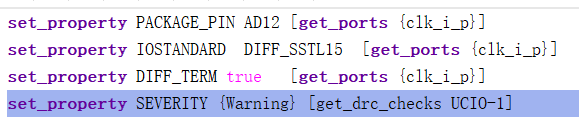

仿真是没有问题的。然后想下载到板子里跑,那么需要IO约束吧。我在xdc中添加如下指令

set_property PACKAGE_PIN AD12 [get_ports {clk_i_p}]

set_property PACKAGE_PIN AD12 [get_ports {clk_i_n}]

set_property SEVERITY {Warning} [get_drc_checks UCIO-1] //可以忽略掉drc error

实现现象告诉我,时钟并没有跑起来,我就纳闷了,差分信号已经引入到板子里了,没生效为什么?后面又查了下资料:

差分信号和普通的信号有一定差异的,差分信号的输入是成对分配的,并且I/O标准是默认LVDS模式,(注意:要是不对差分信号进行IP核的差分信号转化,I/O标准下拉框是没有LVDS模式

差分的管脚分配是成对分配的,只要分配好了一个,另一个会自动分配好,所以不用担心另一个信号怎么分配的问题

https://blog.csdn.net/houyichaochao/article/details/80566699

只有差分端口的P侧需要被约束。

该工具将约束向前传播到iBFGDS实例的输出。

如果两者都被约束,则工具将它们作为两个独立的时钟定义,并分析它们之间的时钟路径。

这可能导致不正确的要求。

类似地,只有差分数据端口的p侧需要在输入延迟和输出延迟约束中受到约束。

N侧路径的分析与P侧完全相同。

然后修改xdc,注意

要引入 IBUFGDS.I 这个信号 ,比如上图是 clk_i_p。。。若引入clk_i_n,则会失败

然后,OK 程序跑起来了嘻嘻嘻