超线程技术

Intel超线程技术(Intel HT技术)是为了在多任务环境下执行多线程操作系统和应用程序代码或单线程应用程序时提高IA-32处理器的性能而开发的。超线程技术使单个物理处理器可以使用共享的执行资源并发地执行两个或多个独立的控制流(线程)。一个线程就是一个控制流。

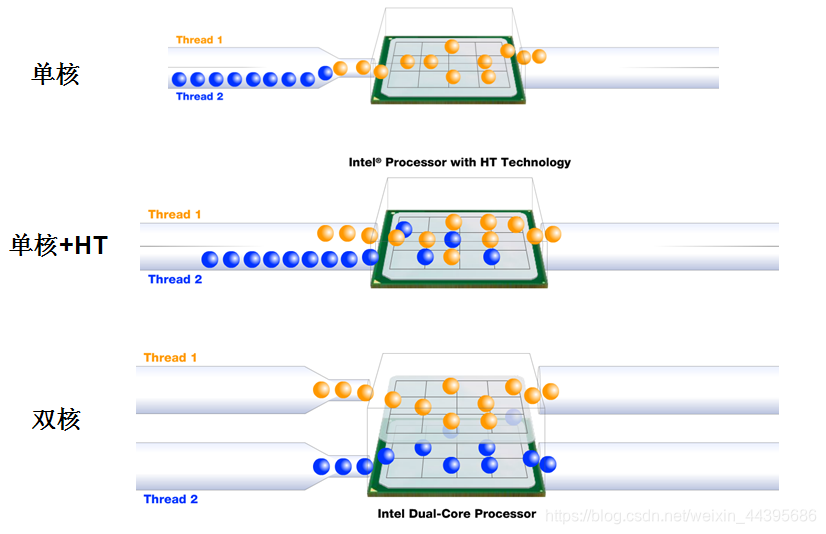

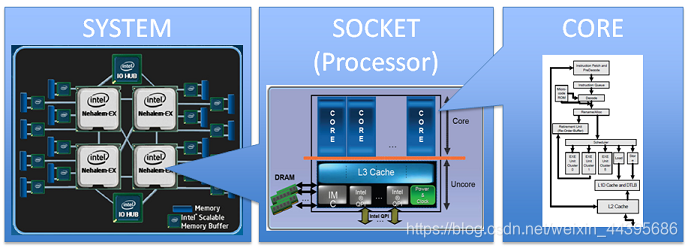

超线程技术执行多线程是并发的,而双核心(即两个物理核心core)执行多线程是并行的,如下图

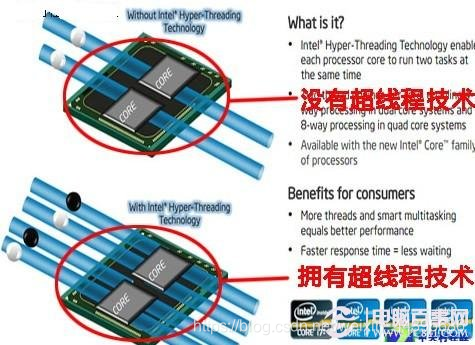

Intel HT技术是IA-32处理器家族中硬件多线程能力的一种形式。它不同于使用不同package(CPU金属壳)的多处理器功能,每个物理处理器package都与一个物理CPU插座相匹配。Intel HT技术通过使用处理器核心中的共享执行资源,通过单个物理package提供了硬件多线程功能。

在体系结构上,支持Intel HT技术的IA-32处理器由两个或多个逻辑处理器组成,每个逻辑处理器都有自己的IA-32体系结构状态( Architectural State)。每个逻辑处理器由一组完整的IA-32数据寄存器、段寄存器、控制寄存器、调试寄存器和大多数msr组成。每个都有自己的高级可编程中断控制器(APIC)

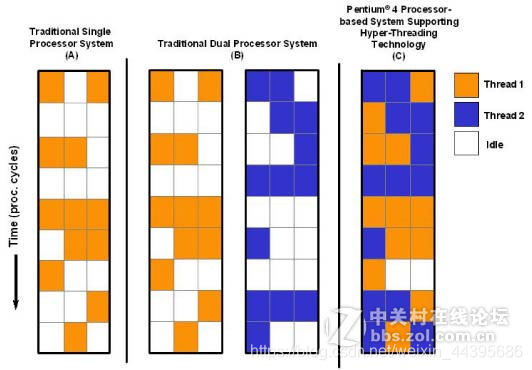

图2-5显示了支持Intel HT技术(使用两个逻辑处理器实现)和传统双处理器系统的处理器的比较。

与使用两个或多个独立物理IA-32处理器的传统MP系统配置不同,支持Intel HT技术的IA-32处理器中的逻辑处理器共享物理处理器的核心资源(AS,Architectural State)。这包括执行引擎和系统总线接口。上电和初始化后,可以独立地指示每个逻辑处理器执行、中断或停止指定的线程。

科普时间 Architectural State

Architectural State(体系结构状态)是CPU保持进程状态的部分。 这通常保存在处理器寄存器中,包括

控制寄存器

- 指令标志寄存器(例如x86中的 EFLAGS )

- 中断屏蔽寄存器

- 内存管理单元寄存器

- 状态寄存器

通用寄存器(例如x86中的 AX,BX,CX,DX等)

- 加法器寄存器

- 地址寄存器

- 计数器寄存器

- 索引寄存器

- 堆栈寄存器

- 字符串寄存器

流水线寄存器,在指令流水线的各个阶段之间

这并不包括作为ALU的实际计算单元。

英特尔®HT技术通过在单个芯片上提供两个或多个逻辑处理器来利用现代操作系统和高性能应用程序中进程和线程级并行性。 这种配置允许在每个物理处理器上同时执行两个或更多线程1。 每个逻辑处理器使用处理器内核中的资源执行来自应用程序线程的指令。 内核使用乱序指令调度并发地执行这些线程,以在每个时钟周期内最大化使用执行单元。

CPU,core,package,die的概念

CPU and Core

CPU ≠ core。CPU是指整个的中央处理单元,指令在这里处理,信号从这里发出。

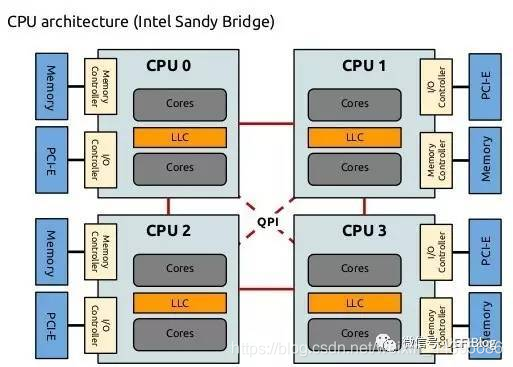

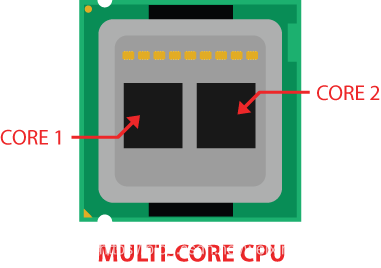

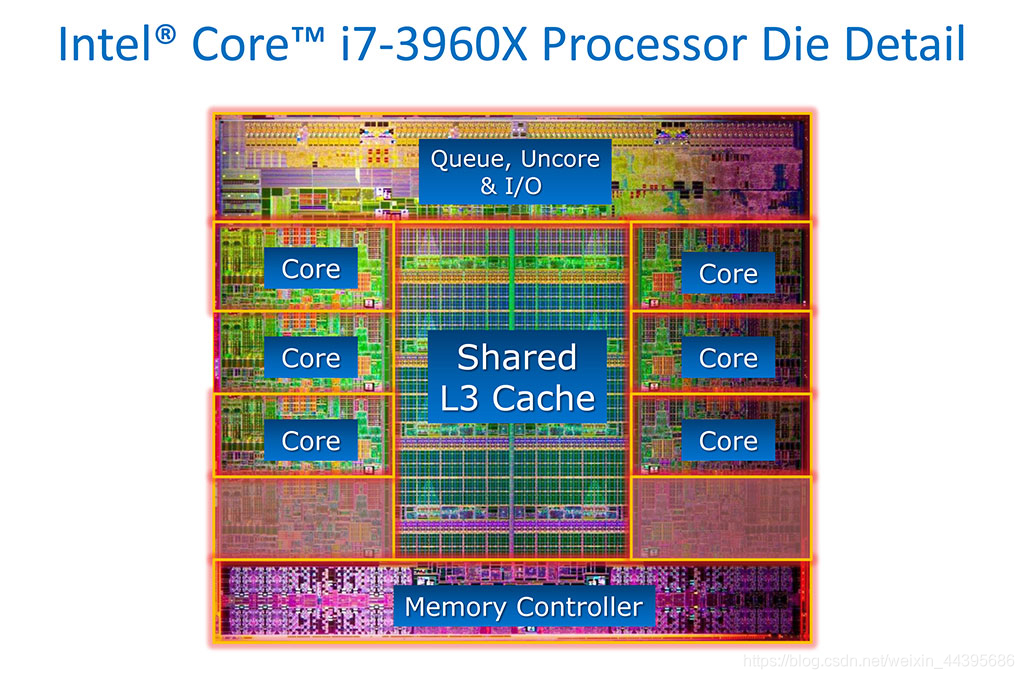

CPU包含的范围比较大,里面包含了core,内存控制器,PCIe控制器,片外总线这些东西,真正干活的是core,用来执行一条控制流(线程)。一个CPU中可能有多个core,平常我们说的物理核心都是指core,每个物理核心(core)都有自己的电路,看下面这幅图。

如上图,多个CPU和多核是不等价的两个概念。

core (Physical)

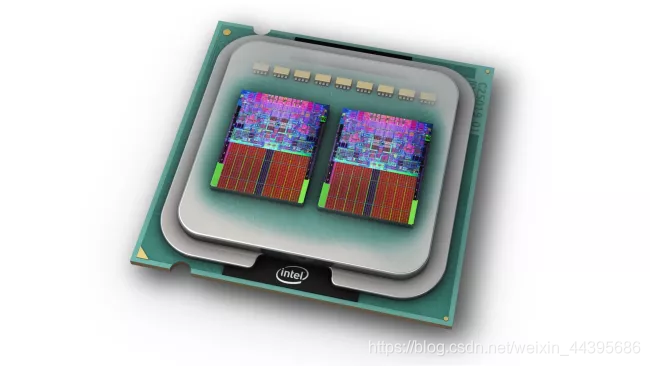

物理核心(core)是一个独立的执行单元,它可以与其他核心(core)并行运行一个程序线程。现代CPU具有多个core,这些core几乎都是独立的处理单元。供应商可以将core作为独立的裸片(die)制造在同一封装(package)上,也可以在同一裸片(core)上蚀刻。

下图中两个黑色方块代表core,灰色的是die。

每个物理核心可以有2个逻辑核心。然而,逻辑核心与在同一物理核心上运行的其他逻辑核心共享资源,因此,拥有更多的逻辑核心并不一定会获得与拥有更多物理核心相同的性能提升。

在intel超线程(HT)的情况下,每个物理内核有两个逻辑内核,所以一个四核(物理)i7处理器将有八个逻辑内核。然而,一个物理核心中的两个逻辑核心不能真正地相互并行操作。这是因为HT的工作原理是,当一个逻辑核心在等待,而另一个逻辑核心却无事可做(例如,当它在等待缓存或内存取出时)时,让一个逻辑核心进行操作。

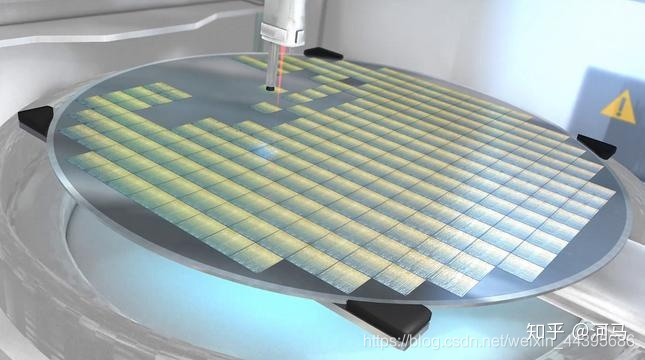

die

知乎有两篇文章对die介绍的很清楚,看完就懂

Die是处理器在生产过程中引入的概念。总的来说,Die或者CPU Die指的是处理器在生产过程中,从晶圆(Silicon Wafer)上切割下来的一个个小方块(这也是为啥消费者看到的CPU芯片为什么都是方的的原因),在切割下来之前,每个小方块(Die)都需要经过各种加工,将电路逻辑刻到该Die上面。

die是一块半导体材料(通常是硅)。一个die可以包含任意数量的core。最多有15种可用于英特尔产品线。die是构成CPU的晶体管的实际所在。

对于主流的CPU厂商Intel和AMD而言,他们会将1个或者多个CPU Die封装起来形成一个CPU Package,有时候也叫作CPU Socket(CPU插槽),如下图所示:

而对于AMD的EYPC CPU而言,它的每个CPU Socket由4个CPU Die组成,每个CPU Die中包含有4个CPU内核,如下图所示,黑色的长方形就是die,每一个中有4个core(物理核心),不过看不见。

CPU Die之间通过片外总线(Infinity Fabric)互联,并且不同CPU Die上的CPU内核不能共享CPU缓存,而单个Die的Xeon处理器内和所有CPU内核其实是可以共享CPU的第三级缓存(L3 Cache)的。

总结:die就是一个硅片,在它上面可以安装core,一个core或者多个core都可以。core是一个完整且独立的执行单元。HT技术可以让一个core并发的执行两个控制流(线程),通常就说这个物理core可以模拟出两个逻辑核,4核8线程就是说有四个核心(core),这4个是物理存在的执行单元,8线程指模拟出来的8个逻辑核,实际并不存在8个,只是在逻辑层面来可以说有8个。

package

package是当你购买单个处理器时所得到的。这里的CPU“package”是指包含一个或多个die的塑料/陶瓷外壳和镀金的触点,以配合你的主板。主板上的每个CPU插槽(socket),只能接受一个package。package是插在插座上的单元。如下图,左侧全是金属触点的是CPU package的背面,右侧有一个明亮外壳的是CPU package的正面。

你至少会有一个核心(Core)、一个die和一个Package。为了使CPU可以正常工作,它必须有一个可以执行命令的单元,一块物理上包含实现处理器晶体管的硅,以及将硅连接到主板和IO上的接口的封装。

Dual-core

双核处理器是一个包含两个物理核心(core)的package。可以是一个die,也可以是两个die。第一代多核处理器通常在一个package上使用多个die,而现代设计将它们放在同一个die上,这带来了一些优势,比如能够共享on-die缓存。下图是一个双核心(core)的CPU,使用了两片die,每片上有一个物理核心(core)。

“CPU”并不是很明确的一个词。当人们购买“CPU”时,他们购买的是CPU package。当他们检查“CPU扩展”时,他们讨论的是逻辑核心。这样做的原因是,在大多数实际应用中,双核处理器(Dual-core )的行为类似于两个处理器系统(两个CPU),即有两个CPU插槽或两个CPU单核package的系统,因此在讨论可伸缩性时,最合理的做法是统计可用的核心(core);它们是如何安装到die、package和主板上的就不那么重要了。

die,package和CPU的关系

来自Intel 工艺流程图