(1)小数的表达

参考:

https://www.cnblogs.com/woshitianma/archive/2013/05/19/3087258.html

x表示实际的数(*一个浮点数), q表示它的Qn型定点小数(一个整数)。

q = (int) (x * 2^n)

x = (float)q/2^n

以Q12为例:

假设定点小数用16位二进制表达,最高位是符号位,那么有效位就是15位。小数点之后可以有0 - 15位。

我们把小数点之后有n位叫做Qn,例如小数点之后有12位叫做Q12格式的定点小数,而Q0就是我们所说的整数。

Q12的正数的最大值是 0 111 . 111111111111,第一个0是符号位,后面的数都是1

那么这个数表示的小数为0x7fff / 2^12 = 7.999755859375。

对于Qn格式的定点小数的表达的数值就它的整数值除以2^n。

那么把一个实际所要表达的值x转换Qn型的定点小数的时候,就是x*2^n了。

例如 0.2的Q12型定点小数为:0.2*2^12 = 819.2,由于这个数要用整数储存, 所以是819 即 0x0333。

因为舍弃了小数部分,所以0x0333不是精确的0.2,实际上它是819/2^12 =0.199951171875。

(2)xilinx FPGA实现定点数转小数

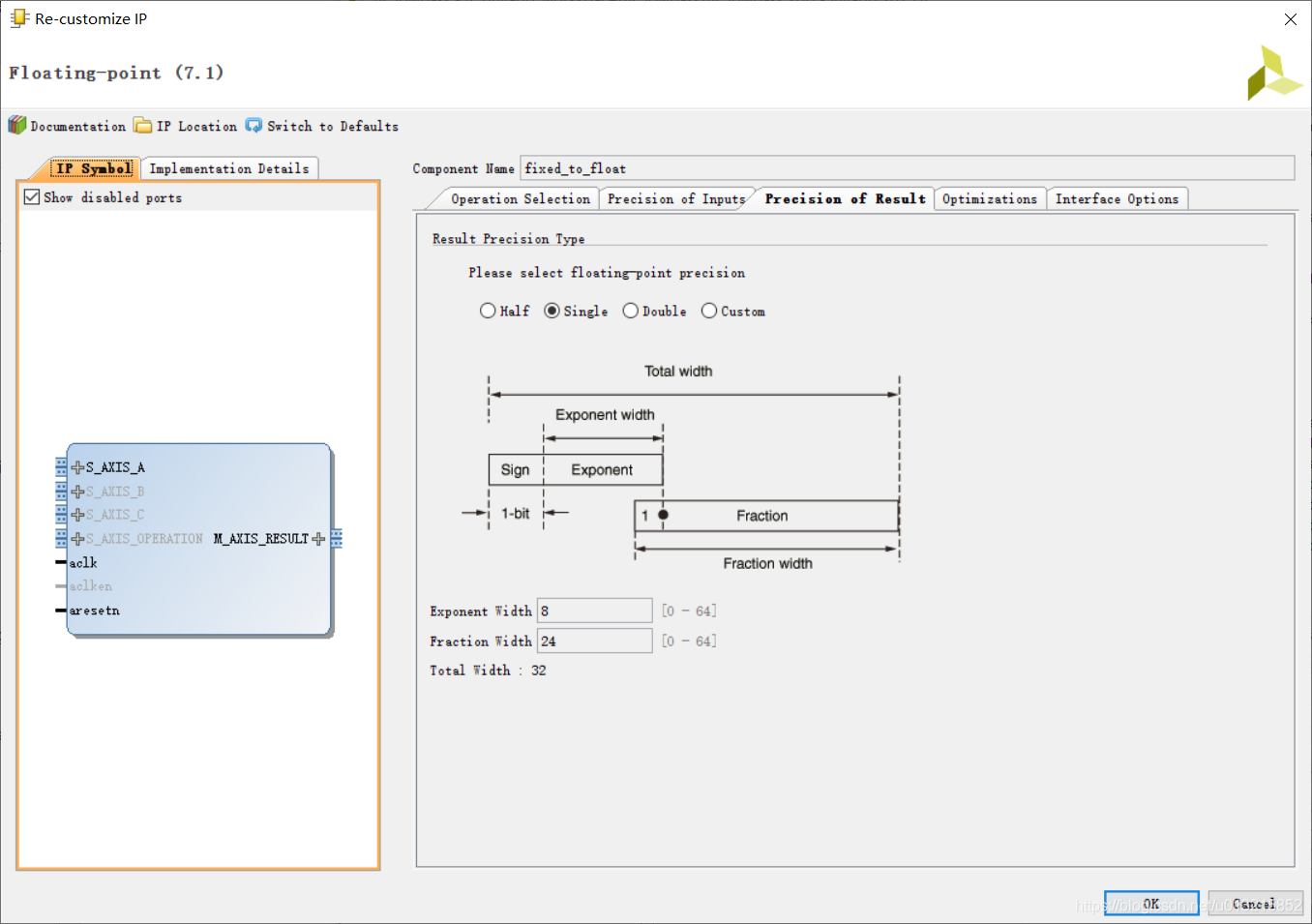

选用Floating-point IP核,这个IP核很强大,可以实现求解绝对值、加减乘除、定点浮点互转等。我们选择定点转浮点Fixed-to-float.

第二部设置输入信号的精度表达,我们的输入是16bit的有符号数,因此选择Custom,设置整形位宽为16,小数位宽为0

第三步设置需要的输出格式,再此我们选择单精度的浮点数,exponent width设置为8,小数部分设置为24

在此,有必要详细的说明一下单精度浮点数的表达方式:

标准的单精度浮点数,总位宽为32 bit,其中包含

1个符号位,表示正负

8个指数位,决定表示的最大值,

23个小数位,决定表示的精度,单精度数的尾数用23位存储,加上默认的小数点前的1位1,2^(23+1) = 16777216。因为 10^7 < 16777216 < 10^8,所以说单精度浮点数的有效位数是7位。

第四步,其他选项设置为默认即可

(3)仿真验证

设置输入的16bit数为有符号数,初始值为0

reg signed [15:0] s_axis_a_tdata = 0;

运行仿真后查看,右键设置s_axis_a_tdata显示为signed Decimal模式,可以看到从0逐渐递增

查看IP核的输出,设置m_axis_result_tdata为单精度浮点模式,我们可以看到IP核输出递增,数字正确,同时和输入相比延迟了7个时钟