USI0 异步数据接收

接收外部数据结构时,UART包括一个时钟和数据恢复装置。时钟恢复逻辑用于将内部产生的比特率时钟和从RXD0引脚引入的异步连续数据结构同步。

据恢复逻辑对引入进行采样和低通滤波,这样可以消除RXD0脚上的干扰

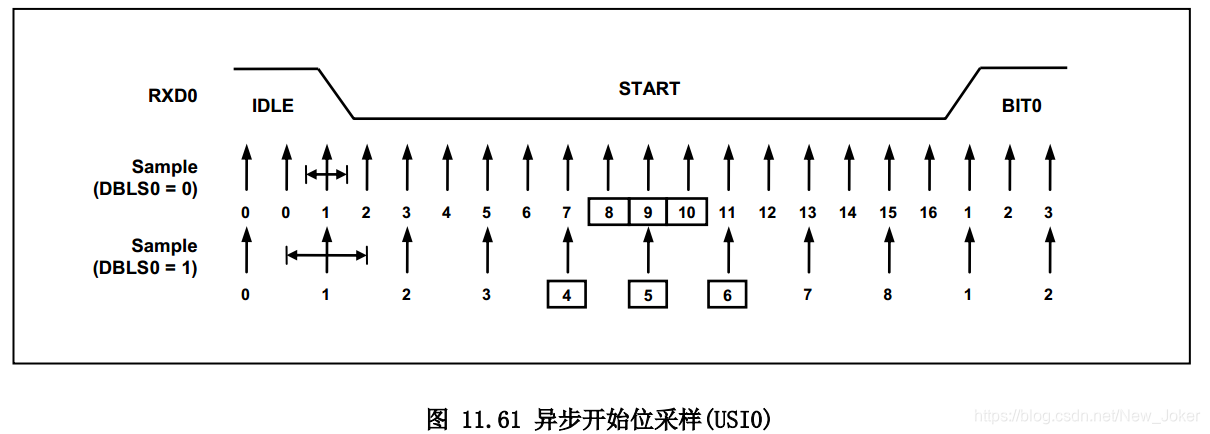

下面举例说明对一个引入结构的开始位进行采样的过程。采样率为波特率正常模式时16次。,双速模式(DBLS0=1)时8次,水平箭头表示的是由于异步采样引起的同步变化,注意多数时间显示的都是双速模式。

当接收使能时(RXE=1),时钟提取逻辑尝试在RXD0上查找一个由高到低的过度变化,这是开始位的条件。在RXD0上检测到由高到低的变化时,常规模式中时钟提取逻辑采用采样的8,9和10位以用于检测是否接收到有效的开始位。如果采样到多个俩个的逻辑低电平,就认为是有效的开始信号,同时内部产生的时钟同步进入的数据。

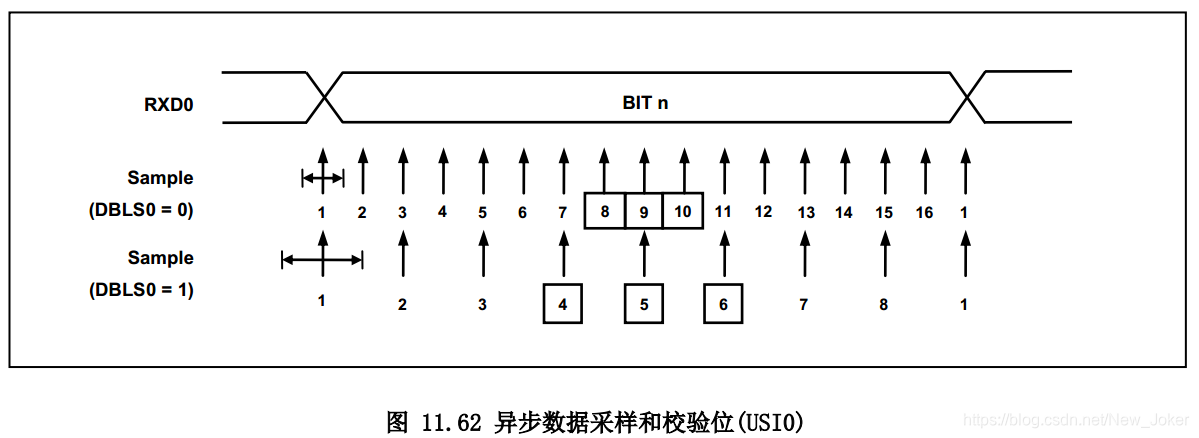

综上所述,当接受时钟和开始位同步时,数据传送开始。数据获取的过程和时钟获取的过程是类似的。常规模式时每个引入的位数据覆盖逻辑采样16次,双速模式时采样8次。常规模式时采样的8,9,10决定数据值。如果采样到多个2个的低电平,接受位认为是逻辑‘0’如果采样到多于2个的高电平,则认为是逻辑‘1’。数据覆盖过程一直被重复直到包含一个停止位的完整的数据接收完成。决定位的值按顺序存储到接收移位寄存器。注意接收器只使用第一个停止位。在内部接收到第一个停止位后,接收器进入空闲状态等待开始位。

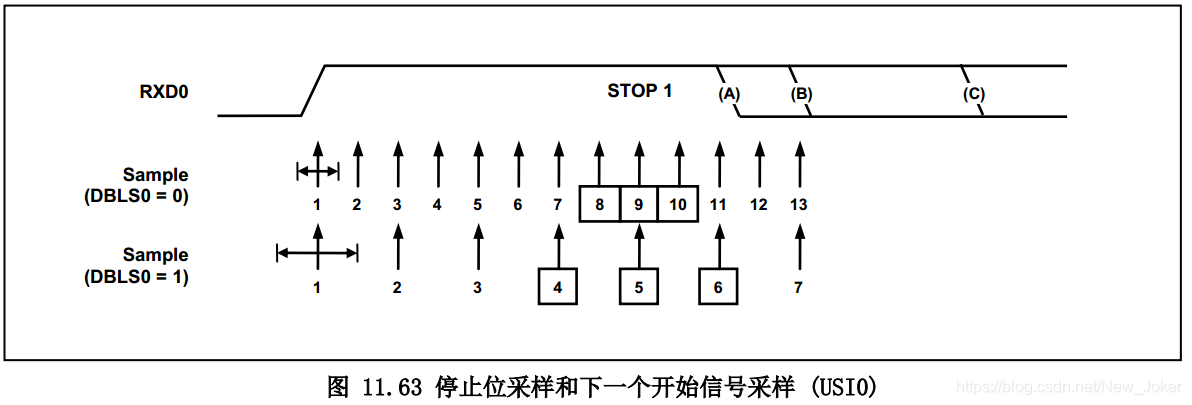

检测停止位的过程和时钟、数据的获取过程类似。也就是,如果采样到多于2个或3个中间值是高电平,就认为检测到停止位,否则,FE标志位置位。在确定第一个停止位有效后,接收器 进入空闲模式等待下一个开始位。