一个简单的例子:起初有两个.c和两个.h文件(hannuo.c不是不用管)

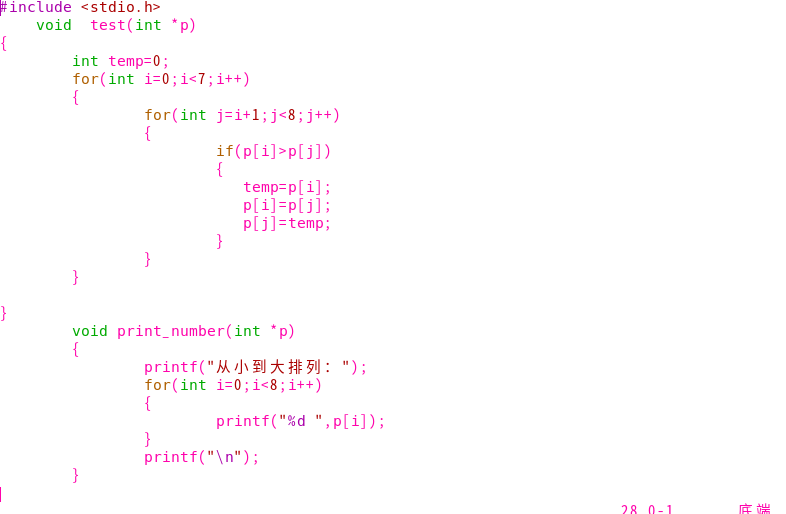

test.c:

test.h:

txt.c:

txt.h:

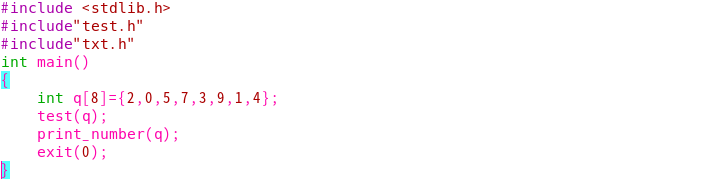

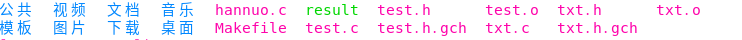

文件都在同一目录下:

一般情况下编译:

可以看到成功生成了result文件,执行:

现在通过编写Makefile文件来实现:

首先建立一个Makefile文件(之前我建好了如上,没有需要建一个,名字必须为Makefile或makefile),然后用vim对文件进行编写。

先写依赖关系,再写编译等命令(命令必须以tab键开头,这里将目标文件名定位result,可以自定)

---------------------------------------------------

result:test.o txt.o

gcc -o result test.o txt.o

test.o:test.c

gcc -c test.c

txt.o:txt.c test.h txt.h

gcc -c txt.c test.h txt.h

---------------------------------------------------

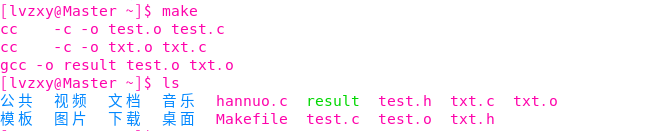

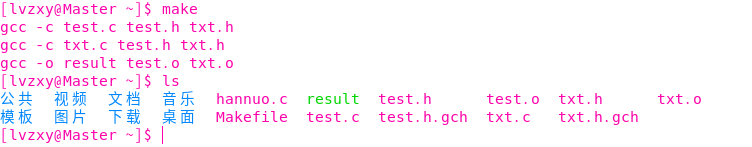

这样一个简单的Makefile文件就制作好了,接下来返回到终端,输入make命令就可生成result文件,运行一下成功。(下面先把原本生成的result删掉,代码复制粘贴后命令前的不是tab键,要改一下)

Makefile:

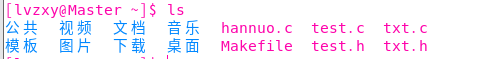

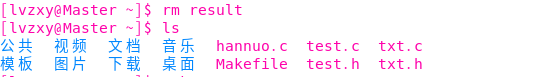

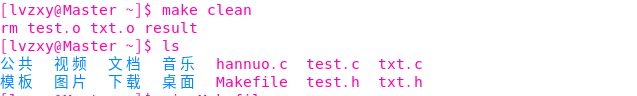

删result:

结果:

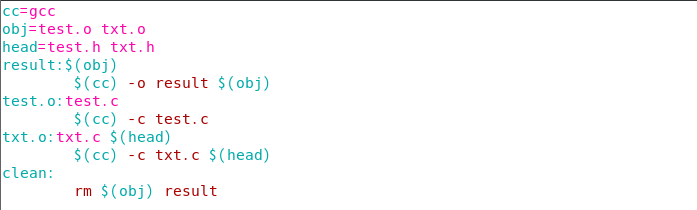

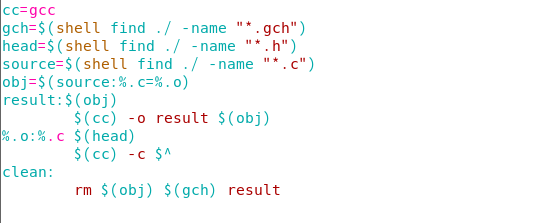

上面写法是最原始的一种,可以用字符串代替方法简化编写。

运行结果:

解释:"="前面的等价后面的,用$()来引用格式不变,clean:命令用来清除编译所生成的文件,$(obj)即生成的.o文件,result即生成的可执行文件,清除后如下。

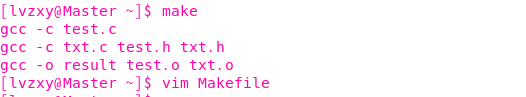

还有写法:

运行结果:

其中.gch为预编译头文件,加快编译速度

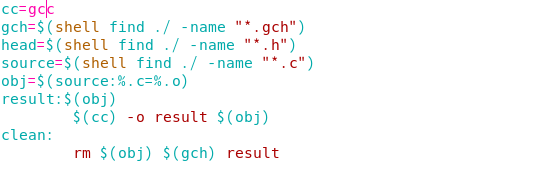

下面还有更简洁的写法:

运行结果:

在这里,我们用到了几个特殊的宏。%.o:%.c,这是一个模式规则,表示所有的.o目标都依赖于与它同名的.c文件(还有head中列出的头文件),$^表示所有依赖的关系的,这里即.c和.h文件,$<表示依赖关系第一项,即.c文件,不过这里没用到,只是介绍一下。如果.o或者其它文件过多则会看起来一大串还是不够简洁,可以添加函数来写使之更方便,如下:

或

其中,shell函数主要用于执行shell命令(终端命令)./即当前目录下,路径可以更改为你程序文件所在目录以便可以找到,具体到这里就是找出当前目录下所有的.c和.h文件。而$(source:%.c=%.o)则是一个字符替换函数,它会将source所有的.c字串替换成.o,即所有的.o文件,这样无论我们在该工程加入多少.c和.h文件Makefile都能自动将其纳入到工程中来,无需手动添加极其方便,同时无论生成多少其它文件,都可用make clean命令一次清除,还原到最初状态。上述皆学习所得必有不足,若有错误还请批评指教!