AMD锐龙处理器里面的CCD、CCX是什么

https://www.expreview.com/70525.html

我们在说AMD的锐龙处理器的时候经常会说CCD、CCX这两个词,熟练的玩家肯定懂我在说什么,然而对于萌新小白来说,估计根本不知道这是什么东西的缩写,其实我刚看到CCD这个词的时候,我第一反应其实是“这不是相机里的传感器吗?”,所以今天就来说说锐龙处理器里面的CCD和CCX是什么。

AMD Zen内核

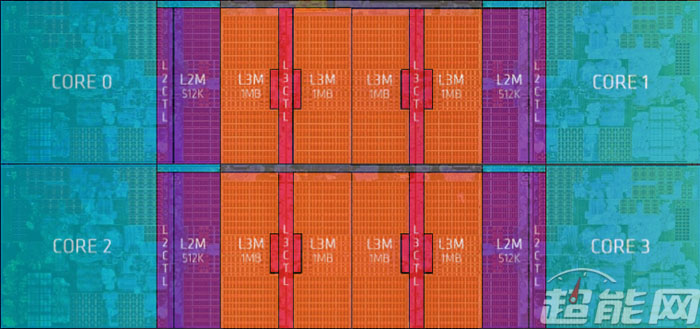

CCX是CPU Complex的简写,它是AMD Zen架构的最基本组成单元,每个CCX整合了四个Zen内核,每个核心都有独立的L1与L2缓存,核心内部拥有完整的计算单元,不再像此前的推土机架构共享浮点单元,这四个核心将共享L3缓存,每个核心都可以选择性的附加SMT超线程,另外CCX内部的核心是可以单独关闭的。

CCX

基于Zen架构的产品中可以存在多于一个CCX,其实非APU的产品内部都有两个CCX,即使是锐龙5 1500X这样的四核处理器也是由两个CCX所组成的,而锐龙5 2400G这样的APU和所有的AMD移动处理器内部都只有一个CCX,CCX之间使用高速Infinity Fabric进行通信,这种模块化设计允许AMD根据需求扩展核心、线程和缓存数量,针对消费客户,服务器和HPC市场推出不同的产品。

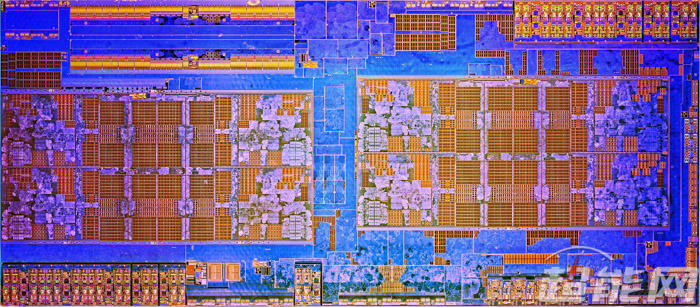

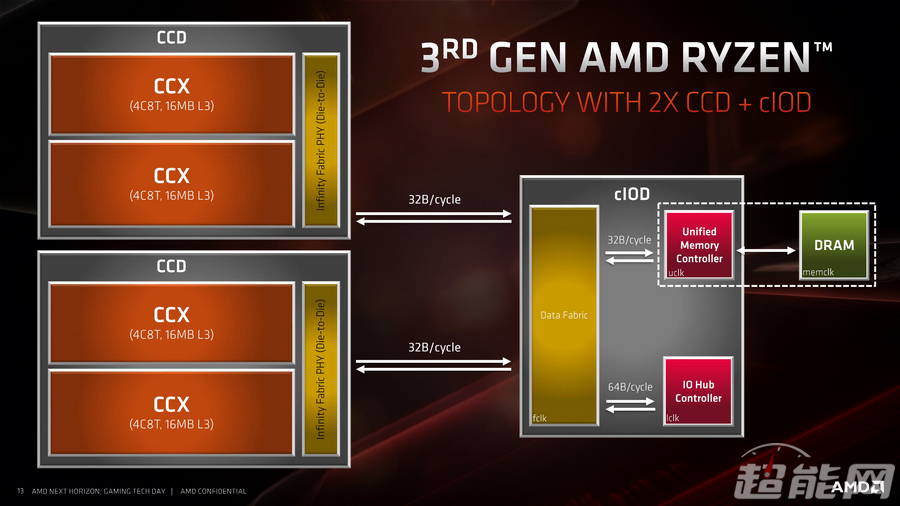

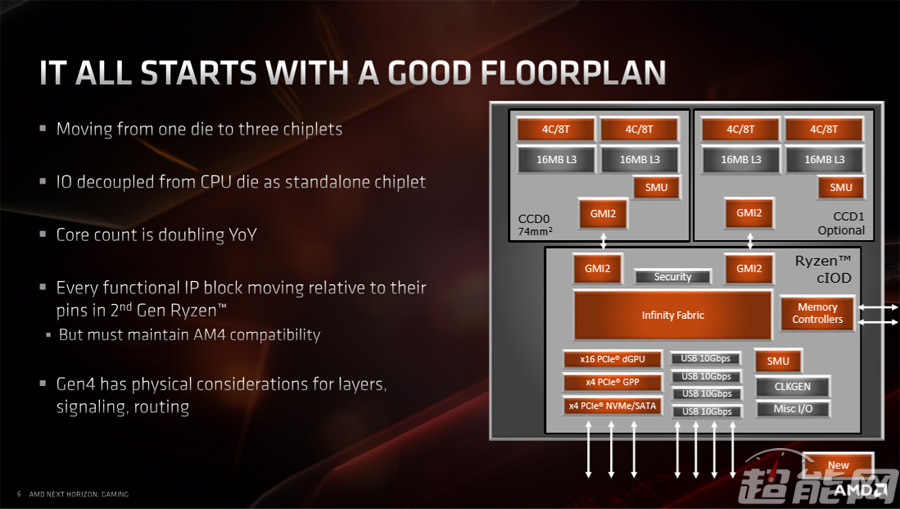

AMD所说的CCD其实是Core Chiplet Die的缩写,是伴随最新的Zen 2架构处理器所诞生的缩写。Zen 2架构处理器不是一个封装在一起的大核心,而是被分为了CCD核心以及I/O核心两个部分,其中CCD核心是单纯的计算核心,里面包含两个CCX,也就是每个CCD是8核16线程的,而内存、PCI-E、USB以及SATA控制器都被整合到I/O核心里面,而这些核心会被一同封装进一颗锐龙3000系列处理器里面。

CCD核心以及I/O核心之间采用第二代Infinity Fabric总线连接,它在扩展性、延迟和能效方面都有所提升,总线位宽从256-bit翻倍到512-bit,单位功耗降低了27%之多。AM4平台上所用的I/O核心最多可与两个CCD相连,也就是最多16核,而TR4平台上所用的I/O核心是可连接8个CCD的,所以最多可达64核。

把计算核心和I/O核心分开这样的设计其实有点像以前的南北桥设计,CPU只负责计算,而通信都交给北桥,而南桥则是北桥的一个手下,只不过AMD现在是把CPU和北桥封装到一块PCB上罢了。当然这样的设计必然会增大延迟,这样的结构并不利于CPU核心与内存控制器之间的数据交换,即便在是同一块PCB上,其内存延迟相比整合到CPU核心内部是要更高一些的,而且我们也可以看到,如果是对应8核以上产品,那么两个CCD之间想要交换数据,那么也得通过I/O核心上的Data Fabric总线进行,这也不是一个有利于提升CPU性能的设计。

所以AMD怎大了Zen 2架构内的L3缓存,与上代相比直接翻了一倍,并且使用了新的指令预测机制,延迟的问题其实很大程度上已经得到了解决。

另外MCM是一种灵活度很高的结构,这样AMD就可以使用不同工艺来生产不同的核心,实际上Zen 2处理器的CCD核心是7nm的,而I/O核心则采用更为成熟的12nm,毕竟7nm对于AMD来说仍然是一种新工艺,产能与成熟度都处于爬升阶段,价格也毕竟高,最重要的组成部分放在7nm工艺上,剩下的部分使用更为成熟的12nm工艺,这样也有利于提升产品的良品率,也可节省成本。

最后要说一下的是,这种把不同工艺的芯片MCM封装到一块PCB做处理器上并不是AMD先弄出来的,Intel早在第一代酷睿处理器就这样玩过,有兴趣的朋友可以查阅当年Clarkdale处理器的评测。