入门首先要掌握HDL(HDL=verilog+VHDL)

掌握一门编程语言的最好方法是渐进式刷题

强烈推荐该国外的Verilog题库,题库既包含练习题也包含语法教程与解题思路,难度由低至高,覆盖面广,从简单的组合逻辑语法、时序逻辑语法、状态机语法、testbench编写到时序图逆推Verilog电路描述应有尽有,同时,该网站还包括在线综合及检错功能,写完题目可以立即验证,解决了该题库后,可以去FPGA4FUN上学习下各类接口、驱动及基于FPGA电子小制作,很有意思。

刷题整理(一)

Verilog语法原则要注意

- 一个reg最好只在一个always块里进行赋值操作

- if-else或case等条件选择语句需要完备的条件,防止综合出不必要的latch(关于 default和else的必要性——组合逻辑的case最好要有default,因为如果case不全,就会产生锁存器。及时case都包含全了,但是还是建议加上default,因为万一哪天改代码把某个case给去掉了,就会产生隐含的latch,所以,最好加上default。对组合逻辑来讲,case的default和if…else是需要特别注意要有default和else的。对时序逻辑来讲,如果默认情况是什么都不做的话,default和else是可以不要的。要跟不要没有什么区别)

- reg或wire变量的位数定义尽量和需要的最小位数一致,减少无用BIT综合后的警告

- 减少触发器之间的组合逻辑长度,缩短组合逻辑造成过长的时延影响时序的准确性

- FPGA 未标明位数的变量,如a <= 3;,默认"3"为32bit,因此要养成标明位数的好习惯

- verilog +号 和或逻辑不可混用

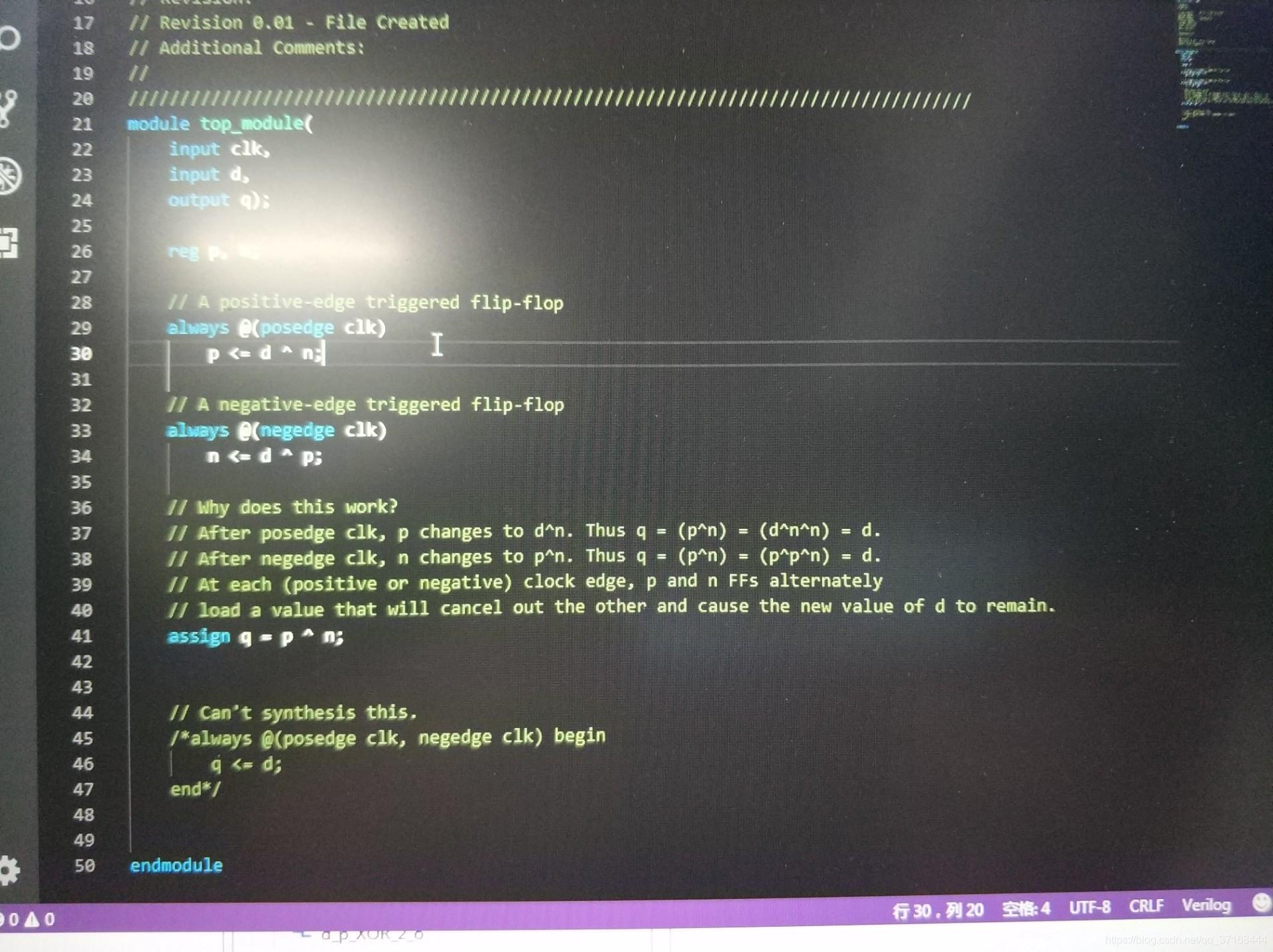

- 想要对时钟进行双边沿触发:

①使用电平敏感触发,能够实现时钟的双边沿触发,但是一般不推荐这种方法触发,这种方法虽然在逻辑上是可行的,但verilog终归不是C一样的高级语言,它的每段代码都需经过综合布线实现的,因此在用verilog实现算法的时候还需考虑代码书写风格的合理性,而对时钟信号使用电平触发,很有可能在某些情况下就不能满足时序。

②将上升沿和下降沿分成两个always块来写

- 区分逻辑运算符和按位运算符:&&与&、!与~、|与||

- 保持整体的同步设计不容易出现时序问题,在同一设计里使用多个时钟来驱动的异步设计功夫不到家别采用

- Verilog中有四种逻辑数值:逻辑0,逻辑1,x:未知态,Z高阻态;其中x、z是不区分大小写的;在verilog中,表达式和逻辑门输入的z通常解释为x,也就是不定态(无关态),不能确定这个逻辑值是1还是0。实际电路中只有0或者1,没有x和z,当你给电路中设置为x或z时,由编译软件或者综合软件等EDA软件决定电路最终是0或者1

- FPGA reset信号设置注意:reset 可能会导致采样丢失(锁存),因此每一个always块里的reset情况要对该快里的reg或wire全覆盖

- 程序可前仿真不一定可以综合,设计布局布线仿真正确可能在芯片上跑起来不正确

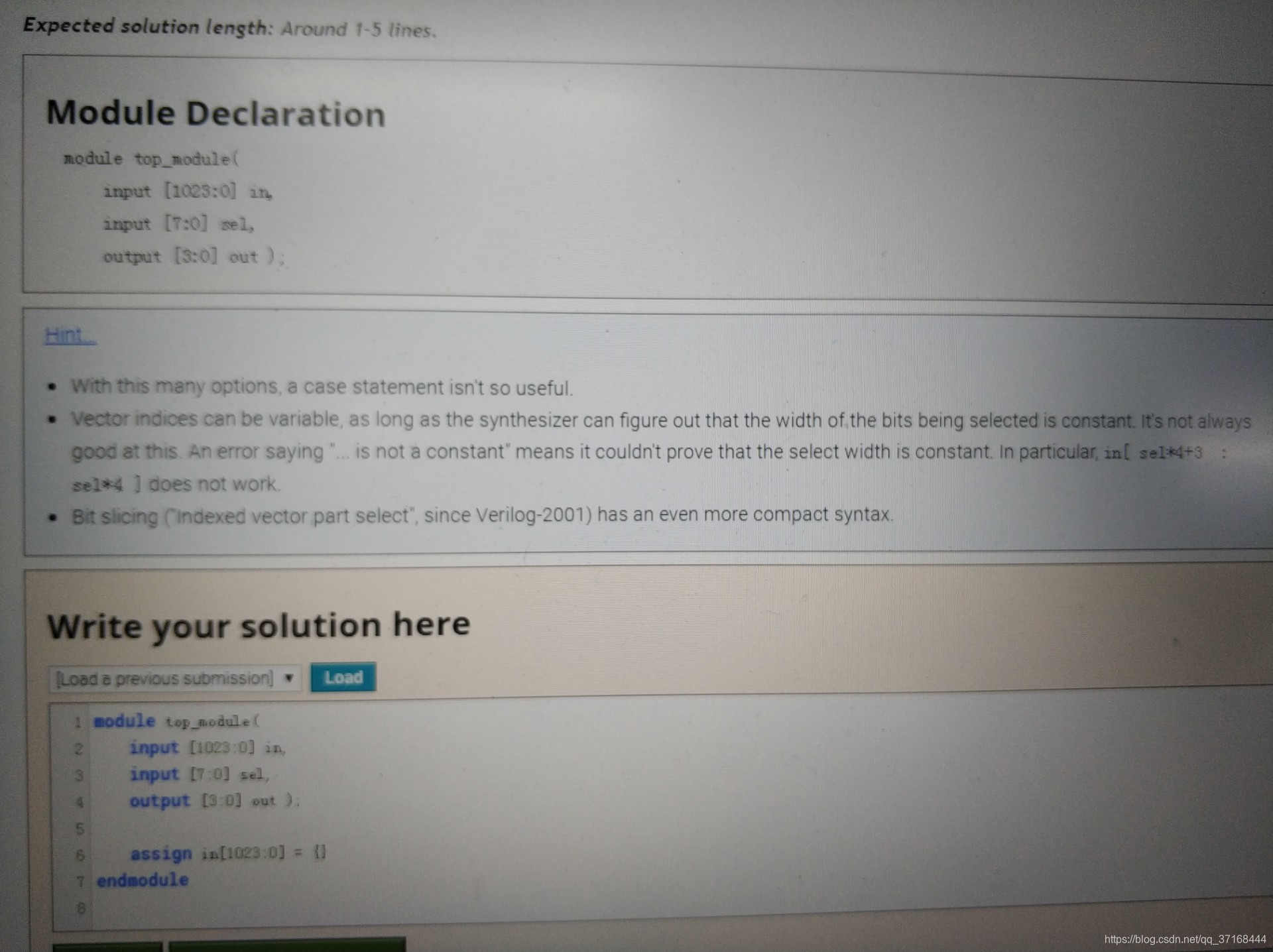

- 关于verilog变量索引:只要合成器能够确定所选位的宽度是恒定的,矢量索引就可以是可变的。特别是,使用变量索引从矢量中选择一位将起作用。但是有例外:因为一次只能选择一位

- 实例连接要注意:模块A->模块B,模块A的输出会滞后一些,总之连接后信号会有输出滞后而实际上不会像仿真信号一样和时钟对齐,可以通过错开半个时钟周期解决