前言

最近在学习PCB板制作,设计软件使用的是PADS,对比大学使用的AD而言,感觉PADS界面清爽,反应快,移动和框选元器件方便,尤其是敷铜这方面,隐藏显示及其快捷,PADS用了一年多了,现在打开老的AD图纸,感觉不怎么会用了,PADS和cadence搭配体验更佳哦。

以前画的板子也都不涉及到高速PCB这方面,也就很少考虑到布线布局这方面的规范,顶多考虑一下安规和布局布线及其常规的知识,保证电路在验证设计这方面不会出错,但最近要画一板比较复杂的电路PCB,从批量生产稳定方面看,要考虑到的细节也就更多了,希望在设计时暴露的错误多一点,这样印象也就深刻一点。

3W原则

搜索PCB设计原则,出现了所谓的3W原则,20H原则以及五五原则。

首先从什么叫3W原则,为什么使用3W原则,以及使用场景。

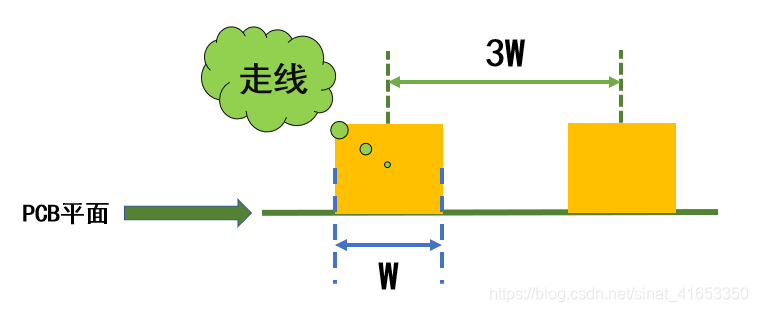

3W原则顾名思义就是3倍线宽,实际上是线与线之间保持3倍线宽,具体示意如下图,

但在实际应用上,受板框,器件以及安规等其他方面影响,并不是板上所有布线都要强制符合3W原则,但对于一些易受干扰的和强干扰的信号线(类似于电磁干扰的三要素:骚扰源,耦合通道以及敏感设备)必须需要减少它们之间走线的串扰。

在电路设计中,一般来说脉冲电路,开关电路,振荡电路以及电源电路都是较为强烈的干扰源,而对于一些微弱模拟信号输入,差分输入端(典型的485电路的上下拉电阻)以及复位线(以前就遇到一打静电,就将系统啪的一下重启复位)等信号线就属于易受干扰的信号线。

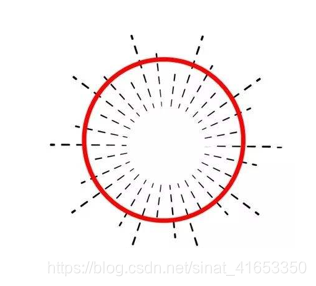

它们之间的耦合通道一旦形成,就形成了串扰,即两条信号线之间耦合引起线上的噪声。容性耦合引发耦合电流,感性耦合引发耦合电压,根据麦克斯韦定律,只要有电流存在,就会存在磁场,磁场之间的干扰就是串扰的来源,这个感应信号可能会导致数据传输的丢失和错误传输。

当一个信号在传输通道上传输时,因电磁耦合对相邻的传输线产生不期望的影响,在被干扰信号线里注入了一定的耦合电流和耦合电压,过大的串扰可能引起电路的误触发,包括电路其他的重要走线(数据线,地址线,控制线以及I/O线)产生影响,导致系统无法正常工作。

言归正传,降低走线之间的串扰的措施其中一项就是增加走线之间的距离,其中3W原则中提到,当走线中心间距不少于3倍线宽时,则可保持70%的电场不相互干扰,如果要达到98%的电场不相互干扰,可使用10W的间距。

首先,3W原则成立是有先决条件的,从串扰成因的物理意义出发,了解到要有效地防止串扰,该间距与叠层高度,导线线宽有关,且3W原则一般是在50欧姆特征阻抗传输线条件下成立的。这是一种防止串扰的方法,但仅做参考并作为如何防止串扰的一种启发,比如可以只将易受干扰信号采用3W原则。在实际PCB设计中,如果要使用到这一设计原则,必须在PCB布线前决定哪些线使用3W原则。