デジタルしばしばいくつかの論理ゲートを使用する回路、例えば、「ANDゲート」、「OR」、「NAND」ゲート回路など、アナログ回路CMOSレベルになりますしばしばTTLレベル。かどうかは、トランジスタからほとんど切っても切れない、設計またはゲートレベル変換回路です。アナログ回路の分析は、「負論理」回路になり、デジタル「NAND」内部回路、スクラッチ設計プロセス、一緒に簡単な回路が含まれている内容を見ています。

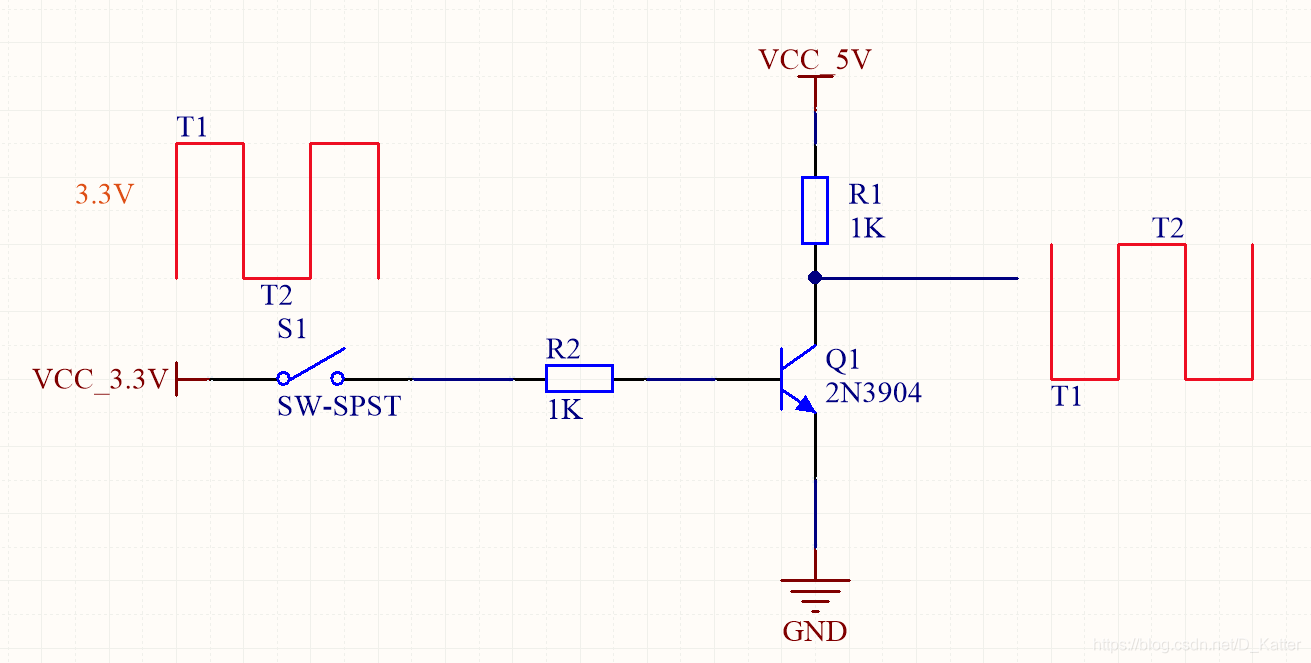

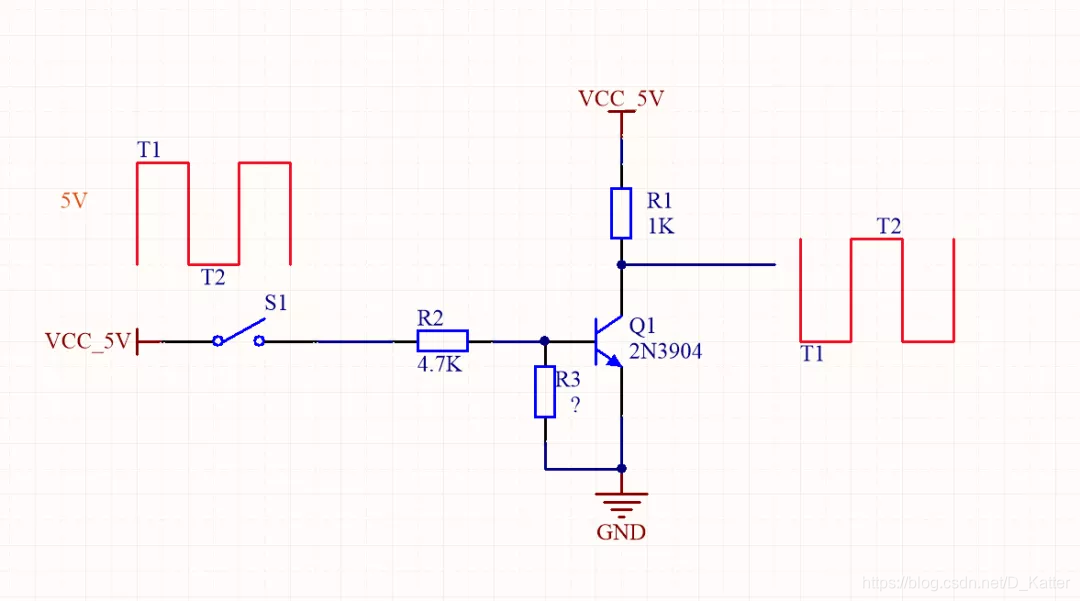

この回路は、それは、多くの場合、レベル変換回路で使用され、上記に精通しなければなりません。同図に示すように、制御信号は3.3Vであるが、トランジスタのコレクタに、すなわちVceが、レベル変換を実現することができる5Vに達することができます。

また、パルス信号の波形の位相と制御回路の出力電圧Vceから見ることができる:コントロール信号がハイのとき、出力信号は0Vであり、制御信号がローである場合、出力信号は5Vです。我々はレベル上端VCC_5V R1統一信号、負論理関数の回路実装の両方を制御する場合。

上記の分析の後、理論的なレベルでの回路は、機能を実現するために何ら問題は、それが回路の設計が合理的であることではありませんか?いや、それを言うために正確であることができます。

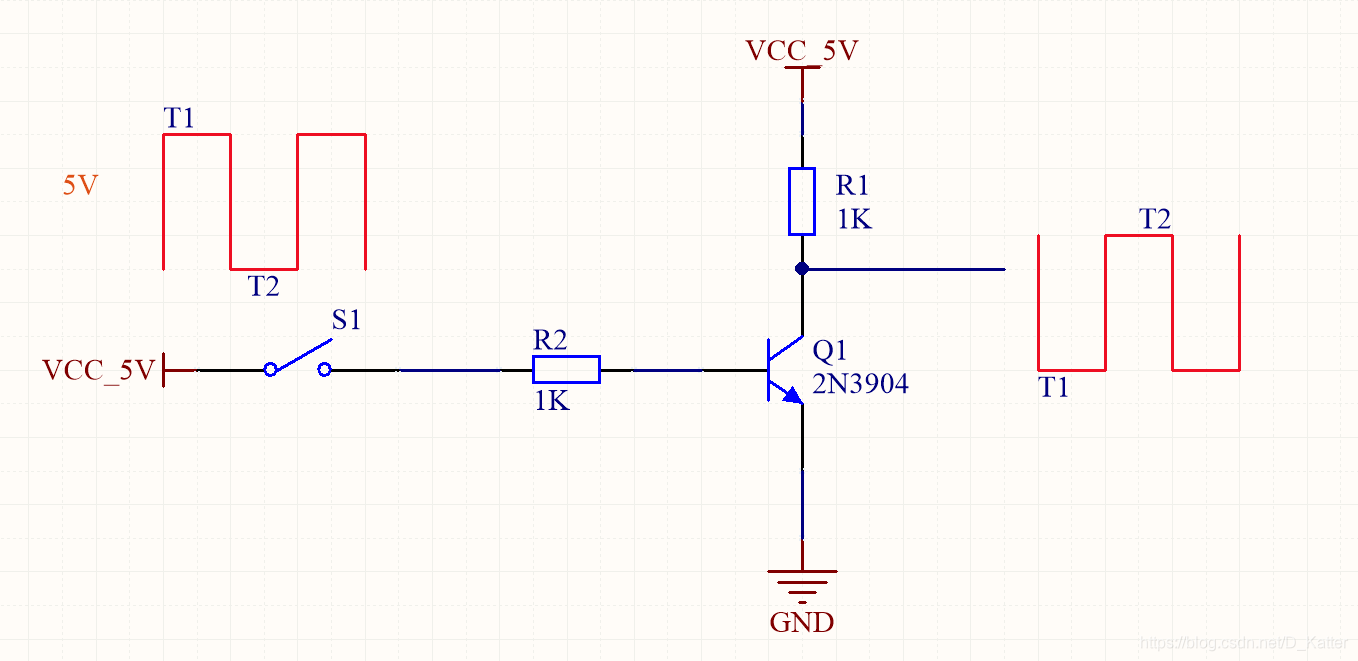

01.一つ不合理:トランジスタレベルの抵抗値のベース

Vbe≥0.7Vは、すなわち、電流Ibが流れ、Icの電流が流れるフロー制御トランジスタ型3端子デバイスのストリームに属します。それは論理回路、またはレベルシフタ回路を反転するかどうかと、トランジスタが「スイッチ」、即ち、三極管「飽和」として使用され、状態2「オフ」。

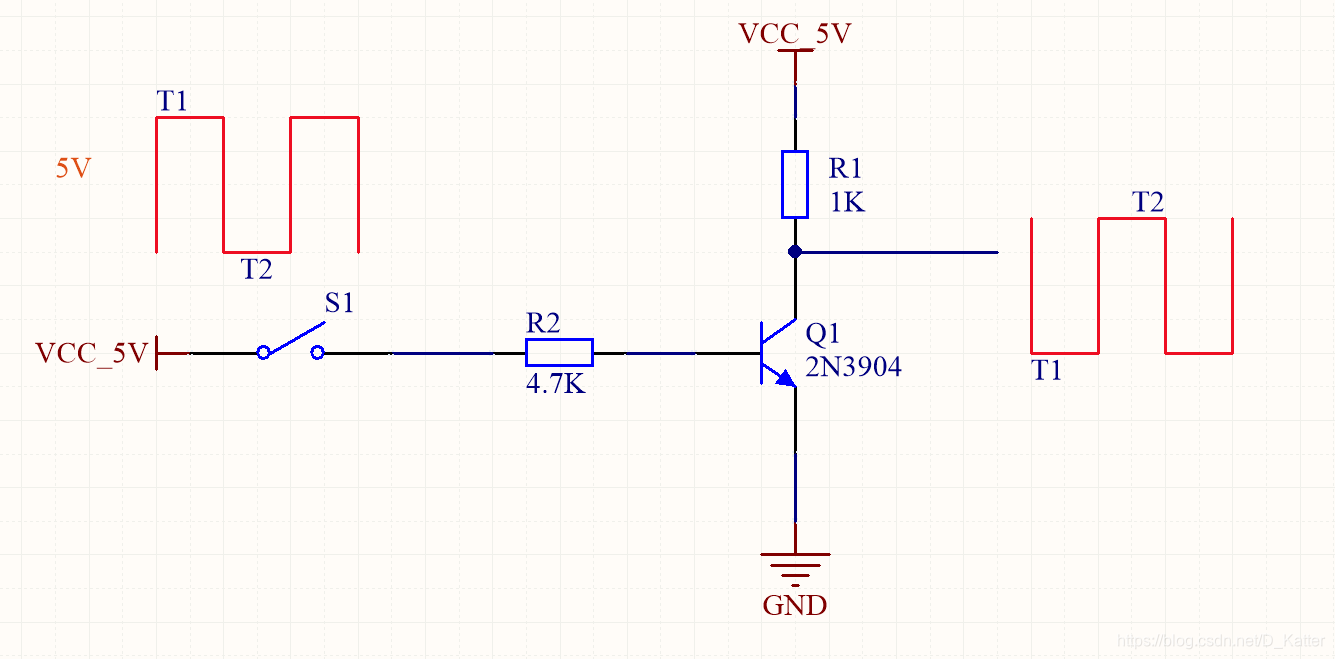

回路が適切に動作するため、Ib≥1mA、トランジスタが完全に飽和導通状態で動作するようになっている必要があります。制御信号が5Vであるため、R2の値は、条件5Kを満たすことです。アカウントに抵抗の値を取ると、ここで4.7Kフェッチ。R1は、ここに取ら1kのプルアップ抵抗です。なぜそれとR2 1K間違っを取りますか?ここでは、電力レベルからの逸脱があります。制御信号が5V、のVbe = 0.7Vであり、次いで、R2が増加し、抵抗R2 P =U²/ Rによって生成された電力は、消費電力が低減されます。

02.不合理2:トランジスタの基本構成は、高い表示されます

回路は、ここでいずれか一つの半導体装置は、未使用のピンをフローティング、いずれかその後、次に高いのいずれか、ローレベル(オンチップの一部のマニュアルも参照のみ二つの状態を可能にするために、ここで説明しません)、ハイインピーダンス状態の出現の発生を回避することです。高インピーダンス手段トランジスタ不安定状態のベースです。

当S1开关导通时,三极管的基极此时为高电平;当S1开关断开时,三极管的基极此时接R2,但是R2的左端悬空,即三极管的基极为高阻态(电平不确定)。既然电平不确定,就存在下面三个问题:

- 静电

- 雷击

- 电磁干扰

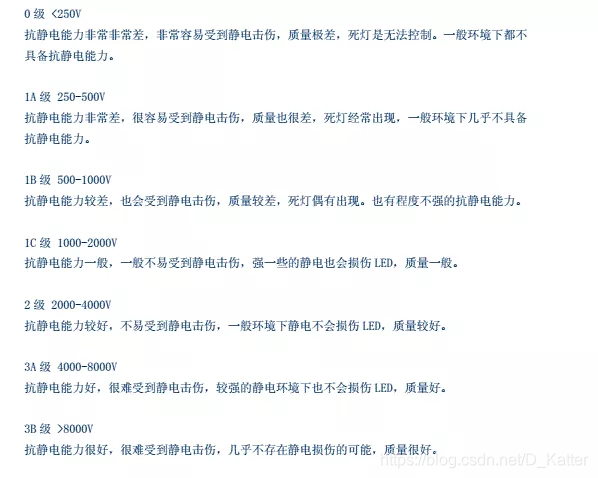

静电大家比较熟悉,冬天穿好衣服如果立马去开自己的笔记本电脑,经常会出现触电的感觉,这就是静电。而接触放电在瞬时可以达到4kV,如果刚好这个静电接触到R2的左端,那么三极管在这一瞬间就会误导通,甚至是损坏。所以经常会在产品上看到ESD防护等级要求,就是为了保证产品能过静电干扰。

雷击和静电破坏原理差不多,如果产品用在室外,碰上雷雨电气,R2左端会存在被几十KV雷击的危险,也会造成三极管的误导通,而且肯定被烧毁。

电磁干扰是因为在空气中存在着大量的电磁波,如果刚好在某个时候,周围存在一个非常大的电磁波被电路吸收,那么三极管还是存在误导通的风险。

因此,为了避免上面三种情况的发生,就要避免三极管的基极出现高阻态的情况。于是就在三极管的基极增加下拉电阻R3,保证开关断开时,基极接地。但是问题来了,R3的取值为多大呢?

R3的取值,从两个方面考虑,

-

流过三极管基极的电流Ib≥1mA

-

Vbe≥0.7V

由于R2的取值能够保证Ib,那是不是R3取2K,4.7K,5.6K 等,只要满足Vbe≥0.7V就可以呢?

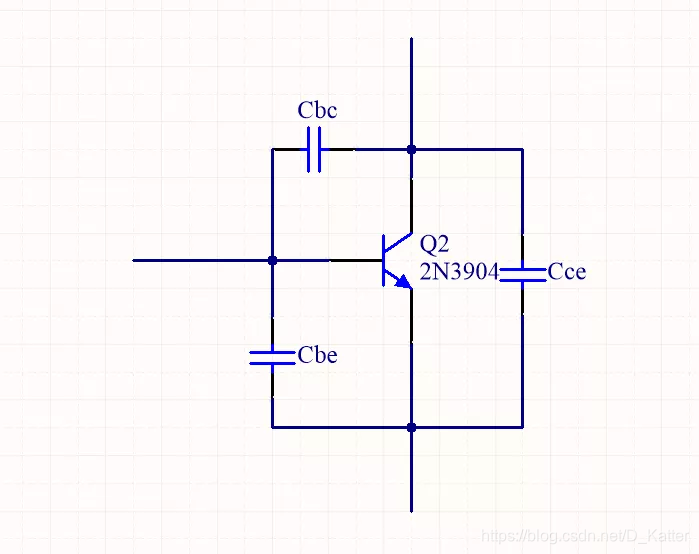

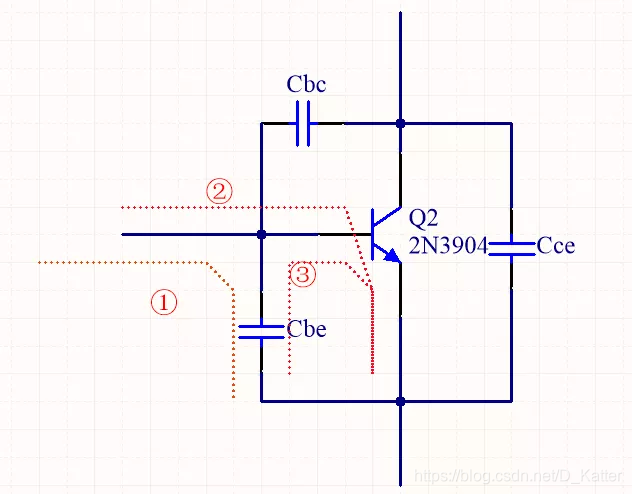

03.不合理之三:没考虑三极管实际特性

半导体器件和导体不一样,像电阻是导体,流过电阻两端的电压和电流是同相位,但是半导体器件由于生产工艺的原因,无法避免的在一些器件上产生了寄生电容也叫杂散电容。三极管的开通和关断就不能按照电阻那样分析,开关闭合,三极管立马开通;开关关断,三极管立马关断,这是理想的状态。对于实际的电路,三极管的开通也是需要时间的。三极管的等效电路如图所示(不考虑Cbc和Cce对电路的影响)。

三极管要开通,基极将经历下面的过程:

-

Ib电流对电容Cbe充电

-

Cbe达到0.7V以后,三极管导通

-

Cbe对be等效的PN结放电

-

トランジスタが完全にオンになると、その後Vceが0、飽和領域におけるトランジスタであり、トランジスタが完全に閉じられたときに、その後の5VのVceは、トランジスタは、作業領域にオフされます。プロセスの間に5V、0〜Vceが、このプロセスは、拡大中間状態を持って、トランジスタがオフになり、ブースト状態では、我々は、このように可能な限り迅速にするトランジスタをオフ、デザインに表示されることを希望していないということです。明らかにCbeは回路全体の、オープン中または停止中かどうか、邪魔に役割を果たしてきました。

R3が明らかに優れ値ではなく、トランジスタを高速化するためにオフにされ、トランジスタの開口を促進するためにわずかに充電電流を増大させることができ、R2を低減することができます。

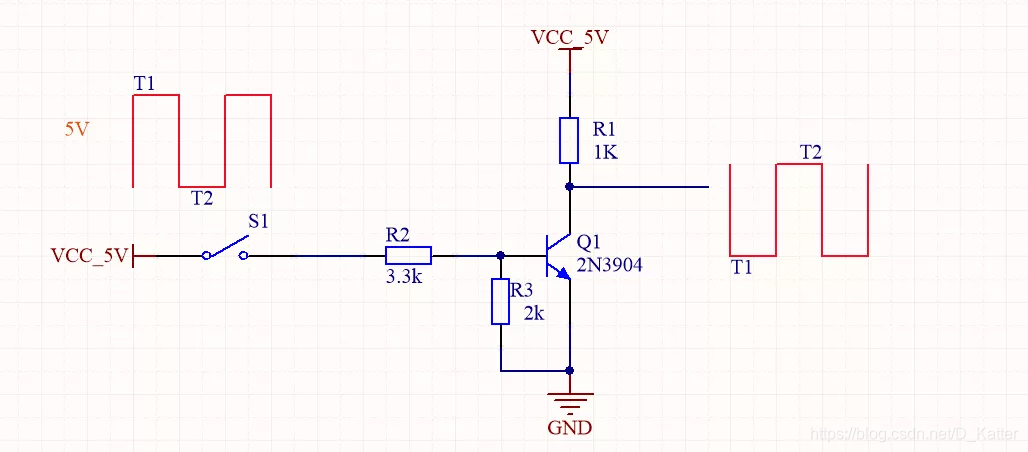

経験によれば、トランジスタのベース抵抗R2はR3は、2Kを撮影し、より適切である、を3.3kをとっ。

上記の分析からわかるように、簡単な回路のみを理論解析の機能を実現するために、含まれる含有量が多すぎる本当に、設計しなければ、回路に使用される実際の製品は、多くを通過する必要がありますその上、包装、モデル、価格、消費電力、製造性を含む検討事項、。

図に示すように、最終的な設計の論理反転回路。

その他のハードウェア設計内容、注意:[90]、アップポスト一緒に学び、進行。