1. 20のアナログ回路を詳しく解説

ブリッジ整流回路

ダイオードの一方向導電性: ダイオードの PN 接合に順方向電圧が印加されると導通状態になり、逆方向電圧が印加されると遮断状態になります。その電圧-電流特性曲線は次のようになります。

理想的なスイッチ モデルと定電圧降下モデル: 理想的なモデルとは、ダイオードが順バイアスされている場合、その管電圧降下は 0 であり、逆バイアスされている場合、その抵抗は無限大と見なされ、電流は 0 であることを指します。締め切りです。定電圧降下モデルとは、ダイオードがオンになったときの管電圧降下が一定値であり、シリコン管では 0.7V、ゲルマニウム管では 0.5V であることを意味します。

ブリッジ整流器の電流フロープロセス: u2 が正の半サイクルの場合、ダイオード Vd1 と Vd2 がオンになり、ダイオード Vd3 と Vd4 がオフになり、負荷 RL の電流が負荷を上から下に流れ、負荷は u2. 電圧の正の半サイクルと同じです。u2 の負の半サイクルでは、u2 の実際の極性は下では正、上では負です。ダイオード Vd3 と Vd4 はオンになり、Vd1 と Vd2 はオフになります。負荷 RL の電流は依然として負荷を上から下まで流れます。底部、負荷は正と u2 で正、半サイクルの間同じ電圧。

パワーフィルター

電源フィルタリングのプロセス分析: 電源フィルタリングは、負荷 RL の両端に大容量のコンデンサを並列に接続します。コンデンサの両端の電圧は急激に変化しないため、負荷の両端の電圧も急激に変化せず、出力電圧を平滑化してフィルタの目的を達成することができます。

-

波形形成プロセス

出力端子は負荷 RL に接続されており、電源が投入されると負荷に電流が供給され、コンデンサ C が充電されます。充電時定数: τ=(Ri∥RL・C)≈Ri・C

一般に、Ri は RL よりもはるかに小さいため、Ri の電圧降下の影響を無視すると、コンデンサの電圧は u2 とともに急速に上昇します。

-

ωt=ωt1のとき、u2=u0となり、u2はu0より低くなり、すべてのダイオードが遮断されます。このとき、コンデンサCはRLを介して放電され、放電時定数はRLCとなり、放電時間は遅くなります。 u0 は滑らかに変化します。

-

ωt=ωt2、u2=u0のとき、ωt2以降はu2>u0となり再び充電が始まり、u0は急激に上昇します。

-

ωt=ωt3、u2=u0の場合、ωt3以降コンデンサはRLを通して放電されます。

定期的に充放電を繰り返す。コンデンサ C のエネルギー蓄積効果により、RL の電圧変動は大幅に減少します。コンデンサフィルタリングは、電流がほとんど変化しない状況に適しています。LCフィルタ回路は大電流、電圧脈動が小さい場合に適しています。

-

フィルタコンデンサ容量と耐電圧値の選定

コンデンサフィルタ整流回路の出力電圧Uoは√2・U2~0.9・U2の間であり、出力電圧の平均値は放電時定数の大きさに依存します。

静電容量 RLC≧(3~5)・T/2 ただし、T は交流電源電圧の周期です。実際には、Uo≈1.2・U2 でさらに近似されることがよくあります。整流器の最大逆ピーク電圧 URM=√2・U2、および各ダイオードの平均電流は負荷電流の半分です。

信号フィルター

信号フィルターの機能: 入力信号内の不要な信号成分を十分小さなレベルまで減衰させますが、同時に有用な信号はスムーズに通過できるようにする必要があります。

-

パワーフィルターとの相違点と類似点

違い: 信号フィルタは信号をフィルタリングするために使用され、その通過帯域は特定の周波数範囲ですが、パワーフィルタは AC 成分をフィルタリングして DC を通過させ、それによって出力電圧を安定に保つために使用されます。 AC 電源では、特定の周波数のパスのみが許可されます。

同じことです。それらはすべて、回路の振幅周波数特性で機能します。

-

LC直列および並列回路のインピーダンス計算

直列接続した場合、回路インピーダンスは次のようになります。

Z=R+j(XL-XC)=R+j(ωL-1/ωC)

並列接続した場合、回路インピーダンスは次のようになります。

振幅と周波数の関係および位相と周波数の関係曲線は次のとおりです。

差動回路と積分回路

差動回路と積分回路

以下に示す微分回路と積分回路。

差動回路は、方形波を鋭いパルス波に変換することができ、主にパルス回路やアナログコンピュータ、計測機器などで、タイムベースの標準信号の抽出など、パルスの立ち上がりエッジや立ち下がりエッジに含まれる情報を取得するために使用されます。

積分回路は入力された方形波を三角波やランプ波に変換するもので、主に波形変換や増幅回路のオフセット電圧の除去、フィードバック制御における積分補償などに使用されます。その主な用途は次のとおりです。

-

電子スイッチの遅延に使用されます。

-

波形変換。

-

A/D変換では、電圧量が時間量に変換されます。

-

位相シフト。

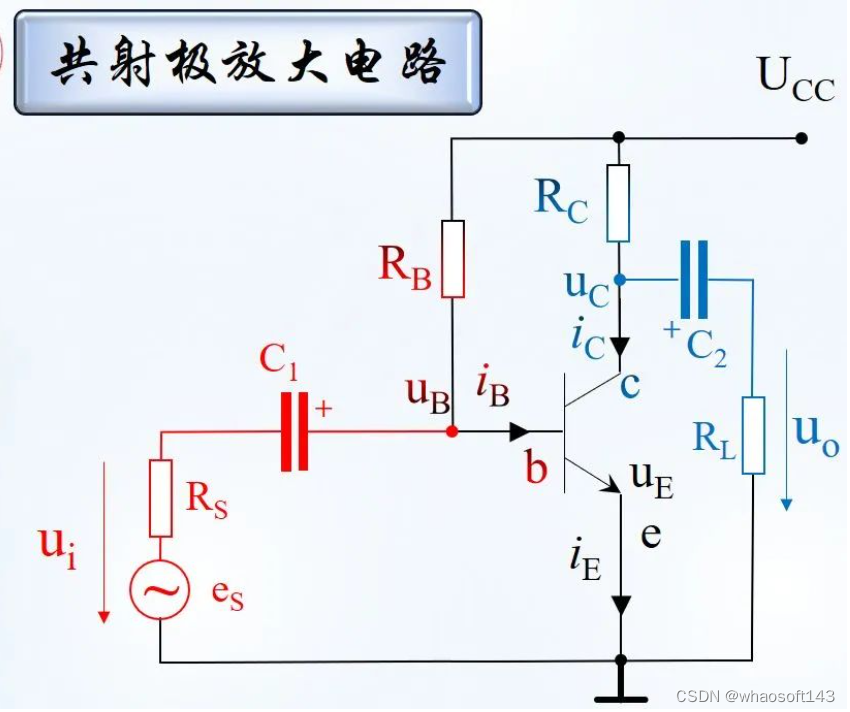

エミッタ接地増幅回路

以下にエミッタ接地増幅回路を示します。

エミッタ接地増幅回路の構造は単純で、電圧増幅と電流増幅が大きく、入出力抵抗が中程度ですが、動作点が不安定であるため、温度変化が小さく、技術的要求が高くない場合に一般的に使用されます。

特徴:

-

入力信号と出力信号が反転します。

-

大きな電流ゲインと電圧ゲインが得られます。

-

一般的に増幅回路の中間段として使用されます。

-

エミッタ接地アンプのコレクタとゼロ電位点の間には出力端子があり、負荷抵抗が接続されています。

分圧バイアス・エミッタ接地増幅回路

以下に示すように、電圧バイアスされたエミッタ接地アンプ回路。

分圧バイアスエミッタ接地増幅回路、つまりベース分圧エミッタバイアス回路は、BJT 増幅回路の 3 つの構成のうちの 1 つです。3 つの構成は、共射出、共セット、および共基本です。

このうち共通セット構成は電流増幅の効果があります。入力抵抗が最も高く、出力抵抗が最も低くなります。ベース接地構成は電圧増幅の機能があり、入力抵抗が最も小さく、出力抵抗が比較的大きくなります。エミッタ接地構成は、電圧増幅と電流増幅の両方を備えています。入力抵抗は中央にあり、出力抵抗は比較的大きくなります。

このため、多段増幅回路の入力段や出力段、バッファ段などではコレクタ接地構成が多く用いられます。共通ベース構成は、高周波または広帯域の低入力インピーダンスの場合によく使用されます。エミッタ接地構成は増幅回路の中段でよく使われます。

コレクタ接地増幅回路

下図に示すコレクタ接地増幅回路(エミッタフォロワ)。

コレクタ接地増幅回路はエミッタから信号を出力し、信号波形や位相は基本的に入力と同じであるため、エミッタフォロアまたはエミッタフォロワとも呼ばれ、バッファとしてよく使用されます。 。

コレクタ接地増幅回路は電流増幅器としてよく使用され、入力インピーダンスが高く電流利得が大きいという特徴がありますが、電圧出力のハット度はほとんど増幅されず、出力電圧が入力電圧に近くなります。 、入力インピーダンスが高いため出力インピーダンスが低く、インピーダンス変換器としてもよく使われます。

回路フィードバックのブロック図

フィードバック回路のブロック図は以下の通りです。

フィードバックは、増幅回路の出力の一部またはすべてがフィードバック ネットワークを通じて特定の方法で増幅回路の入力ループに戻され、回路の入力信号に影響を与えるプロセスです。

増幅回路の静的動作点は温度変化により上下に変動し倍率が不安定になりますが、増幅回路の静的動作点を安定させるために分圧動作点を使用することで安定化することができます。回路に DC 電流の負帰還が導入されます。

入力抵抗を大きくし、出力抵抗を下げるには、エミッタ出力素子を使用し、エミッタ出力素子回路に電圧直列負帰還を導入することができます。

ダイオード電圧安定化回路

以下に示すように、ダイオード電圧安定化回路。

ツェナーダイオードとは、pn接合の逆降伏状態において電圧は基本的に変化せず、pn接合の電流が広範囲に変化する現象を指し、電圧を安定化させるためにダイオードが作られています。

ツェナーダイオードの電圧・電流特性曲線の順方向特性は通常のダイオードと同様ですが、逆方向特性は、逆方向電圧が逆方向降伏電圧よりも低い場合、逆方向抵抗が非常に大きく、逆方向漏れ電流が大きくなります。非常に小さいです。しかし、逆電圧が逆電圧の臨界値に近づくと、逆電流が急激に増加し、これをブレークダウンといいますが、この臨界ブレークダウン点では逆抵抗が急激に小さくなります。電流は広範囲に変化しますが、ダイオードの両端の電圧は基本的に降伏電圧付近で安定しており、ダイオードの電圧安定化機能が実現されます。

直列電圧安定化回路

以下の図に示すように、電圧レギュレータ回路を直列に接続します。

直列電圧安定化回路は、変圧、整流、フィルタリングに加えて、一般に電圧安定化部に調整リンク、基準電圧、比較アンプ、サンプリング回路の 4 つのリンクを備えています。

グリッド電圧や負荷の変化により出力電圧 V0 が変化すると、サンプリング回路は出力電圧 V0 の一部を比較アンプと比較用の基準電圧にフィードバックします。

発生した誤差電圧を増幅して調整管のベース電流を制御し、調整管のコレクタ・エミッタ間の電圧を自動的に変化させてV0の変化を補償し、出力電圧をほぼ一定に保ちます。

差動増幅回路

以下に示すような差動増幅回路。

差動増幅回路は回路の対称性を持ち、動作点を安定させることができるため、直結回路や測定回路の入力段に広く使用されています。

差動増幅回路には、差動モードとコモンモードという 2 つの基本的な入力信号があり、回路の対称性により、2 つの入力端子に接続された信号の大きさが等しく、極性が逆の場合を差動モード入力信号と呼びます。 ; 2 つの入力端子に接続された信号の大きさが等しく、極性が逆の場合、それは差動モード入力信号と呼ばれ、信号のサイズと極性が等しい場合、それらはコモンモード信号と呼ばれます。通常、増幅したい信号はディファレンシャルモード信号として入力され、温度などの環境要因による回路への影響はコモンモード信号として入力されるため、最終的な目標はディファレンシャルモード信号を増幅し、コモンモード信号を抑制することです。モード信号。

差動増幅回路は直結増幅回路の基本構成要素であり、この回路は入力信号ごとに異なる影響を与え、コモンモード信号に対しては強い抑制効果があり、差動モード信号を増幅し、その増幅能力は出力モードに関係します。

電界効果トランジスタ増幅回路

以下の図に示すように、電界効果管アンプ回路。

トランジスタと同様に、電界効果トランジスタにも増幅効果がありますが、電流制御デバイスである通常のトランジスタとは異なり、電界効果トランジスタは電圧制御デバイスです。高入力インピーダンスと低ノイズが特徴です。

電界効果トランジスタの 3 つの電極、つまりゲート、ソース、ドレインは、それぞれトランジスタのベース、エミッタ、コレクタに相当します。

MOS 管は増幅領域で使用でき、非常に一般的です。ミラー電流源、オペアンプ、フィードバック制御などの増幅領域では、MOS 管が使用されます。MOS管の特性上、チャネルがオン・オフ状態にあるとき、ゲート電圧はチャネルの導電率に直接影響し、一定の線形関係を示します。ゲートはソース、ドレインから絶縁されているため、入力インピーダンスは無限大とみなせますが、当然周波数が高くなるほどインピーダンスは小さくなり、ある周波数では無視できなくなります。この高インピーダンス機能はオペアンプで広く使用されており、オペアンプ解析における仮想接続と仮想切断の 2 つの重要な原則はこの機能に基づいています。これは三極管とは比較になりません。

周波数選択(バンドパス)増幅回路

以下に示すように、周波数選択性 (バンドパス) 増幅回路。

周波数選択増幅回路は、通常、受信システムのフロントエンドに配置され、増幅された信号は小さな振幅と高い周波数を持ち、高周波小信号共振増幅器またはバンドパス増幅器とも呼ばれます。 。

オペアンプ回路

以下にオペアンプ回路を示します。

回路内のオペアンプは非反転入力端子と反転入力端子を持ち、入力端子と出力端子の極性が同じ極性のものが非反転アンプであり、入力端子の極性と出力端子の極性が同じです。出力端子は極性が逆です。

非反転入力の入力インピーダンスは高く、反転入力の入力インピーダンスは低くなります。非反転入力の入力インピーダンスは、基本的には非反転端に並列に接続されたバイアス抵抗によって決まりますが、この抵抗は非常に大きな抵抗で使用できます。この帰還抵抗は反転端と出力端の間にはありえませんが、非常によく使われるため、反転入力の入力インピーダンスは比較的低くなります。

差動入力オペアンプ回路

以下に示すような差動入力オペアンプ回路。

出力電圧はオペアンプ両端の入力電圧差に比例し、減算演算が可能になります。減算演算や測定アンプとしてよく使用されます。

電圧比較器

電圧比較器は入力信号を識別して比較する回路であり、非正弦波発生回路を構成する基本単位回路です。一般的に使用される電圧コンパレータには、シングルリミット コンパレータ、ヒステリシス コンパレータ、ウィンドウ コンパレータ、スリーステート電圧コンパレータなどが含まれます。

電圧比較器はアナログ回路とデジタル回路のインターフェースとして使用でき、また波形生成・変換回路などとしても使用できます。単純な電圧コンパレータを使用して、正弦波を同じ周波数の方形波または矩形波に変換できます。

RC発振回路

RC周波数選択回路で構成される発振回路はRC発振回路と呼ばれ、低周波発振に適しており、一般的に1Hz~1MHzの低周波信号の生成に使用されます。この回路は、増幅回路、周波数選択ネットワーク、正帰還ネットワーク、振幅安定化リンクの 4 つの部分で構成されます。主な利点は、シンプルな構造、経済性、利便性です。RC 周波数選択ネットワークのさまざまな形式に従って、RC 発振回路は RC 進み (または遅れ) 位相シフト発振回路とウィーン回路発振回路に分割できます。

LC発振回路

共振回路、タンク回路、または同調回路としても知られる LC 回路は、相互に接続されたインダクタ (文字 L で示される) とコンデンサ (文字 C で示される) を含む回路です。この回路は、回路が共振するときに振動するエネルギーを蓄積する電気共振器 (音叉の電気的アナログ) として使用できます。

LC 回路は、特定の周波数の信号を生成するためと、より複雑な信号から特定の周波数の信号を分離するために使用されます。これらは多くの電子機器、特に無線機器の重要なコンポーネントであり、発振器、フィルター、チューナー、ミキサー回路に使用されています。

水晶発振回路

水晶とは水晶振動子の略称で、二酸化ケイ素の結晶を一定方向に非常に薄いウエハ状に切断し、ウエハの対応する2面を研磨して銀層をコーティングし、2極リードとして使用します。水晶振動子を形成します。非常に安定した固有振動数を持っています。

水晶は六角柱の形をしているため、使用する前に適切なサイズに切断する必要があります。異なる発振周波数の水晶を得るには、加工時に異なる切断方法を使用する必要があります。切断した水晶を一対の金属板で挟んで水晶振動子を形成しますが、圧電効果があり、水晶の 2 つの極に外部電圧を印加すると水晶振動子が変形します。外力により水晶が変形すると、両極の金属板に電圧が発生し、適切な交流電圧を加えると水晶が共振します。印加される交流電圧の周波数が水晶の固有共振周波数と正確に一致する場合、その振幅は最大になります。

パワーアンプ回路

パワーアンプ回路は、より大きな電力を出力するように設計された増幅回路です。通常、負荷を直接駆動し、強力な負荷容量を備えています。電力増幅回路は通常、多段増幅回路の出力段として使用されます。

2. トランジスタを理解するためのいくつかのアニメーション画像

アナログ回路の難しい部分ともいえるトランジスタの電流増幅作用ですが、なぜ小電流Ibで大電流Icの大きさを制御できるのか、増幅の原理をこのアニメーションを使って簡単に説明したいと思います。回路。

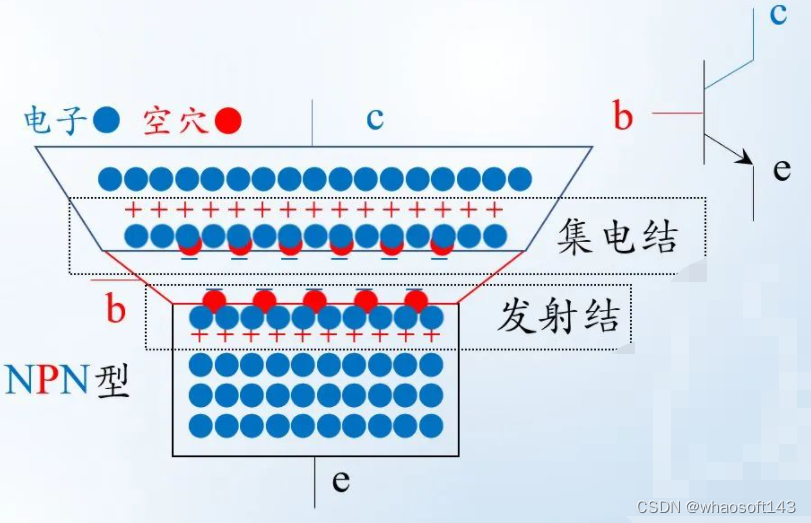

ここでいう三極管はバイポーラトランジスタとも呼ばれ、アナログ増幅回路や単純なデジタル論理回路に使用されます。コレクタ c、ベース b、エミッタ e、および 2 つの PN 接合 (コレクタ接合とエミッタ接合) があります。コレクタ領域は比較的大きく、ベースの厚さは薄く、キャリア濃度は比較的低い。下の写真はNPN型トランジスタで、 エミッタ接合が順バイアスされると電荷分布が変化し、エミッタ接合の幅が狭くなり、電子にとってはeからbへの扉が開くのと同じです。接合が逆バイアスされると、電荷分布も変化し、コレクタ接合幅が広くなります。これは、以下のアニメーションに示すように、電子が C 準位から逃げるのを防ぐドアを開けることと同じです。

エミッタ接合が順バイアスされると電荷分布が変化し、エミッタ接合の幅が狭くなり、電子にとってはeからbへの扉が開くのと同じです。接合が逆バイアスされると、電荷分布も変化し、コレクタ接合幅が広くなります。これは、以下のアニメーションに示すように、電子が C 準位から逃げるのを防ぐドアを開けることと同じです。

b ステージは、電流 Ib のサイズを制限するために大きな抵抗 RB に接続されます。以下のアニメーションに示すように、b 極に流れる過剰な電子はコレクタ接合を通過して電流 Ic を形成する必要があります。

ベース電圧が 2 倍になると、電荷分布は変化し続け、エミッタ接合幅は狭くなり、ゲートは広くなり、より多くの電子が b ステージに移動します。以下のアニメーションに示すように:

RB は大きな抵抗であるため、Ib が 2 倍になっても依然として非常に小さいため、より多くの電子がコレクタ接合を通過するため、Ic も 2 倍になります。以下のアニメーションに示すように:

2 つの DC 電源と小信号 ui および 2 つのコンデンサを組み合わせると、次の図に示すような増幅回路が得られます。

抵抗のサイズが適切であれば、次のアニメーションに示すように、この増幅回路は小信号 ui を逆位相の大信号 uCE に増幅できます。

抵抗のサイズが適切であれば、次のアニメーションに示すように、この増幅回路は小信号 ui を逆位相の大信号 uCE に増幅できます。

赤が入力端子で、ui の変化は UBE に影響します。エミッタ接合を小さな抵抗とみなした場合、赤い Q 点は黒い線に沿って移動し、iC=βiB に従って iB のイメージを描きます。 、iCのイメージを描くと、縦軸がμAからmAに変わり、出力端子はUCE=UCC-ICRCとなり、UCCとRCが変わらない場合、UCEとICが反転します。

最後に、これらのアニメーションの欠点について話しましょう。

-

ラッパのような三極管は私のオリジナルではなく、このリンクもありますが、水槽の比喩はICが最大であると誤解されやすいですが、実際にはIEが最大の電流です。ワオソフト アイオット http://143ai.com

-

このアニメーションは、電子の熱速度を完全に無視しています。この速度は、電圧の作用下での電子のドリフト速度よりもはるかに高速です。

-

アニメーションにはエネルギー準位、エネルギーバンド、フェルミ分布などの内容は反映されていません。

3. PCB設計におけるグランドバウンスを低減する方法

#1. グラウンドバウンスとは何ですか?

グランド バウンスは、PCB グランドとチップ パッケージ グランドの電圧が異なる場合に、トランジスタ スイッチング デバイスで発生するノイズの一種です。

グランドバウンスをよりよく理解するには、ロジックローまたはロジックハイ出力を提供できる以下のプッシュプル回路を考慮してください。

プッシュプル回路

この回路は 2 本の MOS 管で構成されており、上側の P チャネル MOS 管のソースが Vss に接続され、ドレインが出力端子に接続されています。下部の N チャネル MOS のドレインは出力ピンに接続され、ソースはグランドに接続されます。

これら 2 つの MOS チューブ タイプは、MOS チューブのゲート電圧に対して逆の応答を示します。MOS トランジスタのゲートにおける入力ロジック Low 信号により、P チャネル MOS トランジスタが Vss を出力に接続し、N チャネル MOS トランジスタが出力を GND から切断します。

MOS トランジスタのゲートにおける入力ロジック High 信号により、P チャネル MOS トランジスタがその Vss を出力から切り離し、N チャネル MOS トランジスタが出力を GND に接続します。

IC チップ上のパッドを IC パッケージ上のピンに接続するのは小さなボンド ワイヤです。これらの必需品には少量のインダクタンスがあり、上記の簡略化された回路でモデル化されています。もちろん、回路には一定量の抵抗と容量が存在しますが、これらの抵抗と容量はモデル化されていないため、必ずしも理解する必要はありません。

プッシュプル回路

フルブリッジ スイッチの等価回路には 3 つのインダクタが示されており、インダクタの記号はパッケージ インダクタンス (IC パッケージ設計に固有のインダクタンス) を表し、回路出力はいくつかのコンポーネントに接続されています。

入力が長時間論理レベルに留まった後にこの回路に遭遇することを想像してみてください。この状態により、上部トランジスタが上部 MOS チューブを介して回路の出力を Vss に接続します。適度に長い時間が経過すると、LO と LA に安定した磁場が存在し、ΔV O、ΔV A 、ΔV B 間の電位差が 0 ボルトになり、トレースに少量の電荷が蓄積されます。

入力ロジックがローレベルに切り替わると、上部の MOS トランジスタが出力から Vss を切り離し、下部のゲートが下部の MOS トランジスタをトリガーして回路の出力を GND に接続します。

この時点で、入力ロジックが変更され、結果がシステム全体に移動します。

#2. グランドバウンスの原因

出力とグランド間の電位差 電流は出力から下側の MOS を通ってグランドに流れます。インダクタは、磁場の変化に抵抗するために、蓄積された磁場のエネルギーを使用してΔV O とΔV B の間に電位差を作成します。

電気的に接続されていても、出力とグランド間の電位差は瞬時に0Vにはなりません。出力は Vss であり、MOS チューブ B のソースは 0V の電位であることに注意してください。出力ラインが放電すると、前の電位差により電流が流れます。

電流が出力からグランドに流れ始めると同時に、パッケージの誘導特性により、以前に確立された磁界を維持しようとして、ΔV と ΔV の間に電位差が生じます。

インダクタLBおよびLOは、MOSトランジスタのソースおよびドレイン電位を変化させます。MOSFET のゲート電圧はチップ パッケージ上のグランドを基準としているため、これが問題となります。回路がゲート トリガ スレッショルド付近で発振すると、入力電圧がゲートを開いたままにしておくのに十分でなくなったり、ゲートを複数回開いたりする可能性があります。

回路が再び切り替わると、同様の一連の条件によって ΔVA の両端に電位が上昇し、MOSFET A のソースの電圧がトリガしきい値以下に低下します。

#3. グラウンドバウンスが悪いのはなぜですか?

入力の状態が変化すると、出力と MOS チューブは中間の定義された状態ではなくなります。その結果、誤った切り替えまたは二重切り替えが発生する可能性があります。また、同じ GND および Vss 接続を共有する IC チップ上の他のセクターも、スイッチング時間の影響を受けます。

しかし、グランドバウンスの影響は IC チップに限定されません。ΔVB が MOS トランジスタのソース電位を 0V より高くするのと同様に、回路の GND 電位も 0V より低くします。地面のバウンスを描いた画像の多くは、外部の影響を示しています。

複数のゲートが同時に切り替えられると、その影響はより複雑になり、回路が完全に破壊される可能性があります。以下の例でバウンスを確認できます。下の画像は、重要な GND および Vss バウンスが接続され、アクティブ化されていることを示しています。

ここで、スイッチング中に 3.3V ラインに約 1V のノイズが発生します。これは信号ライン内で大きく共振し続け、最終的にバックグラウンド ライン ノイズに陥ります。

騒音はドアの開閉時だけではありません。スイッチ ゲートは IC の電源ピンに接続されますが、PCB は通常、共通の電源レールとグランド レールを共有します。これは、チップ上の Vss およびグランドへの直接電気接続から PCB 上のトレースへの結合を通じて、ノイズが回路内の他の場所に容易に伝達される可能性があることを意味します。 上の画像では、チャンネル 2 (シアン) は、減衰されていない信号ラインでのグランドと Vss のバウンスを示しています。これは非常に激しいため、チャンネル 1 (黄色のライン) の別の信号ラインに引き継がれます。

上の画像では、チャンネル 2 (シアン) は、減衰されていない信号ラインでのグランドと Vss のバウンスを示しています。これは非常に激しいため、チャンネル 1 (黄色のライン) の別の信号ラインに引き継がれます。

#4. 地面の跳ね返りを軽減する方法

1. デカップリング コンデンサ 1 を使用してグランド バウンスを特定します。

グランドバウンスを低減するための推奨ソリューションは、各電源レールとグランドの間に、IC のできるだけ近くに SMD デカップリング コンデンサを取り付けることです。遠くにあるデカップリング コンデンサは、インダクタンスを増加させる長い配線を備えているため、IC から遠く離れた場所に取り付けること自体には何のメリットもありません。IC チップ上のトランジスタの状態が切り替わると、チップ上のトランジスタの電位とローカル電源レールが変化します。

デカップリング コンデンサは、一時的に低インピーダンスの安定した電位を IC に提供し、バウンスの影響を制限し、回路の他の部分にバウンスが広がるのを防ぎます。コンデンサを IC の近くに置くことで、PCB トレース内の誘導ループ領域を最小限に抑え、干渉を減らすことができます。

ミックスドシグナル IC には通常、個別のアナログ電源ピンとデジタル電源ピンがあり、各電源入力ピンにデカップリング コンデンサを取り付けることができます。コンデンサは、IC と PCB 上の関連する電源プレーンに接続された複数のビアの間に配置する必要があります。 デカップリング コンデンサはビアを介して電源プレーンに接続する必要があります。

デカップリング コンデンサはビアを介して電源プレーンに接続する必要があります。

複数のビアが推奨されますが、PCB サイズの要件により不可能なことがよくあります。可能であれば、銅の流し込みまたはティアドロップを使用してビアを接続します。ドリルビットが中心からわずかにずれている場合は、余分な銅がビアをトレースに接続するのに役立ちます。 IC (U1) および 4 つのコンデンサ (C1、C2、C3、C4) 用の銅パッド

IC (U1) および 4 つのコンデンサ (C1、C2、C3、C4) 用の銅パッド

C1 と C2 は、高周波干渉用のデカップリング コンデンサです。データシートの推奨に従って C3 と C4 を回路に追加します。他のプレーンの制約により、ビアの配置は理想的ではありません。

場合によっては、IC の近くにデカップリング コンデンサを配置することが物理的に不可能な場合があります。ただし、IC から遠く離れた場所に配置すると、誘導ループが形成され、グランド バウンスの問題がさらに悪化します。

その場合、デカップリング コンデンサは、IC の下の PCB の反対側に配置できます。それがうまくいかない場合は、隣接する層の銅を使用して基板内に独自のコンデンサを作成することができます (このようなコンデンサは、埋め込み平面コンデンサと呼ばれます)。PCB は非常に小さな誘電体層で分離された平行な銅の流し込みで構成されているためです。このタイプのコンデンサの追加の利点の 1 つは、コストがかかるのは時間だけであることです。

2. 抵抗を使用して電流を制限する

IC に過剰な電流が流入、流出するのを防ぐために、電流制限抵抗を直列に接続してください。これにより、消費電力が削減され、デバイスの過熱が防止されるだけでなく、出力ラインから MOS チューブを通って Vss および GND に流れる電流が制限され、グランド バウンスが低減されます。

3. 配線を使用してインダクタンスを低減する

可能であれば、隣接するトレースおよび隣接する層上のリターン パスを維持します。基板上の層 1 と層 3 の間の距離は、通常、距離の数倍の厚いコア材料が存在するため、層 1 と層 2 の間にあります。信号パスとリターンパスを不必要に分離すると、その信号ラインのインダクタンスが増加し、その後のグランドバウンス効果が生じます。

下の図で PCB レイアウトを確認できます。 アナログとデジタルのアースはそれぞれ白と黄色で強調表示されます

アナログとデジタルのアースはそれぞれ白と黄色で強調表示されます

このボードには個別のアナログとデジタルのグランド リターン ピンがあり、PCB のレイアウトは、IC のデジタル グランド ピンとヘッダー ストリップ上のグランド ピンの間に明確で直接的なパスがなく、それらを分離する効果を打ち消しています。

信号は IC の迂回経路を通ってヘッダー ピンまで伝わり、グランド ピンを通って迂回経路に戻ります。

4. プログラミングと設計を考慮して地面のバウンスを低減する

スイッチの数が増えると、グランド バウンス干渉も増加するため、可能であれば、短い遅延オフセットを備えたスイッチ ドアを使用してください。

たとえば、デザインではさまざまな LED をさまざまな間隔 (1 秒、2 秒、3 秒など) で点滅させて、デザインのステータスを示すことができます。グランド バウンス効果は、3 つの LED すべてが同時にスイッチングしているときに回路に最も大きな影響を与えます。

この例では、LED をわずかにオフセットして完全に同期しないようにすることで、グランド バウンスの影響を軽減できます。LED 間の 1 ms の低さの導入はユーザーには知覚できませんが、グランド バウンス効果は約 3 分の 1 に減少します。

5. その他の PCB レイアウト設計原則

-

可能な場合は、設計上許容されるパッド内ビアを使用してください。

-

信号のリターンパスの距離を短縮します。距離が短いほど寄生容量が減少します。これを実現するには、コンポーネントを接地点の真上に配置するのが最善です。

-

ソケットやコードストリップは使用しないでください

-

グランド接続用のグランド ビアやトレースを共有しないでください。グランドプレーンに接続するには、別のビアとトレースを使用することをお勧めします。

-

コンデンサを出力に直接接続しないでください。

-

/0 標準として低電圧差動信号 (LVDS) を実装し、高帯域幅と高いノイズ耐性を提供します。

-

直列インダクタンスを減らすために短いリードのパッケージを選択し、BGA の使用も推奨します。

-

固体グランドプレーンを使用してIR損失とインダクタンスを低減し、グランド分割プレーンを回避します。

-

設計が許せば、より低いスイッチング素子を使用してみてください

4. プリント基板のはんだ付け不良の原因

回路基板の穴のはんだ付け性ははんだ付けの品質に影響します

回路基板の穴のはんだ付け性が低いと、仮想的なはんだ付け欠陥が発生し、回路内のコンポーネントのパラメータに影響を与え、多層基板のコンポーネントと内層の配線間の導通が不安定になり、回路全体の機能障害を引き起こします。

いわゆるはんだ付け性とは、溶融したはんだによって濡れた金属表面の特性、つまり、はんだが位置する金属表面が比較的均一で連続した滑らかな接着膜を形成する特性です。プリント基板のはんだ付け性に影響を与える主な要因は次のとおりです。

-

はんだの成分と性質

はんだは溶接化学処理プロセスの重要な部分であり、フラックスを含む化学材料で構成されており、一般的に使用される低融点共晶金属は Sn-Pb または Sn-Pb-Ag です。不純物によって生成される酸化物がフラックスに溶解しないように、不純物の含有量を一定の比率に制御する必要があります。フラックスの機能は、熱を伝えて錆を除去することによって、はんだがはんだ付けされた基板の回路表面を湿らせるのを助けることです。一般に、ガルバナムおよびイソプロピル アルコール溶媒が使用されます。

-

溶接温度と金属板表面の清浄度

溶接温度と板金表面の清浄度もはんだ付け性に影響します。温度が高すぎると、はんだの拡散速度が速まり、このとき活性が高いため、基板や溶融はんだ表面が急速に酸化し、溶接不良の原因となります。また、はんだ付け性に影響を与え、はんだビーズ、はんだボール、断線、光沢不良などの欠陥を引き起こします。

反りによる溶接欠陥

溶接工程中に基板や部品が反り、応力変形により仮想半田付けやショートなどの不良が発生します。反りは、基板の上部と下部の温度の不均衡によって発生することがよくあります。大型の基板の場合、落下する基板の重量により反りも発生します。

通常のPBGAデバイスはプリント基板から0.5mm程度の距離にありますが、基板上のデバイスが大きくなると、冷却後に基板が元の形状に戻る際に、はんだ接合部に長時間ストレスがかかることになります。デバイスは 0.1 mm 持ち上げられますが、溶接が切れるのに十分です。

回路基板の設計は溶接品質に影響します

レイアウト面では、基板サイズが大きくなりすぎると、溶接の管理は容易になりますが、プリント配線が長くなり、インピーダンスが増加し、耐ノイズ性が低下し、コストが増加します。サイズが小さすぎると放熱性が低下し、溶接の制御が難しくなり、隣接するラインが発生しやすくなります、回路基板の電磁干渉などの相互干渉が発生します。したがって、PCB ボードの設計を最適化する必要があります。

-

高周波コンポーネント間の接続を短縮し、EMI 干渉を軽減します。

-

重量のある部品(20g以上など)はブラケットで固定し溶接してください。

-

コンポーネント表面の大きな ΔT による欠陥や再加工を防ぐために、コンポーネントを加熱する場合は放熱の問題を考慮する必要があり、熱に敏感なコンポーネントは熱源から遠ざける必要があります。

-

部品はできるだけ平行に配置する必要があり、美しいだけでなく溶接もしやすく、量産に適しています。回路基板は 4:3 の長方形として設計するのが最適です。配線の断線を避けるため、配線幅を急激に変更しないでください。回路基板を長時間加熱すると銅箔が膨張し剥がれやすくなるため、銅箔の面積を大きくとる使用は避けてください。

以上のことから、PCB 基板の全体的な品質を確保するには、生産工程において、優れたはんだを使用し、PCB 基板のはんだ付け性を向上させ、反りや欠陥を防ぐ必要があります。