Diseño de circuito DDR

Introducción a DMC

DMC incluye el controlador de protocolo DDR (PCTL) y DDRPHY, que son soluciones completas de interfaz de memoria para subsistemas de memoria DDR.

La interfaz del controlador RV11XX DDR admite la interfaz estándar JEDEC SDRAM. El controlador tiene las siguientes características:

- Admite DDR3/DDR3L/DDR4/LPDDR3/LPDDR4 y otros estándares;

- Admite hasta 2 RANK, con una capacidad máxima de 4 GB;

- Admite ancho de bus de datos DDR de 32 y 16 bits;

- Modos de bajo consumo como Power Down y SDRAM self-refresh;

Topología DDR y métodos de conexión.

Para que PCBlayout sea conveniente, se utilizan diferentes secuencias de líneas al diseñar diferentes tipos de partículas DDR con diferentes anchos de bits. Consulte el "RV1126_RV1109_Template" publicado y consulte la secuencia de líneas y el diseño de la plantilla.

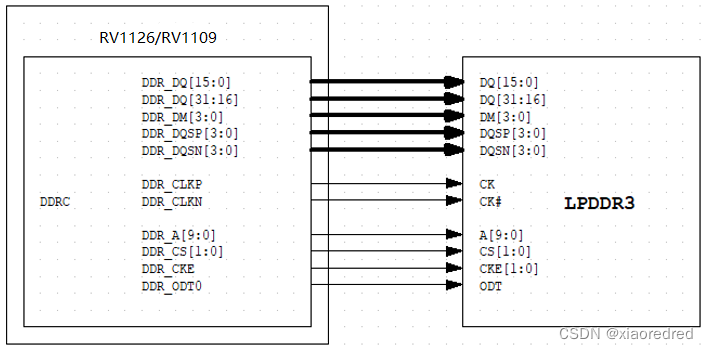

Figura 2–1 Diagrama de conexión de topología LPDDR3

Sugerencias de diseño a juego:

- Señales bidireccionales DQ y DQS: las señales DQ y DQS_P/N en aplicaciones RV11XX tienen topología punto a punto y se pueden conectar directamente.

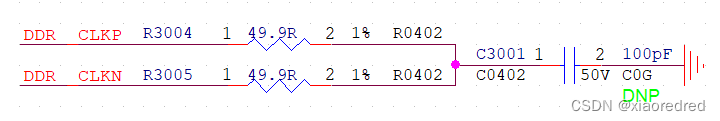

- Reloj diferencial: abarca dos resistencias de 49,9 ohmios cerca de los extremos del grano.

Figura 2–2 Resistencia de la serie DDR_CLK

- Señales de dirección y comandos: por ejemplo, al diseñar dos partículas DDR de 16 bits, las direcciones y comandos de la topología tipo T se pueden conectar directamente. Las señales de dirección y comando de la topología de paso a veces se conectan en serie con resistencias. Los valores de resistencia de las resistencias varían según la simulación y los datos medidos. La actual plantilla de vuelo DDR3 de placa de 4 capas tiene una resistencia de 49,9 ohmios.

- La resistencia externa ZQ se selecciona como 240 ohmios con una precisión del 1%.

fuente de alimentación DDR

Fuente de alimentación del controlador RV11XX DDR:

- DDR_VDD_1/2/3/4/5/6/7 requiere fuente de alimentación externa.

- DDR_VREF puede suministrar energía al VREF de partículas DDR, pero tenga en cuenta que el suministro de energía del pin DDR_VREF se cortará cuando el sistema esté en espera.

- Las partículas SDRAM incluyen dos conjuntos de fuentes de alimentación. Consulte varios estándares JEDEC para conocer la secuencia de encendido:

- La secuencia de encendido de DDR3 SDRAM se muestra en la siguiente figura:

Aplique energía (se recomienda que ESET# se mantenga por debajo de 0,2 * VDD; todas las demás entradas pueden no estar definidas). RESET# necesita mantener un nivel estable durante al menos 200us. Antes de que RESET# libere el nivel bajo (tiempo mínimo 10 ns), CKE se baja en cualquier momento. El tiempo de subida de la tensión de alimentación entre 300 mv y la tensión mínima de VDD no será superior a 200 ms; durante la etapa de subida de potencia, VDD > VDDQ y (VDD-VDDQ) < 0,3 V.

* VDD y VDDQ salen y son controlados por un único convertidor de potencia;

* Los niveles de voltaje en todos los pines excepto VDD, VDDQ, VSS y VSSQ deben ser ≤ VDDQ y VDD en un lado, y ≥ VSSQ y VSS en el otro lado. Además, una vez que se completa el aumento de potencia, el límite máximo de VTT es 0,95 V;

Vref rastrea VDDQ/2.

O

* El VDD, que se alimenta antes que el VDDQ o al mismo tiempo que el VDDQ, no debe tener ninguna inversión de pendiente.

* No debe haber inversión de pendiente con VDDQ alimentado antes o simultáneamente con VTT y Vref.

*Los niveles de voltaje en todos los pines excepto VDD, VDDQ, VSS y VSSQ deben ser ≤ VDDQ y VDD en un lado, y ≥ VSSO y VSS en el otro lado.

-

La secuencia de encendido de LPDDR3 SDRAM se muestra en la siguiente tabla:

| después | Condiciones que se aplican |

| el ha alcanzado | VDD1 debe>VDD2 - 200mV |

| VDD1 y VDD2 deben ser > VDDCA - 200 mV |

|

| VDD1 y VDD2 deben ser > VDDQ - 200 mV | |

| VRef siempre debe < todos los demás voltajes de suministro |

-

La secuencia de encendido de DDR4 SDRAM es la siguiente:

Aplique energía (se recomienda mantener RESET_n por debajo de 0,2 * VDD; todas las demás entradas pueden no estar definidas). Cuando la fuente de alimentación es estable, RESET_n debe mantenerse durante al menos 200us. Antes de que RESET_n libere el nivel bajo, CKE pasa a "Bajo" en cualquier momento (al menos 10 n veces). El tiempo de subida de la tensión de alimentación entre 300mV y Vpp min no será > 200ms; durante el período de subida, VDD ≥ VDDQ y (VDD-VDDQ) < 0,3V. La VPP debe aumentar al mismo tiempo que la VDD o antes, la VPP siempre debe ser ≥ VDD.

* VDD y VDDQ salen y son controlados por un único convertidor de potencia.

* El voltaje en todos los pines excepto VDD, VDDQ, VSS, VSSQ debe ser ≤ VDDQ y VDD en un lado y ≥ VSSQ y VSS en el otro lado. Además, VTT se limita a TBDVmax una vez que se completa el aumento de voltaje;

* VrefCA rastrea TBD.

O

* Cuando el VDD se aplica antes del VDDQ o al mismo tiempo que el VDDQ, no debe haber ninguna inversión ascendente;

* No debe haber ninguna inversión ascendente cuando VDDQ se aplica antes de VTT y VrefCA o al mismo tiempo que VTT y VrefCA;

* Cuando el VPP se aplica antes del VDD o al mismo tiempo que el VDD, no debe haber ninguna inversión ascendente;

* Los niveles de voltaje en todos los pines excepto VDD, VDDQ, VSS, VSSQ deben ser ≤ VDDQ y VDD por un lado y ≥ VSSQ y VSS por otro lado.

- La secuencia de encendido de LPDDR4 SDRAM es la siguiente:

Encienda el dispositivo LPDDR4 en la siguiente secuencia. Estos pasos son obligatorios a menos que se indique lo contrario. Tenga en cuenta que la secuencia de encendido de todos los canales debe realizarse simultáneamente.

Al encender (después de Ta), se recomienda establecer RESET_n en nivel bajo ( ≤ 0,2 x VDD2) y todas las demás entradas deben estar entre VILmin y VIHmax. La salida del dispositivo permanece en High-Z mientras que RESET_n permanece en LOW. Los requisitos de aumento de voltaje de la fuente de alimentación se muestran en la Tabla 4. VDD1 debe aumentar al mismo tiempo que VDD2 o antes. VDD2 debe aumentar al mismo tiempo o antes que VDDQ.

Tabla 2-2 Condiciones de rampa de voltaje

| después | Condiciones aplicables |

| después de ta | VDD1 debe ser mayor que VDD2 |

| VDD2 debe ser mayor que VDDQ -200mV |

Observación:

1. Ta es el punto en el que cualquier fuente de alimentación alcanza los 300 mV por primera vez.

2. Las condiciones de aumento de voltaje en la Tabla 3 se aplican entre Ta y el corte de energía (controlado o no controlado)

3. Tb es el punto en el que todos los voltajes de suministro y los voltajes de referencia están dentro de sus rangos especificados.

4. La duración del aumento de tensión tINIT0 (Tb-Ta) no excederá los 20 ms.

5. La diferencia de voltaje entre los pines Vss y Vssq no debe exceder los 100 mV.

Lista de modelos compatibles con DDR

La frecuencia operativa máxima de la interfaz DDR RV11XX se admite hasta 1056 MHz. Para obtener la lista de soporte de partículas DDR, consulte el documento "Lista de soporte DDR RK". Este documento se puede descargar en la plataforma redmine de nuestra empresa:

https://redmine.rockchip.com.cn/projects/fae/documents?tdsourcetag=s_pctim_aiomsg

Tome K4A8G165WC-BCTD como ejemplo

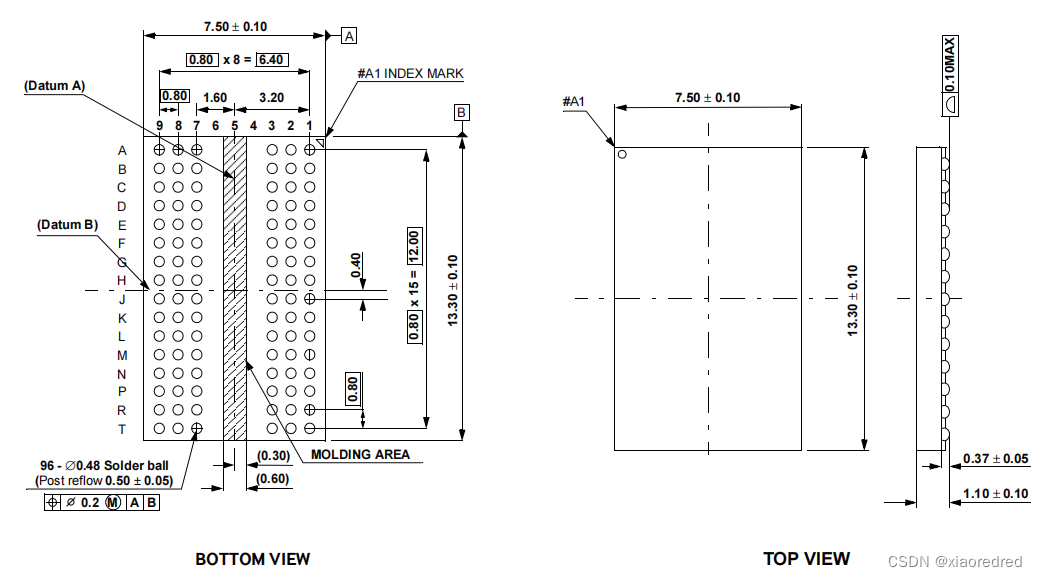

K4A8G165WC-BCTD es el chip de memoria DDR4 2G de Samsung, con una frecuencia de 2666 MHz y empaquetado en 96 FBGA.

pin DDR

| DDR4--K4A8G165WC-BCTD | |||

| definición | Número de pines | Función descriptiva | rango de voltaje |

| Un[0:16] | dieciséis | DIRECCIÓN | |

| AP | / | Precarga automática: muestreado durante un comando de lectura/escritura para determinar si se debe realizar una carga automática en el banco al que se accede después de la operación de lectura/escritura. (Alto: carga automática; bajo: sin carga automática). Muestre 10 durante el comando de precarga para determinar si la precarga se aplica a un banco (A10 LOW) o a todos los bancos (A10 HIGH). Si solo es necesario precargar un banco, seleccione el banco por dirección bancaria. Ocupa A10 | |

| Bc_n | / | Recorte de ráfaga: durante los comandos de lectura y escritura, se muestrea BC_n para determinar si se realizará el recorte de ráfaga (en tiempo real). (Alto: sin ráfaga, bajo: ráfaga). Ocupa A12 | |

| NOSOTROS_n | / | Habilitación de escritura: ocupa A14 | |

| CAS_n | / | Letra de selección de columna: Ocupa A15 | |

| RAS_n | / | Señal de selección de fila: ocupar A16 | |

| DQU[0:7], DQL[0:7] |

dieciséis | Entrada y salida de datos: bus de datos bidireccional. Si la función CRC está habilitada en el registro de modo, se agregará un código CRC al final de la ráfaga de datos. | |

| DMU, DML |

2 | Máscara de datos de entrada: la señal DM_n se utiliza como señal de máscara para escribir datos. Cuando la señal DM_n tiene un nivel bajo, el bit correspondiente a los datos de entrada del comando de escritura se descartará. DM_n se muestrea en ambos bordes de la tira de DQS. | |

| DQSU_P,DQSU_N; DQSL_P,DQSL_N |

4 | Señal estroboscópica de datos diferencial: un par de señales diferenciales, que es válida al mismo tiempo para escribir datos cuando se usa como entrada y válida al mismo tiempo para leer datos cuando se usa como salida. Los datos leídos están alineados con los bordes, pero el borde está centrado en los datos escritos. DDR4 SDRAM solo admite la señal estroboscópica como señal diferencial y no admite la señal estroboscópica de datos de una sola señal. | |

| BA0, BA1 | 2 | Entrada de dirección del banco: BA0 - BA1 define el banco al que se aplican los comandos activos, de lectura, de escritura o de precarga. La dirección del banco también determina a qué registro de modo se accede durante el ciclo MRS. | |

| BG0,BG1 | 2 | Entrada de grupo BANCO: Define a qué banco se aplica el comando de activación, lectura, escritura o precarga. BG0 también determina a qué modo de registro se accederá durante el ciclo MRS. | |

| CK_P, CK_N |

2 | Entrada de reloj diferencial. Todas las señales de dirección y control se muestrean a través del flanco ascendente de CK_t y el flanco descendente de CK_c | |

| CKF | 1 | 时钟使能:CKE为高电平时,启动内部时钟信号、设备输入缓冲以及输出驱动单元。CKE低电平时则关闭上述单元。当CKE为低电平时,可使设备进入PRECHARGE POWER DOWN、SELF-REFRESH以及ACTIVE POWER DOWN模式。CKE与SELF REFRESH退出命令是同步的。在上电以及初始化序列过程中,VREFCA与VREF将变得稳定,并且在后续所有的操作过程中都要保持稳定,包括SELF REFRESH过程中。CKE必须在读写操作中保持稳定的高电平。在POWER DOWN过程中,除CK_t,CK_c,ODT以及CKE以外的所有输入缓冲都是关闭的。在SELF REFRESH过程中,除CKE以外的所有输入缓冲都是关闭的。在正时钟上升边沿采样。 | |

| CS_n | 1 | 片选信号:当CS_n锁存为高电平时,所有的命令都被忽略。在正时钟上升边沿采样。 | |

| ODT | 1 | 从DDR2 SDRAM时代开始新增的功能。其允许用户通过读写MR1寄存器,来控制DDR3 SDRAM中内部的终端电阻的连接或者断开 | |

| ACT_n | 1 | 激活命令输入: ACT_n定义了与CS_n一起输入的激活命令。进入RAS_n/A16、CAS_n/A15和WE_n/A14的输入将被视为行地址A16、A15和A14 | |

| RESET_n | 1 | 活动低异步复位:当RESET_n低时复位处于活动状态,当RESET_n高时处于非活动状态。在正常运行时,RESET_n必须值较高。RESET_n是一种CMOS轨道到轨道的信号,直流电的高低分别为VDD的80%和20%, | |

| ALERT_n | 1 | 警报:具有CRC错误标志、命令和地址奇偶校验错误标志等多个功能。如果CRC有错误,则Alert_n的时间间隔变低,返回到高。如果命令地址奇偶校验有错误,则Alert_n会下降较长时间,直到进行DRAM内部恢复事务完成。在连接性测试模式下,该引脚可作为输入端工作。是否使用这个信号取决于系统。如果没有作为信号连接,ALERT_n销必须绑定到VDD上 | |

| PAR |

1 | 命令和地址奇偶输入: DDR4支持DRAM奇偶校验设置。一旦通过MR5中的寄存器启用,DRAM将使用ACT_n、RAS_n/A16、CAS_n/A15、WE_n/A14、BG0-BG1、BA0-BA1、A17-A0和C0-C2(3DS设备)计算奇偶校验。输入奇偶校验应保持在时钟的上升边缘,同时与CS_n LOW | |

| TEN | 1 | 连接测试模式启用:X16设备上需要,x4/x8上需要可选输入,密度等于或大于8Gb。这个引脚的高将使连接测试模式与其他引脚一起运行。它是一个CMOS轨道到铁路信号,交流高和低在80%和20%的VDD。是否使用此信号取决于系统。这个销可能是DRAM内部拉低通过一个弱下拉电阻到VSS。 | |

| CA_n | 1 | 命令/地址输入信号。可作为地址线使用,也可作为命令代码使用,是命令代码的一部分。 | |

| VDD | 10 | Core供电:1.2V +/- 0.06V | |

| VSS | 7 | Core地 | |

| VDDQ | 10 | I/O供电:1.2V +/- 0.06V | |

| VSSQ | 10 | I/O地 | |

| VDDCA | CA供电 | ||

| VSSCA | CA地 | ||

| VPP | 2 | DRAM激活供电:2.5V(最小2.375V,最大2.75V) | |

| VREF | 1 | 参考电压 | |

| ZQ | 驱动强度校准参考电阻 | ||

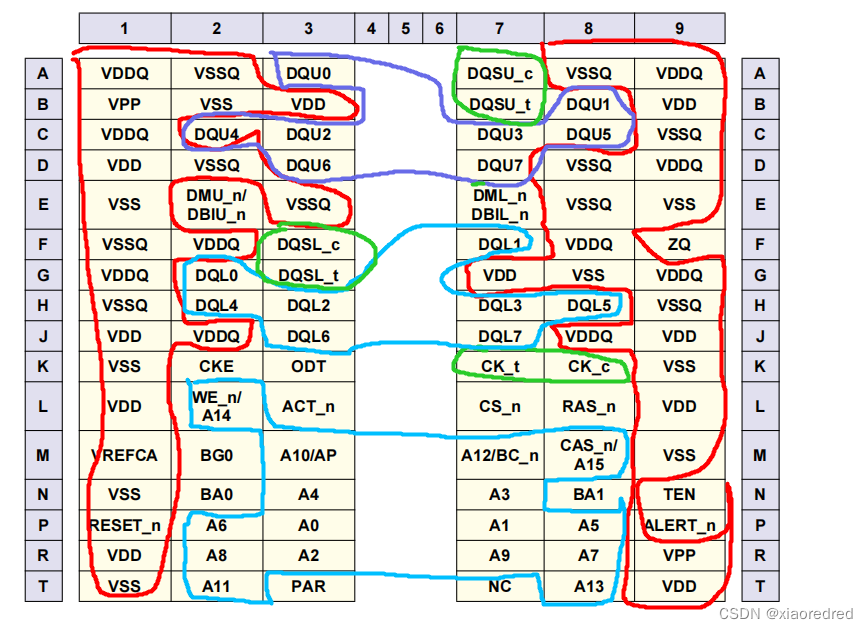

芯片引脚大概布局:

DDR PCB设计

DDR信号设计要求如下:

可以请参考官方的《RV1126_RV1109_Template》

表2-3 DDR3/DDR4/LPDDR4布局要求

| 参数 | 要求 | 备注 |

| 单端阻抗 |

50 Ohm ± 10% |

同一组控制线或同一组数据线间的走线间距应大于走线宽度1.5倍(最好2倍以上),而不同组间的信号线间距应大于走线宽度的2倍(最好3倍以上)。 |

| 差分阻抗 | 100 Ohm ± 10% |

等差分信号线应尽量设计成紧耦合差分对,即差分对内间距应小于走线宽度。走线应对称,如同时改变线宽,同时打过孔等。对于时钟差分信号线,如有两个负载,则各分支线长度应尽量短且对称,每条分支线末端用 200 2 电阻进行并联端接。 |

| DQ与DQS长度差(同组内) | ≤ 30mil | |

| DM与DQS长度差(同组内) | ≤ 30mil | |

| (命令/地址)与CLK长度差 | ≤ 60mil | |

| DQS_P与DQS_N长度差(同组内) | ≤ 12mil | |

| CLK_P 与 CLK_N 长度差 |

≤ 12mil | |

| DQS 与 CLK 长度差 | ≤ 900mil | |

| 不同组间距 | ≥ 2倍走线宽度 | |

| DQ到DQ间距(同组内) | ≥ 2倍走线宽度 | |

| DQ到DQS间距(同组内) | 建议 ≥ 3倍走线宽度 至少是走线宽度的2倍 |

|

| (命令/地址)到(命令/地址)的间距 | ≥ 2倍走线宽度 | |

| CLK到其他线的间距 | 建议 ≥ 3倍走线宽度 至少是走线宽度的2倍 |

|

| DQS最大对内偏差 | 1pS | |

| DQ和DQS之间的最大偏差 | 5pS | |

| BGA扇出 | 信号类 | 在扇出线区域,由于空间限制,不能满足走线宽度和间距要求时,可适当减小走线宽度及减小走线间距,但该扇出线长度应小于500mil。 |

表2-4 LPDDR3布局要求

| 参数 | 要求 |

| 单端阻抗 |

50 Ohm ± 10% |

| 差分阻抗 | 100 Ohm ± 10% |

| DQ与DQS长度差(同组内) | ≤ 30mil |

| DM与DQS长度差(同组内) | ≤ 30mil |

| (命令/地址)与CLK长度差 | ≤ 30mil |

| DQS_P与DQS_N长度差(同组内) | ≤ 12mil |

| CLK_P 与 CLK_N 长度差 |

≤ 12mil |

| DQS 与 CLK 长度差 | ≤ 900mil |

| 不同组间距 | ≥ 2倍走线宽度 |

| DQ到DQ间距(同组内) | ≥ 2倍走线宽度 |

| DQ到DQS间距(同组内) | 建议 ≥ 3倍走线宽度 至少是走线宽度的2倍 |

| (命令/地址)到(命令/地址)的间距 | ≥ 2倍走线宽度 |

| CLK到其他线的间距 | 建议 ≥ 3倍走线宽度 至少是走线宽度的2倍 |

备注:

1. DQS:数据选通,为双向数据,当需要对DDR进行写入时,发送端为主控,接收端为DDR,中心与写入的数据DQ中心对齐,当需要对DDR进行数据的读出时,发送端为DDR,接受端为主控,中心与数据DQ边缘对齐(Bi-directional Data Strobe双向数据控制引脚)

2. DM:数据输入屏蔽,数据写入的时候,如果DM为高,将屏蔽写入,为输入信号,参考电平为VREFFCA;

3. DQ:数据线,对DDR的读写都是经过对DQ电平的写入,双向口,电平参考VREFFDQ;

4. Byte:原意为一个字节,就是8bit,内存中,8位为一组,Byte-to-byte 此处为一个组到另一个组。

数据组:

单端信号要求走50Ω±10%,差分信号走100Ω±10%,其中DQ、DM为单端信号,DQS为差分信号。

DQS差分信号:走线宽度及差分线间距由PCB的叠层阻抗所决定

DQ数据线:DQ的走线宽度由PCB的叠层阻抗决定,组内走线间距需要走2W原则(两走线中心点距离为2倍走线宽度)

DQS和DQ走线间距:走线需要大于等于2W

不同数据组之间的间距:走线需要大于等于2W

DQS差分对之间最大延迟:1PS(1PS的延迟在PCB上大概对应6mil,所以我们要求差分对之间的等长控制在5Mil就一定不会出错)

DQS与DQ的最大延迟:5PS(1PS的延迟在PCB上大概对应6mil,所以我们要求差分对之间的等长控制在30Mil以内)

因为CLK与DQS之间的最大延迟可以接受为150ps,也就是每个数据组之间只要做到750mil内等长即可,但普遍控制在120mil以内

数据信号组为8位为一个字节即为一组,但还需要包括DQS和DQM(DQ0-7,DQM,DQS)

第二组信号为DQ8-DQ15,DQM,DQS。

总体设计思路:

1.时序设计:LPDDR4的时序非常严格,需要设计符合时序要求的时钟、信号延迟和信号捕获等电路。在时钟设计方面,需要保证时钟的稳定性和准确性,以便能够正确地同步数据。在信号延迟和捕获设计方面,需要考虑信号传输的延迟,以及数据捕获时的噪声和时钟抖动等因素。

2.电源和地设计:由于LPDDR4的工作电压较低,一般为1.1V或1.2V,因此需要设计稳定的电源和地电路,以保证内存的正常工作。在电源设计方面,需要考虑电源噪声和电源共模干扰等问题,而在地设计方面,则需要注意接地的稳定性和接地回路的设计。

3.等长匹配设计:由于LPDDR4的时序要求非常严格,因此需要进行等长匹配设计,以保证信号在传输过程中的同步性。在等长匹配设计方面,需要考虑信号路径长度、信号捕获时间和时钟延迟等因素。

4.信号完整性设计:由于LPDDR4的工作频率较高,信号完整性对内存性能的影响非常大。因此需要进行信号完整性设计,包括信号阻抗匹配、信号引脚布局和信号层次布局等方面。

信号组布线顺序

为了确保DDR接口最优化,DDR 的布线应该按照如下的顺序进行。

- 第一:功率、电阻网络中的无源元件引脚交换,如地址线、数据线、控制线、时钟等数据线中的串行端接电阻及排阻,通过交换引脚可以让布线顺利。

- 第二:是VTT 电源平面的规划和布线、VREF 的规划和布线。

- 第三:是时钟布线。

- 第四:是数据组信号线的布线,数据信号组的布线优先级是所有信号组中量高的,因为它工作在2倍时钟频率下,它的信号完整性要求是最高的。另外,数据信号组是所有这些信号组中占线最多的部分,也是最主要的走线长度匹配有要求的信号组。

- 第五:是地址和命令信号布线,地址、命令、控制和数据信号组都与时钟的走线有关。因此,系统中有效的时钟走线长度应该满足多种关系。应该建立系统时序的综合考虑,以确保所有这些关系都能够被满足。

- 第六:是VDDQ 或者 VDD 电源的布线。

EMMC

eMMC的全称为“embedded Multi Media Card”,中文即: 嵌入式的多媒体存储卡。是由MMC协会所订立的、主要是针对手机或平板电脑等产品的内嵌式存储器标准规格。

eMMC的一个明显优势是在封装中集成了一个控制器,它提供标准接口并管理闪存,eMMC利用的是它将主控制器、闪存颗粒整合到了一个小的BGA封装内。

2015年前所有主流的智能手机和平板电脑都采用这种存储介质,多媒体存储卡在替代紧凑型闪存作为智能手机等移动设备的存储介质之后,就有新版本不断推出,速度也越来越快,eMMC 4.4的读取速度大约为104MB/s、eMMC 4.5则为200MB/s。而在2013年7月29日三星开始量产行业首款eMMC 5.0存储产品,其读取速度为400MB/s,而最新的eMMC 5.1规范来说,其理论带宽为600MB/s左右。

EMMC选型

RV11XX EMMC接口支持EMMC 4.51,并兼容4.41,控制器有如下特点:

- 与标准INAND接口兼容;

- 支持1-