Раздел 3 Структура модуля

3.1 Введение в модуль

Модуль (модуль) Verilog'sосновная единица описания, являются внешними портами, используемыми для описания функциональности или структуры проекта и связи с другими блоками .

Модуль может быть концептуально эквивалентен устройству, например, вызов общего устройства (логический элемент И, логический элемент с тремя состояниями и т. д.) или общего макроблока (счетчик, АЛУ, ЦП) и т. д. Следовательно, один модуль может вызываться в другом модуле, а схемотехника может состоять из нескольких модулей. Дизайн модуля — это только определенный уровень проектирования системы, и для проектирования модуля можно использовать различные методы моделирования.

Основной структурной единицей Verilog является «модуль». Модульный дизайн делает систему более организованной и облегчает моделирование и тестирование, поэтому идея дизайна всего проекта - модуль в модуле, который разворачивается последовательно сверху вниз. При разработке проекта каждый модуль реализует определенную функцию, причем модули могут быть вложены иерархически. При проектировании крупномасштабной цифровой схемы ее можно разделить на небольшие модули разных размеров, каждый небольшой модуль реализует определенную функцию, и, наконец, общая функция реализуется путем вызова подмодуля из модуля верхнего уровня. Дизайнерское мышление «сверху вниз» . Эта книга в основном основана на языке описания оборудования Verilog, а модуль является базовой единицей описания Verilog, которая используется для описания функций и структуры каждого проекта, а также внешнего интерфейса для связи с другими модулями.

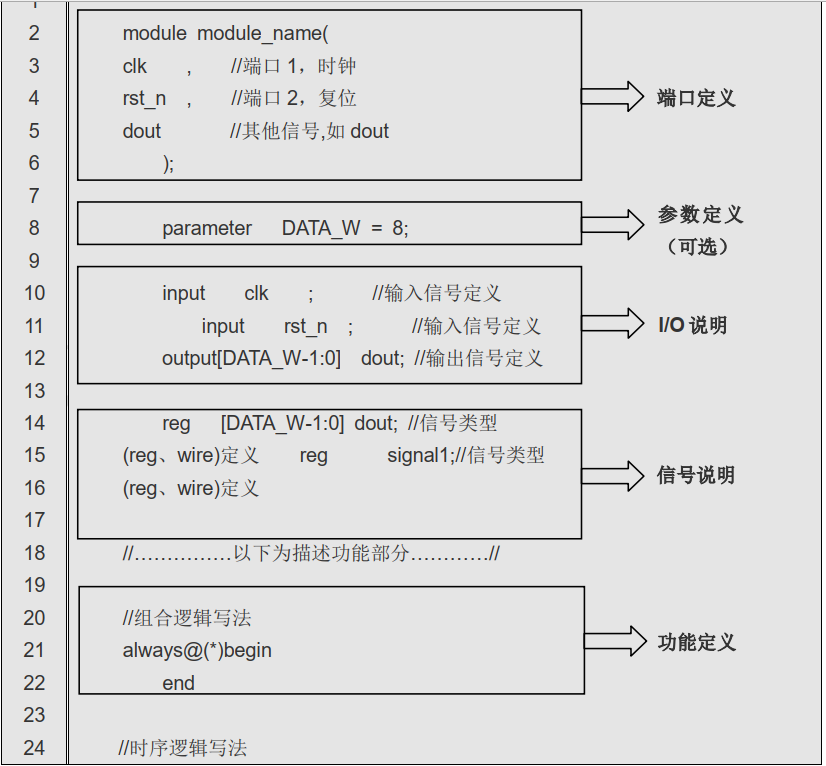

Модуль состоит из пяти основных частей: определение порта, определение параметра (необязательно), описание ввода/вывода, объявление внутреннего сигнала, определение функции .Модули всегда начинаются с ключевого слова module и заканчиваются ключевым словом endmodule.. Его общая грамматическая структура выглядит следующим образом:

3.2 Имя модуля и определение порта

Строки с 1 по 5 объявляют имя модуля и порты ввода и вывода. Его формат следующий: модуль имя модуля (порт 1, порт 2, порт 3, ...); где модуль начинается с модуля и заканчивается на endmodule. Имя модуля является уникальным идентификатором модуля . Обычно рекомендуется, чтобы имя модуля называлось именем, которое может описать его функцию, а имя модуля и имя файла совпадали.

Порт модуля представляет имена входных и выходных портов модуля, а также идентификацию его контактного порта с другими модулями .

3.3 Определение параметра

Определение параметра строки 8 заключается в замене констант символами для повышения удобочитаемости и модифицируемости кода. Это необязательный оператор, который можно опустить, если он не используется.Общий формат определения параметра следующий :

параметр DATA_W = х;

3.4 Определение интерфейса

Строки с 9 по 12 являются описаниями ввода/вывода (ввода/вывода), а порты модуля могут быть входными портами, выходными портами или двунаправленными портами . Формат описания следующий.

Входной порт : вход [разрядность сигнала-1: 0] имя порта 1;

input [разрядность сигнала-1: 0] имя порта 2;

……;

Выходной порт : выход [разрядность сигнала-1: 0] имя порта 1;

вывод [разрядность сигнала-1: 0] имя порта 2;

……;

Двунаправленный порт : inout [разрядность сигнала-1: 0] имя порта 1;

inout [разрядность сигнала-1:0] имя порта 2;

……;

3.5 Типы сигналов

Строки с 14 по 17 определяют тип сигнала. Эти сигналы являются сигналами, используемыми в модуле, и переменными типа провода и регистра, относящимися к порту ( т.е. тип проводной сети и тип регистра ). Он объявляется следующим образом:

reg [width-1:0] R переменная 1, R переменная 2 ...;

провод [ширина-1: 0] W переменная 1, W переменная 2...;

Если тип сигнала не определен,По умолчанию используется проводной тип., а разрядность сигнала равна 1 .

3.6 Функциональное описание

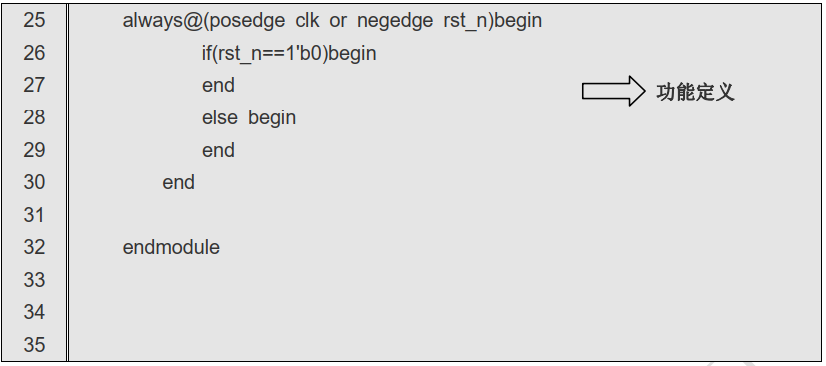

Строки с 21 по 31 являются частью описания функции. в модулеНаиболее важной частью является часть определения логической функции., есть три способа сгенерировать логику в модуле.

- Используйте оператор «assign», как описано

- Опишите вентиль И с двумя входами: присвойте a = b & c. Подробные сведения о функциях см. в разделе «Описание функций — логика комбинирования».

- Используйте блок «всегда». То есть последовательная логика и комбинационная логика, введенные ранее.

- Создание экземпляра модуля. Подробнее о функциях см. в разделе «Создание экземпляра модуля».

3.7 Создание экземпляра модуля

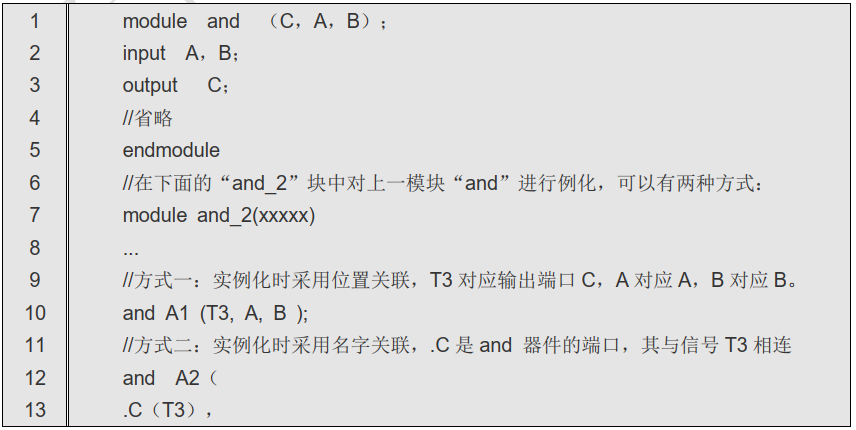

При проектировании цифровой системы обычно применяется нисходящий метод проектирования, который может разделить систему на несколько функциональных модулей, и каждый функциональный модуль далее делится на подмодули следующего уровня. Дизайн каждого модуля соответствует модулю, и каждый модуль разработан как программный файл Verilog HDL. Поэтому для модулей верхнего уровня системы принят структурированный дизайн, то есть модули верхнего уровня вызывают каждый функциональный модуль отдельно .

На модуль можно ссылаться внутри другого модуля, таким образом создавая иерархию описаний. Оператор инстанцирования модуля имеет следующую форму:

module_nameinstance_name(port_associations) ;

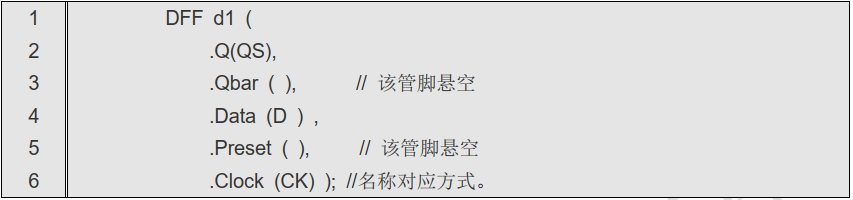

Сигнальные порты могут быть связаны по местоположению или имени, но методы ассоциации нельзя смешивать. Форма ассоциации портов выглядит следующим образом: port_expr // по положению. .

PortName (port_expr) // Имя прохода.

предположение: Пожалуйста, используйте ассоциацию имен в созданном сопоставлении портов , чтобы не было легко сделать ошибки при изменении контакта вызываемого модуля. В инстанцировании некоторые выводы могут не использоваться, а при отображении может использоваться пустая обработка, например:

Вход плавающего порта входного контакта имеет высокое сопротивление Z. Поскольку выходной контакт является плавающим, выходной контакт отбрасывается.。